Устройство для контроля блоков постоянной памяти

Иллюстрации

Показать всеРеферат

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к вычислительной технике и может быть использовано для конт роля запоминающих устройств..

Известно устройство для контроля постоянных блоков памяти, содержащее генератор, блок сравнения, эталонный блок памяти и блок индикацииИ .

Однако данное устройство характеризуется недостаточной надежностью контроля.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля постоянных блоков памяти, со- держащее генератор импульсов и блок сравнения, входы которого подключены соответственно к выходам эталонного блока памяти и входам устройства, а выход соединен с блоком индикации, а также элементы,2И-ИЛИ и счетчик, вход которого подключен к выхо. ду генератора импульсов. В известном устройстве с целью повышения надежности контроля > имитируется режим произвольного обращения к контролируемому постоянному блоку памяти, позволяющего выявить влияние помех, возникающих по одному адресу, на считанный сигнал по всем адресам блока памяти. При этом для каждого адреса блока памяти производится следующая последовательность обраще1 первое обращение по нулевому адресу; второе обращение по данному адресу; третье обращение по первому адресу; четвертое обращение по данному адресу;

2 х 2 — 2 обращение по данному адресу; и

2 х Р— 1 обращение по 2-ому адресу;

2 х 2 обращение по данному адресу, И (rye и — число разрядов адреса; N = 2 число адресов блока памяти). Общее число обращений к контролируемому блоку памяти равно С1 = 2N (2).

Недостаток известного устройства - невозможность выбора режима контроля в соответствии с конструктивными особенностями блоков памяти и входящих в их состав микросхем памяти и, вследствие этого, неоправданно большие затраты времени на проведение контроля.

Конструктивные особенности построения блоков памяти приводят к различной степени 902077 взаимовлияния обращений, производимых по различным адресам. В связи с этим при контроле нецелесообразно проверку взаимовлияния обращения по данному адресу и обращения по какому-либо адресу производить по всем адресам блока памяти, как это делается в известном устройстве, что позволит сократить время контроля.

Так, например, в полупроводниковых блоках памяти, состоящих из микросхем памяти, 1р проверку взаимовлияния обращений имеет смысл проводить лишь по адресам блока памяти, относящимся к одной микросхеме памяти. Действительно, в этом случае ячейки на.мети конструктивно расположены в одном кристалле и имеют паразитные связи существенно большие, чем ячейки памяти, расположенные в различных микросхемах памяти.

Ячейки ц, расположенные в одной микросхеме памяти, так же имеют различную сте пень паразитных связей. Например, ячейки памяти, составляющие столбец нли строку матрицы запоминающих элементов микросхемы памяти, связаны намного сильнее, чем ячейки памяти, относящиеся к разным столб@ам или строкам, так как имеют общие шины адреса кли же общие выходные разрядные шины. Этот факт в некоторых случаях так же позволяет сократить время контроля путем проверки взаимовлияний обращений, производимых JIHUlb к ячейкам памяти, составляющим строку или столбец матрицы запоминающих элементов микросхемы памяти.

Цель изобретения — повышение быстродействия устройства.

Йоставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее генератор импульсов, выход которого подключен ко входу первого счетчика, блок сравнения, одни входы которого подключены к выходам эталонного накопителя, а другие входы блока сравнения являются входами устройства, выходы блока сравнения являются управляющими выходами устройства, блок элементов 2И-ИЛИ, дополни. тельно введены нериый коммутатор, входы 45 которого подключены к выходам первого счетчика и к одним входам блока элементов

2И-ИЛИ, а управляющие входы первого коммутатора являются управляющими входами устройства, второй счетчик, вход которого подключен к выходу первого коммутатора, и второй коммутатор, одни входы которого подключены к выходам блока элементов

2И-ИЛИ, вторые входы — к выходам второго счетчика и к другим входам блока элементов

2И-ИЛИ, а управляющие входы второго коммутатора являются управляющими входами устройства, выходы второго коммутатора подКлючены ко входам эталонного накопителя н являются выходами устройства, управляющие выходы первого счетчика подключены к соответствующим входам блока элементов 2И-ИЛИ, вторые входы подключены к выходам второго счетчика, а выходы соединены со входами эталонного блока памяти и выходами устройства.

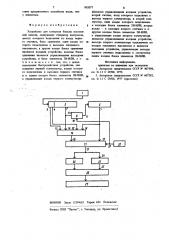

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит генератор 1 импульсов, первый счетчик 2, имеюцшй нулевой sIIход 3 н единичный выход 4 младшего разряда и выходы 5 остальных разрядов, второй счетчик 6 на h-разряд с выходами 7, первый коммутатор 8 со входами 9, управляющими входами 10 и выходами 11, блок 12 элементов 2И-ИЛИ, имеющий входы 13 — 16, второй коммутатор 17 с первыми 18, вторыми 19 н управляющими 20 входами и выходами.21, подключенными ко входам эталонного накопителя 22, накопитель 23 со входами 24 и выходами 25, блок 26 сравнения, блок 27 индикации и пульт 28 управления.

Второй коммутатор 17 содержит дешифратор, элементы НЕ, элементы И и элементы

ИЛИ (не указаны).

Предлагаемое устройство работает следующим образом.

Пусть проверяемый постоянный накопитель 23 конструктивно состоит из 2"" микросхем памяти. Тогда в и-разрядном коде адреса ячейки памяти накопителя 23 можно выделить m с IтаsрpIшIIиsх x рpаaзs1рIяsд оoвs, определяющих адрес микросхемы памяти, и n — m младших разрядов, определяющих адрес ячейки памяти внутри данной микросхемы памяти.

С целью сокращения времени контроля блока памяти выбирают режим проверки взаимовлияния обращений, производимых лишь к ячейкам памяти, расположенным в одной микросхеме. Для этого на пульте 28. у равления набирают код режима работы, равный в данном случае двоичному коду числ» п-е.

С выхода пульта 28. управления код поступает на управляющие входы 10 первого коммутатора 8 и управляющие входы 20 steato коммутатора 17. Йрн этом первый коммута. тор. 8 подключает к своему выходу 11 шину (fI-пт+1) -te разряда первого счеЯВа 2 н сигнал с Ноо поступает иа Вход второго счетчик» 6. С управляющих входов 20 второго коммутатора 17 код режима работы поступает на входы дешифратора коммутатора 17. На (n-e) -ом выходе дешифратора коммутатора

17 появляется еднни шый сигнал. Единичный сигнал с (n-м)-го выхода дешифратора коммутатора !7 поступает иа входы элеменню

ИЛИ коммутатора 17 и с выходов на вторые входы элементов И коммутатора, разрешая про. хождение на первые входы элементов ИЛИ.902077 коммутатора 17 сигналов и-m младших разрядов и-разрядного кода, поступающего на первые входы 18 второго коммутатора 17 с выходов блока 12 элементов 2И-ИЛИ. Нулевые сигналы с выходов элементов ИЛИ коммутатора !7 и нулевой сигнал с п-го выхода дешифратора коммутатора 17 поступают на входы элемента HE коммутатора 17, единичные сигналы с выходов которых поступают íà вторыа входы элементов И коммутатора 17,. раз- 1Е решая прохождение на вторью входы элементов ИЛИ коммтуатора 37 m старших разрядов и-разрядного кода, поступающего на вторые входы 19 второго коммутатора 17 с выходов 7 второго счетщка 6;

Итак, при выбранном режиме работы на выходах 21 второго коммутатора 17 формируется и-разрядный код, n m младших разрядов которого поступают с первых и-т выходов 18 блока !2 .элементов 2И-ИЛИ, а m старших разрядов — с выходов 7 m старших разрядов счетчика 6. 33 начальный момент времени первый 2 и второй б счетчики нахоцятся в нулевом состоянии. С выхода 3 первого счетчика 2 разрешающый сигнал поступает на вход !3 блока 12 злемен1тов 2И-ИЛИ, а запрещающий сигнал е выхо.да 4 — иа вход 35 блоаса !2 элементов 2И-ИЛИ. Сигналы с ваавдов 5 первого счетчика 2 поступают иа входы 34, а сигналы ЗЭ с выходов 7 второго счеткпв б иа входы 16 блока 12 элементов 2И-ИЛИ. При этом иа выходах 18 блока 12 элементов 2И-ИЛИ устанавливается и-разрядный код 00 ... 00, соответствующий выходам 5 первого счетчика 2,sg а на выходах 21 второго коммутатора 17 устанавливается и-разрядный код адреса 00 ...0.00 ... Π— нулевой адрес нулевой микросхемы памяти накопителя 23 (точкой отделены и — 1т3 младших разрядов от ITI clapslQsx) . ав

С обоих накопителей.22 и 23 производится считывание соответствуяицей этому адресу информации, которая с выхода каждого иэ sasx яоступает на соответствующие входы блока

26 сравнения, вырабатывающего прн различии сравниваемых данных выходной сигнал, поступающий на блок 27 индикации.

При идентичности считанной с обоих како. пителей 22 и 23 информации иа выходе блока 26 сравнения сигнал не вырабатывается, импульс е генератора l меняет состояние счетщка 2 на единицу и на выходе 4 нулевого разряда счетчика 2 устанавливается разрешающий сигнал. Прн этом на выходах 18 блока 12 элементов 2И-ИЛИ н на выходах

21 второго коммутатора 17 формируется и-разрядный код 00 ... 0.00 ... 0 — нулевой . адрес нулевой микросхемы памяти накопите. ля 23, соответствующий выходам 7 второго счетчика 6.

Вновь по этому адресу в накопителях

22 и 23 производится считывание информаcsssss и, в случае ее идентичности, следующий имщльс sesepampa l увели изает состояние первого счетчика 2 .ю еднняцу и иа выходе

3 его пулевого разов -устаиавнивается разреп3а@аВА assam П3ги siaas на выходах 38 .блока 32 франтов 2й-ИЛИ формируется

1п.разрядный scag 30..0, соответствутищий выходам 5 первого ачетчвиса 2, а на выходах 21 второго коммутато3га 17 — scag адреса 10... ...0.00...0 — первый адрес нулевой микросхемы накопителя 23. Вновь по этому адресу в накопитель 22 и 23 производится сжтываниа информации н, в случае ее идентнщости, изменяется состояние nepsoro счетчика 2 на еднащу. Прн этом на выходах 18 блока 12

2И-ИЛИ, а следовательно, и на выходах 23 второго коммутатора 17 устанавливается код адреса обращения 00...0.00...0 — нулевой адрес нулевой микросхемы памяти накопителя 23, соответствующий выходам 7 второго счетчика 6 и т.д. После обращения к накопителям

22 н 23 по адресам 11...1,00...0 — последнему адресу нулевой микросхемы памяти блока

23 и 00...0.00...0 — ее первому адресу импульс генератора l теперь уже изменяет на единицу состояния обоих счетчиков, так как сигнал переноса с выхода 5 (и-m+3)-го разряда первого счетчика 2 через первый коммутатор

8 поступает иа вход второго счетака б. 3 еперь ycspoficsso формирует последовательность адресов, при которой обращение по каждому из 21з тп адресов нулевой микросхемы памяти накопителя 23 производится после обращеssss по ее первому адресу, затем после обращения по ее второму адресу и t.ä. до ее последнего адреса 11...!.00...0, после чего иа выходах 7 второго счетчика 6 устанавливается код 00...0.!0...0 н устройство переходит к проверке первой MNKpocxeMbf памяти накопителя 23, для которой повторяется последовательность обращений как н при проверке его нулевой микросхемы.

Далее на выходах 7 второго счетчика 6 .устанавливается код 00...0.1...0 н такая же последовательносп . обращений повторяется для проверки второй микросхемы памяти накопителя 23 н т.д.

Общее число обращении «:г к проверяемому блоку памяти в предлагаемом устройстве

2 равно Сг = 2NssM (где Им 2и-м чпс ло адресов микросхем памяти, составляющих блок памяти, а М = 2 — число микросхем памяти в блоке. Следовательно, быстродей902077

ВНИИПИ Заказ 12394/62 Тираж 623 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная,4 ствие предлагаемого устройства выше, чем у известных.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее генератор импульсов, выход которого подключен ко входу первого счетчика, блок сравнения, одни входы которого подключены к выходам эталонного накопителя, а другие входы блока сравнения являются входами устройства, выходы блока сравнения являются управляющими выходами устройства, и блок элементов 2И-ИЛИ, о тл и ч а ю ш е е с я тем, что, с целью повышения быстродействия устройства, оно содержит первый коммутатор, входы которого подключены к выходам первого счетчика и к одним. входам блока элементов 2И-ИЛИ, а управляющие входы первого коммутатора являются управляющими входами устройства, второй счетчик, вход которого подключен к выходу первого коммутатора, и второй ком.мутатор, одни входы которого подключены к выходам блока элементов 2И-ИЛИ, вторые входы — к выходам второго счетчика и к другим входам блока элементов 2И-ИЛИ, а управляющие входы второго коммутатора являются управляющими входами устройства, . !

О выходы второго коммутатора подключены ко входам эталонного накопителя и являются выходами устройства, управляющие выходы первого счетчика подключены к соответствующим входам блока элементов 2И-ИЛИ, .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР И 407398, кл. G 11 С 29/00, 1975.

2. Авторское свидетельство СССР И 607282, кл. G 11 С 29/00, 1977 (прототип)