Устройство для управления автономным @ -фазным инвертором напряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИ4Е ТЕЛЬ СТВУ

Союз Советских

Социалистических

Республик

< >902201 (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.04.80 (21) 2918343/24-07 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Н 02 P 13/18

Гееударственнмй кемнтет

СССР (53) УДК 621.316..727 (088.8) Опубликовано 30.01.82. Бюллетень № 4

Дата опубликования описания 05.02.82 пв делам нзебретеннй и открытий (72) Автор изобретения

С. Г. Обухов (1 (71) Заявитель

Московский ордена Ленина энергетический кистину (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ АВТОНОМНЫМ

m-ФАЗНЫМ ИНВЕРТОРОМ НАПРЯЖЕНИЯ

Изобретение относится к электротехнике и предназначено для управления многофазными автономными инверторами напряжения с ШИМ.

Известно устройство для управления инверторами напряжения, основанное на выделении сигнала разностной частоты (1).

Недостатком этого устройства является то, что оно не обеспечивает хорошего гармонического состава выходного напряжения инвертора, регулировка величины выходного напряжения может быть осуществлена только по цепи питания, что ограничивает возможности применения подобных систем.

Наиболее близким по технической сущности к изобретению является устройство, основанное на вертикальном принципе управления. Устройство содержит источник тактовых импульсов, генератор линейно-изменяющегося напряжения (который может быть выполнен по схеме интегратора), компаратор и источник управляющего напряже.ния. Источник управляющего напряжения выполнен в виде трехфазного генератора прямоугольно-ступенчатого напряжения (2)

Недостатком этого устройства является невысокая точность работы.

Цель изобретения — повышение точности.

Поставленная цель достигается тем, что в устройство для управления m-фазным инвертором напряжения, содержащее тактовый генератор, связанный через интегратор .с компаратором, второй вход которого присоединен к источнику управляющего напряжения, введены два счетчика, генератор опорной частоты, m дешифраторов, m цифровых элементов сравнения, причем, выход компаратора связан с цепью сброса интегратора и входом первого .,счетчика, выход которого связан с первым входом всех цифровых элементов сравнения, генератор опорной частоты через второй счетчик и дешифраторы связан со вторыми входами цифровых элементов сравнения, а выход тактового генератора связан с цепью обнуления первого счетчика.

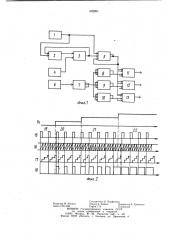

На фиг. 1 приведена структурная схема устройства при m = 3; на фиг. 2 — временные диаграммы.

Тактовый генератор 1 связан через интегратор 2 с компаратором 3, ко второму входу которого подключен источник 4 управляющего напряжения. К выходу компаратора

902201 подключен первый счетчик 5, а к выходу генератора 6 опорной частоты второй счетчик 7.

Выход второго счетчика 7 связан с дешифраторами 8, 9 и 10. Выходы дешифраторов и выход счетчика 5 связаны со входами цифровых элементов 11, 12 и 13 сравнения.

На временной диаграмме 14 приведен код на выходе дешифратора 8, на диаграмме 15 выходное напряжение на выходе тактового генератора !, на диаграмме 16 напряжение на выходе интегратора 2, на диаграмме 17 код на выходе первого счетчика 5, на диаграмме 18 импульсы выходного напряжения автономного инвертора.

Устройство работает следующим образом.

С приходом каждого импульса тактового генератора 1 интегратор 2 обнуляется, счетчик 5 также устанавливается в нулевое положение. Затем начинается интегрирование фиксированного напряжения. Когда напряженис на интеграторе достигает величины управляющего напряжения на выходе источника 4 срабатывает компаратор 3 и обнуляет интегратор 2, в счетчик 5 записывает-, ся единица. Интегратор вновь интегрирует фиксированное напряжение, при равенстве выходного напряжения на интеграторе и управляющего напряжения вновь срабатывает компаратор 3 и в счетчик 5 записывается следующее число. И так далее процессы повторяются до тех пор, пока число в счетчике не достигает некоторого заранее установленного максимума, после чего оно остается постоянным до окончания периода тактового генератора 1.

Интервалы 19, 20, 21 и 22 выбраны таким образом, чтобы получить наилучшее приближение кода на выходе дешифратора 8 к синусоиде при равномерном квантовании по уровню. На первом интервале сигнал на выходе дешифратора равен 00, поэтому цифровой элемент 11 сравнения не фиксирует ни одного интервала, на котором сигнал дешифратора 8 превышал бы число, записанное в счетчике 5. На интервале 20 на выходе дешифратора появляется код 01, так что на протяжении одного периода работы интегратора 2 код превышает число, записанное в счетчике 5. На этом интервале формируется импульс выходного напряжения инвертора.

Аналогично на интервале 21 выходные импульсы инвертора охватывают два такта работы интегратора 2. Таким образом, выходные импульсы имеют ширину, пропорциональную коду на выходе дешифратора 8, Глубину модуляции, т. е. ширину выходных импульсов, можно изменять при изменении управляющего напряжения, подаваемого от источника 4. Код на выходах дешифраторов

9 и 10 сдвинут относительно кода дешифратора 8 на 120 и 240 эл. град. выходной частоты инвертора, Таким образом, в предлагаемом устройстве нет блока формирования многофазного прямоугольно-ступенчатого напряжения, регулируемого по амплитуде. Взамен этого имеется источник 4 постоянного управляющего напряжения. Дополнительно введенные элементы представляют собой стандартные элементы цифровой микроэлектроники, выпускаемые серийно, не требующие наладки и поэтому обеспечивающие высокую стабильность и точность работы. При этом устройство обеспечивает реализацию всех достоинств, присущих инверторам с широтно-импульсной модуляцией по вертикальному способу управления: линейность регулировочных характеристик, хороший гармонический состав выходного напряжения, независимость регулирования частоты и напряжения в широких пределах.

Формула изобретения

Устройство для управления m-фазным автономным инвертором напряжения, содержащее тактовый генератор, связанный через интегратор с компаратором, второй вход которого связан с источником управляющего напряжения, отличающееся тем, что, с целью повышения точности, оно снаб35 жено двумя счетчиками, генератором опорной частоты, m дешифраторами и m цифровыми элементами сравнения, причем, выход компаратора связан с цепью сброса интегратора и входом первого счетчика, выход которого связан со входами цифровых эле4в ментов сравнения, генератор опорной частоты через второй счетчик и дешифраторы связан со вторыми входами цифровых элементов сравнения, выход тактового генератора связан с цепью обнуления первого счетчика.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3958171, кл. 321/9А, 1964.

2. Патент Великобритании № 1190847, so кл. -H, 2 F, 1972.

902201

Составитель О. Парфенова

Редактор М. Янович Техред А. Бойкас Корректор А. Гриценко

Заказ 124)4/68 Тираж 7)8 П од и исное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

П3035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4