Селектор импульсов по длительности

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Соцналнстнческнх

Республнк о»902240 (61) Дополнительное к авт. саид-ву р М g+ з (22) Заявлено .1 1.06.80 (21) 2938478/18-21

Н 03 К 5/26

G 05 В l/Ol с присоединением заявки №вЂ” (23) Приоритет—

Государственный комитет

СС СР по делам изобретений и открытий (53) УДК 621. 374. .33(088.8) Опубликовано 3001.82. Бюллетень ¹4

Дата опубликования описания 300 1.82 (54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ

Изобретение относится к импульсной технике и может быть и"пользовано для селекции импульсов по заданной длительности.

Известен селектор импульсов по длительности, содержащий генератор импульсов, счетчик, два триггера, три схемы И, схему ИЛИ и инвертор (1).

Недостатки данного селектора сложность и невозможность селектирования импульсов, длительность которых лежит в заданных нижнем и верхнем пределах допуска. Данный селектор позволяет производить селекцию только тех импульсов, длительность которых 15 превышает заданную величину, не ограниченную сверху.

Известен селектор импульсов по длительности, содержащий генератор тактовых импульсов, счетчик, два дешифратора, два триггера, элемент задержки, два элемента И и инвертор (2).

Недостатками данного селектора являются сложность, большие затраты оборудования на его реализацию и не- 25 возможность формирования выходных импульсов изменяемой длительности.

Данный селектор вырабатывает выходной импульс длительностью, всегда равной длительности тактового импуль- 30 са с выхода генератора в ответ на входной импульс, длительность которого соответствует нижнему и верхнему пределам допуска.

Наиболее близким по технической сущности к предлагаемому является селектор импульсов по длительности, содержащий элемент сброса и два сдвиговых регистра, синхронизирующие входы которых соединены между собой, а выход второго регистра соединен с выходной шиной (3}.

Недостатками данного селектора являются низкая надежность из-за сложности больших затрат оборудова» ния на его реализацию, невозможность формирования выходных импульсов с наперед заданной стабильной длительностью

11ель изобретения — повышение надежности за счет упрощения.

Поставленная, цель достигается тем, что в селектор импульсов по длительности, содержащий элемент сброса и два сдвиговых регистра, синхронизирующие входы которых соединены между собой, а выход второгр регистра соединен с выходной шиной, введены элемент ИЛИ, два элемента И и инвертор, вход которого соединен

902240

10 вого, записывается логическая единица, так как на синхронизирующий

)5 вход регистра 1 постоянно поступают синхронизирующие импульсы, обеспечивающие сдвиг логической единицы из предыдущего разряда в последующий.

Количество разрядов регистра 1, в которые записывается логическая единица, зависит от длительности входных импульсов.

Если длительность входного импульса меньше нижнего предела допуска длительности, то i-й разряд регистра 1 находится в нулевом состоянии, т.е ° на первом выходе регистра 1 будет уровень логического нуля, а на втором выходе - уровень логической единицы. После окончания входного импульса на выходе инвертора 3 формируется уровень логической единицы, воздействующий на вторые входы первого б и второго 7 элементов И и на первый вход элемента 5 сброса.

Элемент 5 сброса не срабатывает, так как его второй вход находится в состоянии логического нуля, второй регистр 2 не запускается и на выходе

4О селектора не будет отклика на данный входной импульс. Так как первый вход первого элемента И соединен с вторым выходом первого регистра 1, находящийся в состоянии логической единицы, - 45 то первый элемент И б срабатывает и через элемент ИЛИ 4 обнуляет первый регистр 1.

Селектор готов к приему следующего входного импульса.

Если длительность входного импуль- са больше верхнего предела допуска длительности, то и-й разряд регистра

1 находится в единичном состоянии, т.е. на третьем выходе регистра 1 будет уровень логической единицы, а на четвертом выходе - уровень логического нуля. После окончания входного импульса на выходе инвертора 3 формируется уровень логической единицы, воздействующей на вторые входы .первого б и второго 7 элементов И и на первый вход элемента 5 сброса.

Элемент 5 сброса не срабатывает, так как его третий вход находится с информационной шиной и с информационным входом первого регистра, выход — с первым входом элемента сброса и со вторыми входами первого и второго элементов И, первые входы которых соединены соответственно с вторым и с третьим выходами первого регистра, выходы - соответственно с первым и с вторым входами элемента ИЛИ, выход

1 которого соединен с установленным входом первого регистра, синхронизирующий вход которого соединен с шиной синхронизации, первый и четвертый выходы — соответственно с вторым и с третьим входами элемента сброса, выход которого соединен с третьим входом элемента ИЛИ и с установочным входом второго регистра, информационный вход которого соединен с шиной нулевого потенциала.

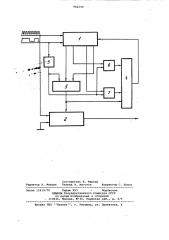

На чертеже приведена функциональная схема предлагаемого селектора импульсов по длительности.

Селектор импульсов по длительности содержит первый сдвиговый регистР 1< синхронизирующий вход которого соединен с синхронизирующим входом второго сдвигового регистра 2 и с шиной синхронизации. По шине синхронизации поступают импульсы высокой частоты от генератора импульсов (не показан) .

Информационный вход регистра 1 соединен с входом инвертора 3 и с информационной шиной, а установочный вход — с выходом элемента ИЛИ 4 °

Первый и четвертый выходы регистра

1 соединены соответственно с вторым и с третьим входами элемента 5 сброса, второй и третий выходы — с первыми входами соответственнс первого

6 и второго 7 элементов И, вторые входы которых объединены между собой и соецинены с первым входом элемента 5 сброса и с выходом инвертора 3.

Выходы первого б и второго 7 элементов И соединены соответственно с пер вым и вторым входами элемента HJIH 4, третий вход которого соединен с выход"м элемента 5 сброса и с установочным входом второго регистра 2, информационный вход которого соединен с шиной нулевого потенциала.

Первый и второй выходы первого регистра 1 соответствуют прямому и инверсному выходам 1-го разряда регистра 1. Наличие единицы в

i-oM разряде первого регистра 1 означает, что длительность входного селектируемого импульса соответствует нижнему пределу допуска длитель ности °

Третий и четвертый выходы первого регистра 1 соответствуют прямому и инверсному выходам r1-го разряда регистра 1. Наличие единицы в и-ом разряде первого регистра 1 зна чит, что длительность входного селектируемого импульса превышает верхний предел допуска длительности.

Селектор импульсов по длительности работает следующим образом.

В исходном состоянии, .когда входные импульсы не поступают на информационную шину, регистры 1 и 2 находятся в обнуленном состоянии.

При .поступлении на информационный вход регистра 1 входного импульса с информационной шины в разряды регист. ра 1 последовательно, начиная с перв состоянии логического нуля, второй

902240 регистр 2 не запустится и на выходе селектора не будет отклика на данный входной импульс. Так как первый вход второго элемента И 7 соединен с третьим выходом регистра 1, находящимся в состоянии логической единицы, то второй элемент И 7 срабатывает и через элемент ИЛИ 4 обнуляет первый регистр 1.

Селектор готов к приему следующего входного импульса. !

О

Если длительность входного импульса находится в пределах нижнего и верхнего допусков длительности, то

i-й разряд регистра 1 находится в единичном состоянии, а и-й разряд— в нулевом состоянии °

После окончания входного импульса уровень логической единицы с выхода инвертора 3 воздействует на первый вход элемента 5 сброса, на второй и третий входы которого поступают в 20 данном случае уровни логической единицы соответственно с первого и четвертого выходов первого регистра

1. Элемент 5 сброса срабатывает и на его выходе появляется сигнал, котоРый я5 через элемент ИЛИ 4 обнуляет первый регистр 1 и воздействует на второй регистр 2 устанавливая все его раз1

Ряды в единичное состояние.

На выходе второго регистра 2, связанного с выходной шиной, появляется импульс, длительность которого определяется количеством разрядов второго регистра 2 и частотой синхронизирующих импУльсов. Так как информационный вход второго регистра 2 связан с шиной нулевого потенциала, то синхронизирующие импульсы, постоянно поступающие на синхронизирующий вход второго регистра 2, производят последовательное обнуле- 40 ние разрядов регистра 2, начиная с .первого. При обнулении последнего разряда второго регистра 2 выходной импульс прекращает вырабатываться.

Нижний и веРхний предел допусков 45 длительности селектируеьых импульсов можно легко изменить, подключая выходы первого регистра 1 к соответствующим разрядам.

Длительность выходных импульсов, являющихся откликом на входные импульсы, также легко изменять, уменьшая или увеличивая количество разрядов второго регистра 2.

Таким образом, введение элемента

ИЛИ, двух элементов И и инвертора позволяет исключить из него входной логический блок, импульсный выходной каскад, счетчик, решающий логический блок, каскад стробирования и два элемента сброса, т.е. повысить надежность.

Кроме того,предлагаеьый селектор позволяет формировать стабильные выходные импульсы, длительность которых можно регулировать в широких пределах от одного периода следования синхрониэирующих импульсов до периода следования входных селектируемых импульсов.

Формула изобретения

Селектор импульсов по длительности,. содержащий элемент сброса и два сдвиговых регистра, синхронизирующие входы которых соединены между собой, а выход второго регистра соединен с выходной шиной, о тл и ч а ю шийся тем, что, с целью повышения надежности за счет упрощения, в него введены элемент

ИЛИ, два элементы И и инвертор, вход которого соединен с информационной шиной и с информационным входом первого регистра, выход - с первым входом элемента сброса и с вторыми входами первого и второго элементов И, первые входы которых соединены соответственно с вторым и с третьим выходами первого регистра, выходы— соответственно с первым и с вторым входами элемента ИЛИ, выход которого соединен с установленным входом первого регистра, синхронизирующий вход которого соединен с шиной синхронизации, первый и четвертый выходы которого соединены соответственно с вторым и с третьим входами элемента сброса, выход которого сое-! динен с третьим входом элемента ИЛИ и с установочным входом второго регистра, информационный вход которого соединен с шиной нулевого потенциала

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 558394, кл. Н 03 К 5/18, 1977.

2. Авторское свидетельство СССР

9 658727, кл. H 03 К 5/24, 1979.

3. Патент COLA 9 3790881, кл. Н 03 К 5/20, 1974 (прототип).

Составитель Н. Маркин

Редактор A. Мотыль Техред Т. Маточка Корректор С. Щомак

Заказ 12419/70 Тираж 953 4 ПОдписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4