Устройство анализа телеметрических сигналов

Иллюстрации

Показать всеРеферат

Союз Советскнн

Соцмапмстмчески к

Респубпмк

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<н>902281 (6l ) Дополнительное к авт. свнд-ву (22) Заявлено 14.03.79 (21) 2739357/18-09 с присоединением заявки М (23) Приоритет

Опубликовано 30.01 82 Бюллетень №

Дата опубликования описания 02.02.82 (51)М. Кл.

Н 04 1/00

ГооудвротвснныН комитет

СССР но яелем изобретений н открытий (53 ) Уд К 621. 394., .14 (088.8) ; 72) Авторы изобретения

I !

f

Х. Эсенов н Д. Ялкапов (71 ) заявители (54) УСТРОЙСТВО АНАЛИЗА ТЕЛЕМЕТРИЧЕСКИХ

СИГНАЛОВ

Изобретение относится к связи и может использоваться цля обнаружения и предотвращения ошибок в принятой информации от передатчика летательных аппаратов.

Известно устройство анализа телеметрических сигналов, содержащее последовательно соединенные блок выделения входного сигнала и блок задержки, а также пороговый блок и приемник (lj .

Однако известное устройство не обеспечивает необходимого быстродействия.

Цель изобретения - повышение быстроцействия.

Указанная цель достигается тем, что в известное устройство анализа телеметрических сигналов введены последовательно соединенные элемент задержки, формирователь импульсов, элемент

HE и первый элемент И, а также регистр памяти, блок управления, коммутатор, блок вычисления конечных разностей и последовательно соединенные второй элемент И, ключ и сумматор, выход которого подключен к входу приемника, а к второму входу сумматора подключен выход блока задержки, вход которого объединен с входом регистра памяти, к входам сброса второго и третьего раз5 ряцов которого подключен выход первого элемента И, при этом выходы разрядов регистра памяти через коммутатор подключены к входам блока вычисления конечных разностей, вход которого под !

О ключен к входу порогового блока, причем выход порогового блокь подключен к входу элемента задержки, второму вхо» ду первого элемента И и первому входу вт орог о элемента И, к второму в ходу

15 которого подключен выхоц формирователя импульсов, а второй выход третьего разряда регистра памяти подключен к входу блока управления, выходы которо20 го подключены к управляющим входам коммутатора и ключа.

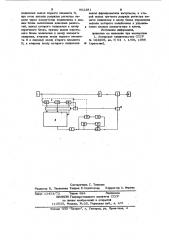

На чертеже приведена структурная электрическая схема предлагаемого устройства.

1 ф

l4, выработанным из второго. третьего и четвертого значений сигнала с выхода регистра 5. Поскольку все четыре значения входного сигнала верны, на выкоде порогового блока 9 имеется нулевое значение сигнала. Если пятое значение входного сигнала не верно, то на выходе порогового блока 9 появляется единичное значение сигнала. При этом элемент И

13 вырабатывает сигнал, стирающий сигналы в ячейках 17 и 18 (так как формирователь 11 на выходе имеет "0 ).

Одновременно по сигналу с блока 7 управления размыкаются контакты коммутатора 6, и с элемента И 14 в приемник 4 сигнал не поступает и таким образом третье и четвертое значения сигнала не отмечаются. При поступлении пятого значения сигнала в ячейку 18 коммутатор 6 срабатывает, сигнал с выхода элемента И 14 "1» (так как с порогового элемента поступает сигнал "1 и также с формирователя 11 поступает сигнал

»1 ) °

Поэтому в сумматоре 12 пятое значение входного сигнала отмечается и т.д. По отмеченным значениям сигнала в приемнике 4 легко их выбрать и получить полное сведение о достоверности принятых сигналов.

Предлагаемое устройство позволяет автоматизировать процесс обработки радио-телеметрических цифровых сигналов и повысить быстродействие обработки информации, а также делает возможным обработку нелинейной информации.

Устройство анализа телеметрических сигналов, содержащее последовательно соединенные блок выделения входного сигнала и блока задержки, а также пороговый блок и приемник, о т л и ч а ющ е е с я тем, что, с целью повышения но соединенные элемент зайержки, формирователь импульсов, элемент НЕ и перключ и сумматор, выход которого подключен к входу приемника, а к второму задержки, вход которого обьединен с входом регистра памяти, к входам сброса второго и третьего разрядов которого

3 90228

Устройство анализа телеметрических сигналов содержит блок 1 выделения вкоцного сигнала, блок 2 задержки, сумт матор 3, приемник 4, регистр 5 памяти, коммутатор 6, блок 7 управления, блок

8 вычисления конечных разностей, пороговый блок 9, элемент 10 задержки, формирователь 11 импульсов, элемент

HE 12, первый 13 и второй 14 элементы И, ключ 15. Регистр 5 выполнен на ячейках 16-18.

Устройство работает слецующим образом.

Из блока 1 выделенный входной сигнал, имеющий дискретную форму, посту- 1f пает в блок 2 задержки и на вход (в ячейку 16) регистра 5. Пока три после- довательные, значения сигнала не поступят в блок 2 задержки и в ячейку 16, сигнал в приемник 4 не поступает. Когда третье значение сигнала поступнт в ячейку 1 6, е го предыдущее значение поступает в ячейку 17, а первое значение — в ячейку 18. При этом по сигналу с блока

7 управления срабатывает коммутатор 6 1д и эти три последовательные значения входного сигнала с ячеек 16 - 18 регистра 5 поступают в блок 8, с выхода которого вычисленные разности сигналов поступают на пороговый блок 9, где сравнивается с заданным порогом. На выходе порогового блока вырабатывается сигнал, который может иметь значения»0" нли»1", при этом нулевое значение этого сигнала соответствует случаю, когда все три после33 довательные значения принятых сигналов верные. В случае, когда хотя бы одно из трех обрабатываемых значений сигнала ошибочно, сигнал на выкоде порогового Формула изобретения блока 9 имеет значение "1

В начале работы устройства формирователь 11 вырабатывает сигнал в виде

"1 . Сигналы с выходов формирователя

11 и порогового блока 9 умножаются в элементе И 14 и на его выкоде появляется сигнал в виде "0 или 1 . Выход»»»»

45 ной сигнал элемента И 14 поступает быстродействия, введены последовательодновременно с первым значением сигна ла с выхода блока 2 задержки. Если три последовательные значения входного сиг- вый элемент И, а также регистр памяти, нала верны, то на первом значении сиг- блок управления, коммутатор, блок вы50 нала с блока 2 задержки никакая отмет- чйсления конечных разностей и последока не делается. вательно соединенные второй элемент И, При появлении четвертого значения входного сигнала на выходе блока 2 за держки появляется сигнал, который пред- >> входу сумматора подключен выход блока ставляет второе значение входного сигнала, поступающее в приемник 4 оцновременно с выходным сигналом элемента И

5 90228 1 4 подключен выход первого элемента И, выход фармирователя импульсов, а вто при этом выходы разрядов регистра па- рой выход третьего разряда регистра памяти через коммутатор подключены к вхо- мяти подключен к входу блока управления дам блока вычисления конечных разнос- выходы которого подключены к управлятей, выход которого подключен к входу g ющим входам коммутатора и ключа. порогового блока, причем выход псрого- Источники информации, вого блока подключен к входу элемента принятые во внимание при экспертизе задержки, второму входу первого элемен- 1, Авторское свидетельство СССР та И и первому входу второго элемента % 183806, кл. Н 04 L 1/00, 1966

И, к второму входу которого подключен 1О (прототип).

Составитель Г. Теплова

Редактор В. Пилипенко Техред E.Õàðûòoí÷èê Корректор A. Ференц

И»

Заказ 12433/72 Тираж 684 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

° ИВОЮ ФВ ° ВВЮЮВЮЮИЮВ

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4