Устройство для сопряжения цифровой вычислительной машины с магнитофоном

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистическин

Республик

ОЛ ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()903854 (6l ) Дополнительное к авт. свид-ву— (22)Заявлено 30.06.80 (21) 2952134/18-24 с присоединением заявки М— (23) Приоритет—

Опубликовано 07.02.82. Бюллетень М 5 °

/ (5I)M. Кл.

G 06 F 3/04

Гасударствтнный квинтет вв делан нэвбрвтеннй н OTKpblTNN (53) УДК 681.325 (088.8) Дата онубликоваиия описания 07.02.82!

М.M.Êàíåâñêèé, N.À.Êàùàâöåâ, Б.А.Прони и ГйЪ:.Чайковский з

- Гн а з

Всесоюзный научно-иссоенонатеннски;": инфитут з электромеханики 3 (72) Авторы изобретения (7l) Заявитель (54) УСТРОЙСТВО Д1И СОПРЯЖЕНИЯ ЦИФРОВОЙ

ВЫЧИСЛИТЕ11ЬНОй MAliINHbl C ИАГНИТОФОНОИ

Изобретение относится к вычислительной технике и может быть исполь. зовано для сопряжения вычислительной машины с кассетным магнитофоном звукозаписи.

Известно устройство сопряжения цифровой вычислительной машины с внешним устройством, содержащее каналы вывода и ввода информации, при этом канал вывода информации вклю10 чает три ключа и преобразователь прямоугольных импульсов в синусоиду, причем один вход двух ключей соединен между собой и является входо1ч устройства, на который подается ин15 формационный сигнал последовательным кодом с цифровой вычислительной машины, а другой вход первого ключа подключен к выходу блока синхронизации, с которого поступает сигнал преобразования, соответствующим "0" другой вход второго ключа подключен к другому выходу блока синхронизации, с которого постугзет сигнал преобразования, соответствующий "l" а выходы этих ключей подключены ко входам третьего ключа, выход которого подключен к преобразователю прямоугольных импульсов в синусоиду, и его выход является первым выходом устройства, канал ввода информации включает компаратор и цифровой анализатор частот, собранный на четырех триггерах, ключе и счетчике, при этом второй вход первого триггера соединен со вторым входом третьего триггера, йрямой выход первого триггера соединен с первым входом ключа и с первым входам третьего триггера, инверсный выход последнего соединен со вторым входом ключа, выход которого соединен с первым входом счетчика, прямой выход второго триггера соединен с первым входом четвертого триггера, выход которого является вторым выходом устройства, первый вход второго триггера соединен с источником постоянного напря903854 жения, а блок синхронизации собран на счетчике, пяти кличах и двух эле ментах HE (l ).

В этом устройстве для получения достоверной информации приходится использовать на один бит информации четыре периода сигнала преобразова ния соответствующего "0", и восемь периодов сигнала преобразования, соответствующего "!", что приводит к 10 снижению скорости обмена.

Наиболее близким к изобретению по технической сущности является устройство для сопряжения цифровой вычислительнсн машины с кассетным

15 магнитофоном звукозаписи, содержащее каналы вывода и ввода информации и блок синхронизации, канал вывода информации состоит из синхронизируюцего триггера, элемента НЕ, модулятора, содержащего два элемента

И-HE и элемент ИЛИ-НЕ, и преобразова. теля прямоугольных импульсов в синусоиду, при этом выход устройства через преобразователь прямоугольных импульсов в синусоиду подключен к выходу элемента ИЛИ-НЕ, входы которого подключены к выходам соответствующих элементов И-НЕ, первые входы которых подключены соответо„твенно к прямому и инверсному выходам синхронизирующего триггера, первый вход которого является первым входом устройства, а второй вход через элемент

HE соединен со вторым входом второго элемента И-НЕ, вторые входы элементов

И-НЕ соединены с. соответствующими выходами блока синхронизации, канал ввода содержит компаратор, формирователь, цифровой анализатор частот, 4 состоящий иэ четырех триггеров, счетчика и элемента И-HE при этом прямой вход компаратора является вторым входом устройства, инверсный вход и выход компаратора подключены соответ- > ственно к выходу и входу делителя напряжения, инверсный выход соединен через формирователь с первым входом первого триггера, второй вход которого соединен со вторыми входами второ- зО го триггера, счетчика и входом блока синхронизации и является входом средней частоты устройства, прямой выход первого триггера соединен со входом элемента И-НЕ и первым входом второго 55 триггера, инверсный выход которого соединен со вторым входом элемента

И-НЕ, выход которого соединен со вторыми входами третьего и четвертого триггеров и первым входом счетчика, выходом соединенного с третьими входами третьего и четвертого триггеров, прямой выход которого является цифровым информационным выходом устройства, первый вход триггера соединен со входом постоянного напряжения устройства, прямой выход третьего триггера соединен с первым входом четвертого триггера P2$.

Недостатком данного устройства является низкая пропускная способность, так как на один бит информации приходится. использовать один период сигнала преобразования, соответствующего "0", и два периода сигнала преобразования, соответствующего

"1". Кроме того, в данном устройстве при считывании записанной информации на разных магнитофонах возможно несовпадение фазы считываемого сигнала, что приводит к необходимости произвоводить повторное считывание с изменением фазы запускающего сигнала в цифровом анализаторе частот.

Цель изобретения — повышение про-, пускной способности устройства и до» стоверности обрабатываемой информа-. ции.

Поставленная цель достигается тем, что в устройстве, содержащем блок синхронизации, канал вывода, состоящий из синхронизирующего триггера, элемента НЕ и модулятора, содержащего два элемента И-НЕ и первый элемент ИЛИ-НЕ, причем первые входы первого и второго элементов И-НЕ соединены соответственно с прямым и инверсным выходами синхронизирующего триггера, а вторые входы— соответственно с первым и вторым выходами блока синхронизации, вход которого соединен с входом опорной частоты устройства, первый вход синхронизирующего триггера является циф= ровым информационным входом устройства, а второй вход через элемент

НЕ подключен ко второму входу первого элемента И-НЕ, выходы первого и второго элементов И-HE соединены с соответствукнцнми входами первого элемента ИЛИ-НЕ, и канал ввода, включающий цифровой анализатор частот, состоящий из четырех триггеров и счетчика, и компаратор, инверсный вход и выход которого подключены соответственно к выходу и входу

903854 6 щий из элементов И-HE 7 и 8, элемента ИЛИ-НЕ 9, триггера 10 модулятора, и формирователь II разнополярных сигналов, цифровой информационный вход 12 устройства, аналоговый информационный выход 13 устройства.

Канал 2 ввода включает полосовой фильтр 14, компаратор 15, резисторы

16 и 17 делителя напряжения, формирователь 18 импульсов. цифровой ана" лизатор 19 частот, состоящий из первого 20, второго 2 1, третьего 22, четвертого 23 и пятого 24 триггеров (Д-триггеров), двух элементов И 25 и 26, элемента ИЛИ-НЕ 27, счетчика

28, ачалоговый информационный вход

29 устройства, вход 30 опорной чар- стоты устройства, цифровой информационный выход 31 устройства, вход р 2О 32 постоянного напряжения.

Блок 3 синхронизации имеет выход

33 частоты преобразования, соответствующей "0", выход 34 частоты преI I 11 образования, соответствующеи 1 и вход 35 опорной частоты.

Устройство работает следующим образом. делителя напряжения, выход компаратора соединен через формирователь импульсов с первым входом первого триггера, второй .вход nepioro триггера и первые входы второго триггера и счетчика подключены ко входу блока синхронизации, прямой выход первого триггера соединен со вторым входом второго триггера, первый вход третьего триггера соединен со входом постоянного напряжения устройства, прямой выход — с первым входом четвертого триггера, выход счетчика соединен со вторыми входами третьего и четвертого триггеров, а второй вход — с третьими входами третьего

I и четвертого триггеров, в канал вывода введены формирователь разнополя ных сигналов и триггер модулятора, Ь канал ввода введен полосовой фильт а в цифровой анализатор частот— пятый триггер, два элемента И и второй элемент ИЛИ-НЕ, причем вход полосового фильтра является аналоговым информационным входом устройства, а выход подключен к прямому входу ком паратора, входы первого элемента Р .подключены соответственно к прямому выходу первого триггера и инверсному выходу второго триггера, входы вто- зо рого элемента И подключены соответственно к инверсному выходу первого триггера и прямому выходу второго триггера, выходы первого и второго элементов И соединены соответственно з с первым и вторым входами второго элемента ИЛИ-НЕ, выход которого подключен ко второму входу счетчика и первому входу пятого триггера, второй вход которого соединен с прямым 4о выходом четвертого триггера, прямой выход пятого триггера является цифровым информационным выходом устройства, прямой выход триггера модулятора через формирователь разнополяр-as ных сигналов соединен с аналоговьм информационным выходом устройства, инверсный выход триггера модулятора соединен с первым его входом, а второй вход — с выходом первого элемента So

ИЛИ-НЕ.

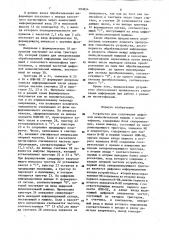

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит канал 1 выво55 да, канал 2 ввода и блок 3 синхронизации. Канал I вывода включает синхронизирующий триггер 4 (Д-триггер) элемент НЕ 5, модулятор 6, состояВ режиме вывода информация с циф" ровой вычислительной машины последовательным кодом поступает через цифровой информационный вход 12 устройства на первый вход (вход Д) синхронизирующего триггера 4 и переводит его в случае необходимости через элемент НЕ 5 в другое состояние только при поступлении синхронизирующего сигнала на второй вход (вход C) синхронизирующего триггера 4. Часто; та синхронизирующего сигнала выбрана равной частоте сигнала преобразования, соответствующей "0". В зависимости от состояния синхронизирующего триггера 4 через элементы

И-НЕ 7 или 8 на выходе элементе .

ИЛИ-НЕ 9 появляются импульсы с частотой, например, 5 кГц или с частотой 10 кГц, соответствуищей частоте сигнала преобразования, соответствующего "1". Этот сигнал формируется в блоке 3 синхронизации. Двухчастот" ный сигнал с элемента ИЛИ-НЕ 9 по» ступает на триггер 10 модулятора, на котором получается фазокодированный сигнал, поступающий через формирователь 11 разнополярных сигналов на аналоговый информационный выход 13 устройства и далее на вход кассетного магнитофона.

903854

В режиме ввода обрабатываемая информация поступает с выхода кассет ного магнитофона через аналоговый информационный вход 29 и полосовой фильтр 1,4 на компаратор 15, с выхода которого последовательность импульсов с частотой 2,5 кГц или 5 кГц поступает на вход формирователя 18, формирующего импульсы с крутыми фронтами. tO

Импульсы с формирователя 18 импульсов поступают на вход триггера

20, который служит для синхронизации обрабатываемой информации поступающей с кассетного магнитофона звукозаписи, с опорной частотой цифровой вычислительной машины, поступающей по входу 30. . Триггеры 20 и 21, элементы И 25 и 26 и ИЛИ-НЕ 27 формируют импульсы 20 запуска информационной части анализатора частоты счетчика 28 и триггеров 22, 23 и 24. Импульсы запуска в данной схеме формирования получаются как по положительному, так и по отрицательному перепаду напряжения, что позволяет исключить зависимость считывания от фазы информационного сигнала. Ио импульсу запуска, сформированному на выходе 36 элемента ИЛИ-НЕ 27, производится запись числа в счетчик 28„ триггер 22 устанавливается в "i" а триггеры

23 и 24 сохраняют предыдущее положение. Число, записанное в счетчик

28, начинает считываться импульсами опорной частоты. Если с кассетного магнитофона считывается частота преобразования, соответствующая "0" (2,5 кГц), иа выходе счетчика 28 по- щ является импульс переноса, который устанавливает триггеры 22 и 23 в "0".

При формировании следующего запуска-, ющего импульса триггер 22 устанавливается в "1", триггер 23 остается в предыдущем положении, а триггер 24 переходит в положение, в котором находится триггер 23. На цифровом информационном выходе 31 формируется сигнал, соответствующий "0", который поступает на вход цифровой вычислительной машины. Лрименение триггера 24 позволяет симметрировать выходной информационный сигнал, поступающий в машину. Если с кассетного магнитофона считывается частота, соответствующая "1" (5 кГц),на выходе счетчика 28 импульсы переноса не появляются, так как до того как записанное в счетчике число будет считано, в счетчик 28 записывается следующее число, а на выходе триггера

24 формируется сигнал, соответствующий "1", поступающий на вход цифровой вычислительной машины.

Таким образом, предлагаемое изобретение позволяет повысить пропускную способность устройства, достоверность обрабатываемой информации и скорость обмена между цифровой вычислительной машиной и кассетным магнитофоном звукозаписи путем умень» шения числа периодов сигнала преобразования на один бит обрабатываемой информации до одного полупериода для сигнала преобразования, соответствующего "0", и до одного периода сигнала преобразования, соответствуюшего "i".

Кроме того, предлагаемое устройство обеспечивает правильность считывания информации при работе с разнымн магнитофонаьы.

Формула изобретения

I устройство для сопряжения цифровой вычислительной машины с магнитофоном, содержащее блок синхронизации, канал вывода, состоящий из сннхронизирующего триггера, элемента НЕ и модулятора, содержащего два элемента И-НЕ и первый элемент ИЛИ-НЕ, причем первые входы первого и второго элемента И-НЕ соединены соответственно .с прямым и инверсным выходами синхронизирующего триггера, а вторые входы — соответственно с первым и вторым выходами блока синх-. ронизации, вход которого соединен с входом опорной частоты устройства, первый вход синхронизирующего триггера является цифровым информационным входам устройетва,а второй вход через элемент НЕ подключен ко второму входу первого элемента И-НЕ, выходы первого и второго элементов И-НЕ соединены с со- ответствукицими входами первого элемента ИЛИ-HE и канал ввода включающий цифровой анализатор частот, состоящий из четырех триггеров, и счетчика, и компаратор, инверсный вход и выход которого подключены соответственно к выходу и входу делителя напряжения, выход компара9 9038 тора соединен через формирователь им-. пульсов с первым входом первого триггера, второй вход первого триггера и первые входы второго триггера и счетчика подключены ко входу блока синхронизации, прямой выход первого триггера соединен со вторым входом второго триггера, первый вход третье.

ro триггера соединен со входом постоянного напряжений устройства, 1О прямой выход - с первым входом четвертого триггера, выход счетчика соединен со вторыми входами третьего и четвертого триггеров, а второй вход — с третьими входами третьего 5 и четвертого триггеров, о т л и ч аю щ е е с я тем, что, с целью повышения пропускной способности устройства, в канал вывода введе« ны формирователь раэнополярних сигналов и триггер модулятора, в канал ввода введен полосовой фильтр, а в цифровой анализатор частот — пятый триггер, два элемента И и второй элемент ИЛИ-НК, причем вход полосового фильтра является. аналоговым информационным входом устройства, а выход подключен к прямому входу компаратора, входы первого элемента И подключены соответствен- З1 но к прямому выходу первого тригге»

54 ра и инверсному выходу второго гера, входы второго элемента И подключены соответственно к инверсному выходу первого триггера и прямому выходу второго триггера, выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента

ИЛИ-НЕ, выход которого подключен ко второму входу счетчика и первому входу пятого триггера, второй вход которого соединен с прямым выходом четвертого триггера, прямой выход пятого триггера является цифровым информационным выходом устройства прямой выход триггера модулятора че реэ формирователь раэиополярных сиг налов соединен с аналоговым информа» ционным выходом устройства,.инверсный выход триггера модулятора соединен с первым его входом, а второй вход — с выходом первого элемента

ИЛИ-НЕ

- Источники-ннформацнм— принятые во внимание при экспертиэе

1. H1tachi Microcomputer system

tre 1ning module Н 68/TR, 1977, р. ЗУ.

2. Авторское свидетельство СССР по заявке В 2759102/18-24, кл. 6 Об F 3/04, 1979 (прототип).

903854

Г

1 !

-I

I 1

Г, I

1

) Г 1 1 1

II

)I

II 1 1

1 !

t

III

1

Составитель В.Вертлиб

Редактор В.Данко Техред Т. Маточка КорректоР Б.Бутяга г

3аказ 121/30 Тираж 731 Подписное

ВНИИ11И Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал 1!!Ш "Патент", г. Ужгород, ул. Проектная, 4