Устройство для определения наименьшего из @ чисел

Иллюстрации

Показать всеРеферат

7 (72) Авторы изобретению

B.Ã. Попов

B.Ë. Areee, В.Б. Красильников, А.Н. Плеаанов и (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАИИЕНЬШЕГО

ИЗ и ЧИСЕЛ

Изобретение относится к автоматике и вычи сли тельной техни ке и может быть использовано при реализации техннчес" ких средств цифровых систем контроля, систем обработки данных и автоматизированных систем управления.

Известно устройство для определения наибольшего и наименьшего из и чисел и их максимальной разности, со" держащее и входных регистров, элементы ИЛИ (11.

Основным недостатком этого устройства является низкое быстродействие, так как определение экстремального числа производится за К тактов работы генератора импульсов, где К - разрядность чисел.

Наиболее близким по технической сущности к изобретению является устройство для сравнения И двоичных чисел, содержащее и регистров, группу элементов И, элементы ИЛИ, регистр результата. В этом устройстве шина тактовых сигналов соединена с первыми входами элементов И т рет ьей группы, выходы которых подключены ко вторым входам элементов И первой группы. Втфрые входы элементов И третьей группы соединены с выходами соответствую щих разрядов регистра результата, вхФды установки в единичное состояние всех разрядов которого, кроме первого, подключены к выходам элементов И четвертой группы, первые входы каждо1О го из которых соединены с выходами соответствующих разрядов сдвигающего регистра, а вторые входы - с выходами первого элемента ИЛИ. Входы этого элемента подключены к выходам первого

15 и второго элементов И, первые входы которых соединены с инверсным и прямым выходами триггера знака соответственно, а вторые входы - с выходами

20 третьего и четвертого элементов И, < первые входы которых подключены к вы ходу первого элемента задержки, кото рый через второй элемент задержки со единен со входами сдвигающего регист .

3 90386 ра и счетчика. Выход счетчика подклю" чен ко входу установки в нулевое состояние сдвигающего регистра, к первым входам элементов И пятой группы, ко входУ установки в нулевое состоя5 ние первого разряда регистра результата и к первым входам группы элементов ИЛИ, выходы которых соединены со входами установки в единичное состояние соответствующих разрядов регистра результата, выходы которого под\ ключены ко вторым входам элементов И третьей и пятой групп. Выходы элементов Й пятой группы соединены с первыми входами элементов И шестой rpynr

1ты, Вторые входы элементов И шестой группы подключены к выходам регистров. Вход третьего элемента задержки соединен с шиной тактовых сигналов, а его выход - со входом nepeoro элемента задержки и с первыми входами элементов И седьмой группы, вторые входы которых подключены к выходам соответствующих разрядов сдвигающего регистра. Выходы элементов И седьмой группы соединены со вторыми входами элементов И второй группы (2).

Недостатком известного устройства является низкое быстродействие, 39 так как сравнение и чисел производится последовательно за k тактовых импульсов, и, кроме того, от разрядности чисел, так как величина такта on" ределяется временем сложения чисел в накапливающем сумматоре.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что s устройстве для определения наименьшего из и чисел, содержащем регистры, дешиф аторы, регистр результата, многовходовой элемент И, поразрядные узлы анализа, элементы ИЛИ, группы элементов И, ИЛИ, причем выходы каждого i"го регистра, где 1 = 1,2,. ° .,n соединены со входами i-го дешифратора и с информационными входами элементов Ь i-ой группы, а выходы i-ro элемента ИЛИ подключены ко входам управления элементов И i-ой группы, выходы элементов И каждой i-ой группы соединены со входами элементов ИЛИ группы, выходы которых подключены ко входам регистра результата, каждый -ый выход каж- З дого i-го дешифратора соединен с i-ым входом j-ro поразрядного узла анали:за, где j = 1,2,...,m,m - число раз1 4 рядов операндов, каждый i-ый выход

j-го поразрядного узла анализа подклЬчен к j-ому выходу i-го элемента ИЛИ, а выход переносов каждого К-го поразрядного узла анализа, где К =

1,2,...,(m- 1), соединен со входом управления (К+1)- го поразрядного узла анализа.

Кроме того, каждый К-ый поразрядный узел анализа состоит из и элементов И, и элементов НЕ и многовходового элемента И, причем каждый i-ый вход узла подключен к первому входу

i-го элемента И, вход управления. узла соединен со вторыми входами элементов И, каждый i-ый вход узла подключен через I-ый элемент НЕ к (i+2)-ому входу (1+1), (i+2),... n-го элементов И и к 1-ому входу многовходового

l ,элемента И, выход которого подключен ,к выходу переносов узла, выход кажl с рого e -ro элемента соединен с 1-ым .выходом узла.

При этой пт-ый поразрядный узел анализа состоит из И элементов И и

{И- I) - го элемента НЕ, причем каждый

Р-ый вход узла, где Р - E,2,...,(È- 1) соединен с первым входом Р-го элемента И, вход переносов узла подключен ко вторым входам элементов И, каждый

Р-ый вход узла через P -ый элемент НЕ соединен с (р+2)-ым входом(Р -1), (p+2),...,È-го элементов И, ти-ый вход узла подключен к (w+2)-ому входу

Vl-ro элемента И, выход каждого q-го элемента И соединен с а -ым выходом узла.

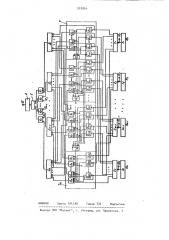

На чертеже представлена блок-схема устройства.

Устройство содержит регистры 1„, 12,...,1и. Де Фраторы 24,2а.. ?и группу элементов ИЛИ 3, регистр 4 результата, элементы ИЛИ 5<, 5,...,5„, группы элементов И 6, 6,...,6,„, поразрядные узлы 7, 7,...,7,„ ана-лиза, каждый К-ый из которых, где

К 1,2.. .,(вФ 1), состоит из элементов HE 8, 8, ..., Зи, элементов М

9, 9,...,9и, иноговходового элемента И 10, N-ый поразрядный узел анализа состоит из элементов НЕ 8,1, 82,...,8я и элементов И 9, 9,...,9„ входы регистров 111, 11,...,11„ выходы регистров 12,12,..., 12 выходи-4 i ные шины 13 устройства.

Устройство работает следующим образом.

5 903864 6 ко входам управления элементов И -с(й группы, выходы элементов И каждой

1-ой группы соединены со входами элементов ИЛИ группы, выходы которыЯ подключены ко входам регистра резуль тата, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в нем каждый -ый выход каждого <-го дешифратора соединен с -ым входом у-го поразрядного узла анали1 за, где g = 1,2,...,1я, и- число разрядов операндов, каждый q -ый выход

+го поразрядного узла анализа подключен к -ому входу e-ro элемента ИЛИ, а выход переносов каждого

К-ro поразрядного узла анализа, где

К = 1,2,...,(Ю.1), соединен со входом управления (К+1)-го поразрядного узла анализа.

2. Устройство по и 1, о т л ич а ю щ е е с я тем, что в нем каждый К-ый поразрядный узел анализа состоит из элементов И, и элементов

НЕ и многовходового элемента И, при" чем каждый 4 -ый вход узла подключен к первому входу 1-го элемента И, вход управления узла соединен со втдрыми входами элементов И, каждый л-ый вход узла подключен через 1-ый элемент HE и (+2)-оиу входу (+1), (i+2)@...,й-го элементов И и к 4-ому входу многовходового элемента И, вы" ход которого подключен к выходу переносов узла, выход каждого 1-го эле"

1 мента соединен с Ф-ым выходом узла.

3. Устройство по и. 1, о т л ич а ю щ е е .с я тем, что в нем м.ы4 поразрядный узел анализа состоит из

И элементов И и (и- 1)-го элемента Н1, причем каждый р-ый вход, узла, где р = 1,2,...,(И- 1) соединен с первым входом р-го элемента И, вход переносов узла подключен ко вторым входам элементов И, каждый р-ый вход узла через р-ый элемент. НЕ соединен с

:(р+2)"ым входом (р-1),(р+2),..., и-го элементов И, m-ый вход узла подключен к {@+2)-ому входу и-го элемен та И, выход каждого i-го элемента И соединен с 1-ым выходом узла.

Пусть наименьшее число находится во втором регистре 1 и равно 1, т.е, на втором выходе дешифратора 2 g будет еди ни чный си гнал. При этих условиях все первые выходы всех дешифраторов, а также вторые выходы, кроме 2- го дешифратора, будут нулевые. Тогда выходы элементов НЕ первого поразрядного узла анализа будут единичными, многовходовой элемент И 10,1 первого о поразрядного узла анализа разрешает .анализ во второй группе, открывая по первым входам все элементы И этой группы. Второй выход первого дешифратора - нулевой, поэтому единичный сигнал с выхода nepsoro элемента HE во втором поразрядном узле анализа 7 открывает по вторым входам все элементы И, начиная со второго °

На входе второго элемента Hf. 8 и на третьем входе второго элемента И 9 действует единичный сигнал.

Нулевой сигнал с выхода элемента 82> закрывает все элементы И во втором поразрядном узле анализа, начиная с у5 третьего, по третьему входу. С выхода элемента И 9з единичный сигнал через элемент ИЛИ g поступает на второй вход элемента И первого поразрядного узла анализа 7 . Число, хранимое в регистре 1, по шинам 12< передается через группу элементов ИЛИ 3 в регистр 4 результата, Очередной цикл работы устройства начинается после приема следующей группы И чисел во входные регистры.

В предлагаемом устройстве время сравнения не зависит ни от количества сравниваемых чисел и ни от их разрядности и определяется суммарным временем анализа в одной группе, так как он выполняется во всех группах одновременно, что позволяет повысить быстродействие.

Формула изобретения

1. Устройство для определения наименьшего из и чисел, содержащее регистры, дешифраторы, регистр резуль- 56 тата, многовходовой элемент И, поразрядные узлы анализа, элементы ИЛИ, группы элементов И, ИЛИ, причем выходы каждого из 1-ro регистра, где

1 1,2,...,и соединены со входами ss

1-го дешифратора и с информационными входами элементов И -ой группы, а выходы -го элемента ИЛИ подключены

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 234003, кл. G 06 l 7/04, !968.

2. Авторское свидетельство СССР

И 664170, кл. 6 06 F 7/02, l979 (прототип).