Управляемый арифметический модуль

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТВЛЬСТВУ

Союз Советсимк

Социалистичесиик республик (ii)90385g (6!) Дополнительное к авт.саид-ву (22) Заявлено 07.01. 80 (21) 2868187/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 07.02.82. Бюллетень № 5

Дата опубликования описания 09.02.82 (5l)М. Кл. 5 06 F 7/38

Йвудврствнпвб камктет СССР ае аваам кзобретеннк и открытий (53) УДК681.3 (088.S) (72) Авторы изобретения (71) Заявитель (54) УПРАВЛЯЕМЫИ АРИФМЕТИЧЕСКИЙ МОДУЛЬ

Изобретение относится к вычислительной технике и может быть использовано для построения различных узлов и устройств цифровых ЭВМ.

Известен управляемый арифметический модуль, содержащий четыре информационных входа и шесть управляюших входов; два выхода, триггер и логические элементы И, ИЛИ, НЕ (1)Недостатком этого модуля является то, что он имеет ограниченные возможности по реализации математических операций, что ухудшает характеристики конструируемых на его основе узлов и устройств. Кроме того, модуль сложен в управлении.

Наиболее близким по технической суш ности к предлагаемому является управляемый арифметический модуль, содержащий триггер, по два элемента И, ИДИ и PABHCGHA×HÎÑTÜ, два коммутатора, три информационных входа, вход перено- са, вход разрешения выполнения операции, девять управляющих входов и два выхода, причем управляющие входы первого коммутатора подключены к управля» юшим входам модуля, а его информационные входы — к информационным входам модуля, выход первого коммутатора сом .

5 динен со входом первого элемента РАВ-.

НОЗНАЧНОСТЬ, второй вход которого является управляюшим входом модуля, а выход соединен с управояюшим входом второго коммутатора, второй управляющий

1О вход которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, первый вход которого является управляюшим входом модуля, а второй соединен с выходом триггера, счетный вход .которого

15 соединен с выходом первого элемента

ИЛИ, первый вход которого соединен со входом переноса устройства, а второйс выходом второго коммутатора, информационные входы которого подключены

20 к управляющим входам модуля, а его стробируюший вход соединен со входом разрешения выполнения операции, входы йервого элемента И соединены со

865 4

903

3 входом переноса модуля, с выходом второго элемента РАВНОЗНАЧНОСТЬ и с первым входом второго элемента

И, второй вход которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, третий вход является управляю, щим входом модуля, а его четвертый вход подключен ко входу разрешения выполнения операции, выходы элементов И соединены со входами второго элемента

ИЛИ, выход которого является выходом нереноса устройства, а выход триггера является выходом результата устройстГ2).

Не достатком известного устройства является его сложность, а также предьявление жестких требований к параметрам импульсного сигнала разрешения выцолнения операции с целью обеспечения устойчивой работы схемы.

Цель изобретения — упрощение конструкции.

Поставленная цель достигается тем, что управляемый арифметический модуль, содержащий элементы РАВНОЗНАЧНОСТЬ и ИЛИ, два элемента И, триггер и два коммутатора, настроечные входы первого из которых являются управляющими входами модуля, а информационные входы подключены к информационным входам устройства, выход триггера является выходом результата модуля, информационные входы второго коммутатора являются управляющими входами модуля, выход элемента ИЛИ является выходом переноса модуля, а его входы соединены с выходами элементов И, первые входы которых подключены соответственно ко входу переноса устройства и выходу первого ком мутатора, содержит зле м ент HE и третий элемент И, выход которого соединен со входом элемента ИЛИ, его первый вход соединен с выходом первого коммутатора, а второй вход объединен со вторым входом второго элемента И и является управляющим входом модуля, третьи входы второго и третьего элементов И соединены соответственно с прямым и инверсным выходами триггера, а их четвертые и пятые входы соединены соответственно с первым и вторым, третьим и четвертым информационными входами второго коммутатора, выход которого соединен со входом элемента

РАВНОЗНАЧНОСТЬ, другой вход которого подключен ко входу переноса модуля, а выход соединен со входом первого элемента И и входом элемента НЕ, а

5 !

О

13

23

3S

43

53 также с единичным входом триггера, вы» ход элемента НЕ соединен с нулевым в дом триггера, синхровход триггера я яется синхровходом модуля, дополн„„„ ный информационный вход модуля явля ется информационным входом первого коммутатора.

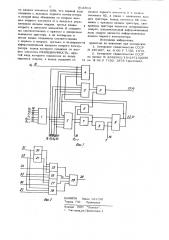

На фиг. 1 показана схема управляемого арифметического модуля; на фиг. 2— схема коммутатора.

Схема управляемого арифметического модуля содержит коммутаторы 1 и 2, элемент ИЛИ 3, элементы И 4-6, элемент РА ВНОЗНА Ч НОСТЬ 7, эле мент НЕ

8, триггер 9, информационные входы 1013, вхоц 14 переноса, управляющие входы 15 - 21, выход 22 переноса, выход

23 результата и синхровход 24, Схема коммутатора (фиг. 2 ) содержит элементы И 25 — 28, ИЛИ 29, HE 30 и 31, управляющие входы 32 и 33, информационные входы 34 — 37, выход 38.

Схема устройства работает следующим образом.

На информационные входы 10 — 13 устройства подаются значения сигналов: на вход 10 — сигнал A значения

ro разряда операнда А, на вход 11 сигнал A инверсного значения q --го разряда операнда А, на <вход 12 — сигнал ) +4 с выхода старшего разряда в И разрядном устройстве, на вход 13 — сигнал

Q < с выхода младшего разряца в И -разрядном устройстве. На вхоц 14 подается входной сигнал переноса Р„, с выхода 22 снимается фйходной сигнал переноса Р, а с выхода 23 — сигнал результата операции (или содержимое триггера). Настройка модуля на выполнение требуемой операции осуществляется с помощью схемы сигналов настройки

И. — И-т, подаваемых на управляющие входы 15 - 21 модуля. Результат операции записывается в триггер 9 при подаче на вход 24 синхросигнала T.

В таблице представлены реализуемые устройством операции и соответствующие коды настроек. При этом принято, что код содержимого триггера перед началом операции соответствует операнду

В, а код А — входному операнду.

Предлагаемый управляемый арифметический модуль выполняет все операции, реализуемые известным устройством, в то же время он имеет меньше управляющих входов (у известйого их девять управляющих входов, а у предлагаемого уг:тройства семь), кро; e того, у пего ком5 903865 6 мутатор является нес инхронизируемым, того, схема предлагаемого. управляемого что упрощает его конструкцию. Таким арифметического модуля является и образом, схема предлагаемого модуля яв- более быстроцействующей, так как в ляется более простой. В нем параметры ней глубина цепи входного сигнала синхросигнала не зависят от параметров S и сигнала обратной связи меньше, схемы, а определяются полностью типом чем у известного (в схеме известиспользуемого триггера. Это повышает, ного устройства в этих цепях croQ1 наряду с уменьшением сложности, падеж- дополнительные элементы равнозначность функционирования модуля. Кроме ности) .

Операция п. п

И6

1 И2 ИЗ

1 Запись А

2 Запись А

3 Инверсия В

4 АЧВ

О

О

АЧВ

АЧВ

АЧ В

О

АфВ

АфВ

А В

AÖВ

О

О . О

О О

О

О

10

О

О

1 l

О 0

1 1

12 А®В

13 А®В

14 А®В

О

О

l !

15 Сдвиг вправо

16 Сдвиг влево

17 А+В

0

О

А+ В

А+В

0

О

20

А+Й

А+В

0

21

0

22 Запись О

23 Запись 1

0 1 — -—

О дом результата модуля, информационные входы второго коммутатора являются управляющими входами модуля, выход элемента

ИЛИ является выходом переноса модуля, а его входы соединены с выходами элементов

И, первые входы которых подключены соответственно ко входу переноса устройства и выходу первого коммутатора, о т л и ч аю шийся тем, что, с целью упрощения, модуль содержит элемент HE и третий элемент И, выход которого соединен фор мула изобретения

Управляемый арифметический модуль, содержащий элементы РАВНОЗНАЧНОСТЪ и ИЛИ, два элемента И, триггер и два коммутатора, настроечные входы первого

SS из которых являются управляющими входами модуля, а информационные входы подключены к информационным входам устройства, выход триггера является выхо0 0

0 3, 0 1

О О

0 1

О 1

О 1

О

1 О

О

1 1

l О

0 1

l l

О О

1 О

О 1

О 0

903865 и со входом элемента ИЛИ, его первый вхоД входом первого элемента И и входом соединен с выходом первого коммутатора, элемента НЕ, а также с единичным вхоа второй вход объединен со вторым вхо- дом триггера, выход элемента I-IE соедом второго элемента И и является упра- динен с нулевым входом триггера, синвляюаим входом модуля, третьи входы g хровход триггера является синхровходом второго и третьего элементов H соедине- модуля, дополнительный информационный ны соответственно с прямым и инверсным вход модуля является информационным выходами триггера, а их четвертые и . входом первого коммутатора. пятые входы соединены соответственно Источники информации, с первым и вторым, третьим и четвертым О принятые во внимание при экспертизе информационными входами второго комму- 1. Авторское свидетельство СССР татора, выход которого соединен со вхо- % 487387, кл. Я 06 F 7/50, 1975. дом элемента РАВНОЗНАЧНОСТЬ, дру- 2. Авторское свидетельство СССР гой вход которого подключен ко входу по заявке Ъ 2682661/18-24 (153558 переноса модуля, а выход соединен со 15 кл. 9 06 F 7/50, 1978 (прототип).

Ур

Уд

Л ф /

8, ВНИИПИ Заказ 121/30

Тираж 731 Подписное

Филиал ППП Патент", г. Ужгород,ул. Проектная,4