Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()903972 (6I ) Дополнительное к авт. свна-ву

{22)Заявлено 08. 06. 79 (21) 2776317/18-24 (5l )IN. Кв.

G 11 С 1.1/00 с ярисоелинением заявки М (23) Приоритет Ъеударетеаеы6 «вн«тет

СССР ав Аеааи «зоеретених н открыт«й

Опубликовано 07.02.82. Бюллетень йе 5 (S3) тДК 681 327. .6(088.8) Дата опубликования описания 09. 02.82 (72) Авторы изобретения

Э.П. Калошкин, В.ll. Болдырев, Ю.И. Савот

Ю.П. Попов, E Х. Певитман, Е.А. Верников (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изорретение относится к запоминающим устройствам, выполненным в виде биполярных больших интегральных схем (БИС), и может быть использовано в современных ЦВИ и устройствах памяти.

Известны полупроводниковые оперативно-запоминающие устройства (ОЗУ), выполненные в виде БИС с матрицей запоминающих триггерных элементов, на основе биполярных переключающих транзисторов l 1).

Основные недостатки этих устройств - малый объем памяти и боль,шой размер кристалла, что обусловлено относительно большой площадью триггерного элемента. т5

Известно также оперативное запо", минающее устройство, содержащее мат ричный накопитель на триггерных ячейках памяти с двумя адресными шинами

20 в каждой строке, одна из которых подключена к соответствующему выходу де-. шифратора адреса, а другая - к соответствующему входу генератора выборки, и двумя разрядными шинами в каждом столбце, подключенными к соот- ветствующим выходам дешифратора разрядов и к эмиттерам эмиттерных повто рителей, коллекторы которых подключены к положительному полюсу источни ка питания, вход дешифратора разрядов подключен к одному выходу блока управления, управляющий выход " к одному входу выходного усилителя, другой выход блока управления подключен к другому входу выходного усилителя (23.

В этой схеме при выборке потенциал f адресных шин соответствующей строки определяется внутренним устройством дешифратора адреса, а потен циал разрядных шин Т определяется потенциалом на базе эмиттерного повторителя и внутренним устройством.дешифратора разрядов. Поскольку дешифратор адреса и дешифратор разрядов ра-: ботают независимо друг от друга, совершенно независимо друг от друга флуктуируют потенциалы У и Р . Обусловленная этим существенная нестабил ьност ь разности потенци алов между словарной и разрядной шинами является причиной возникновения в схеме эффекта ложного срабатывания (считывания из невыбранной ячейки или записи, в невыбранную ячейку).

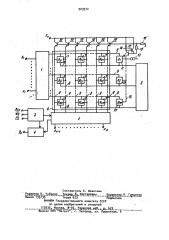

Цель изобретения - повышение быст родействия и надежности устройства, Указанная цель достигается тем, щ что устройство содержит в каждой строке матричного накопителя дополнительный инжекционный элемент памяти, эле мент согласования на транзисторе, доолнительный эмиттерный повторитель, елитель напряжения на резисторах и генератор тока, причем каждый дополнительный инжекционный элемент памяти подключен к адресным шинам соответствующей строки, к генератору тока и эмиттеру транзистора элемента .согласования, коллектор которого через резистор подключен к положительному полюсу источника питания и не- . посредственно - к базе транзистора дополнительного эмиттерного повторителя, база транзистора элемента согласования подключена к эмиттеру транзистора дополнительного эмиттерйого повторителя и через делитель на- 3 пряжения, средняя точка которого подключена к базам эмиттерных повторителей, — к шине нулевого потенциала, На чертеже изображена блок-схема устройства.

Предлагаемая большая интегральная схема оперативного запоминающего устройства включает дешифратор 1 ад реса, дешифратор 2 разрядов, блок 3 управления, выходной усилитель 4, генераторы 5 выборки и матричный на-. копитель б на триггерных ячейках па-. мяти из m строк и k столбцов триггерных ячеек 7 памяти. Ячейки каждой

j-ой строки снабжены двумя адресными шинами 8, одна из которых подключена к дешифратору 1 адреса, а другая - к генератору 5 выборки. Ячейки каждого - ro столбца снабжены двумя разрядными шинами 9, подключенными к соответствующим выходам дешифратора 2 разрядов и к эмиттерам эмиттерных. повторителей 10. В схему введе-ны элемент 11 согласования на транзисторе и дополнительный эмиттерный повторитель 12, генератор 13 тока, ss резистор 14 и делитель напряжения из резисторов 15 и 16. Кроме того, в каждую строку ячеек накопителя вве903972 ден дополнительный инжекционный элемент 17 памяти, полностью соответствующий половинке триггерной ячейки памяти. Элемент 17 снабжен разрядной шиной 18, подключенной к генератору 13 тока и к эмиттеру транзистора элемента 11. согласования. Коллектор транзистора элемента 11 согласования через резистор 14 выведен на положительный полюс источника питания. На этот же полюс выведен коллектор до-.

t полнительного эмиттерного повторитегня 12. База дополнительного эмиттер ного повторителя 12 подключена к коллектору транзистора элемента t I со,гласования, а база транзистора элемента 11 согласования и эмиттер дополнительного эмиттерного повторителя 12 через делитель напряжения, средняя точка которого подключена к базам эмиттерных певторителей--10>-к шине нулевого потенциала, При выборке строки дополнительный инжекционный элемент памяти передает потенциал выбранной строки на дополнительную разрядную шину 18. бина 18 находится в состоянии постоянной выборки за счет подключения к ней генератора 13 тока>и потенциал с нее через элемент 11 согласования передается на делитель напряжения. При этом эмиттерный повторитель 12 и резистор 14 служат для правильной трансля- ции потенциала дополнительной разрядной шины l8 на базы эмиттерных повторителей 10.

Таким образом, потенциал разрядной шины определяется потенциалом адресной шины. Колебания потенциала адресной шины вызывают соответствующие изменения потенциала разрядных шин. Нестабильность .разности потенциалов между адресной и разрядными шинами при этом существенно уменьшается, и значительно улучшается надежность работы схемы Быстродействие схемы возрастает за счет уменьшения перепада напряжений между адресными шинами вы" бранной и невыбранной ячеек. Экспериментально установлено, что использование предлагаемой схемы уменьшает вероятность ложного срабатывания на

503 и обеспечивает увеличение быстродействия на 204.

Предлагаемое изобретение черезвычайно важно с точки зрения его использо" вания при изготовлении большых и сверхбольших интегральных схем, при меняемых в оперативно-запоминающих

903972 устройствах вычислительных систем и в других областях народного хозяй. ства. Актуальность его обусловлена существенным увеличением быстродействия и надежности работы схемы.

Формула изобретения

Оперативное запоминающее устройство, содержащее матричныи накопит е тель на триггерных ячейках памяти с двумя адресными шинами в каждой стро. ке, одна из которых подключена к соответствующему выходу дешифратора адреса, а другая - к соответствующему входу генератора выборки, и двумя разрядными шинами в каждом столбце, подключенными к соответствующим выходам дешифратора разрядов и к эмиттерам эмиттерных повторителей, коллекторы которых подключены к положительному полюсу источника питания, вход деаифратора разрядов подключен к однр.му выходу блока управления, управляющий выход - к одному входу выходного усилителя, другой выход блока управления подключен к другому входу выходного усилителя, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит в каждой строке мат ри чного накопителя дополнительный инжекционный элемент памяти,элемент согласования на транзисторе,дополнительный эмиттерный повторитель, делитель напряжения на резисторах и генератор тока, причем каждый дополнительный инжекционный элемент памяти подключен к адресным шинам соответствующей строки, к генератору тока и эмиттеру транзистора элемента со-. гласования,. коллектор которого через резистор подключен к положительному полюсу источника питания и непосредственно - к базе транзистора дополнительного эмиттерного повторителя, база транзистора элемента согласования подключена к эмиттеру транзистора дополнительного эмиттерного Iloato» рителя и через делитель напряжения, средняя точка которого подключена к базам эмиттерных повторителей к ,шине нулевого потвнциала..

Источники информации, принятые во внимание при экспертизе

1. Патент С@А 1г 3636377, 340-174 2в,19722. н!ЕЕЕ International Papers.

ISSCC", 1976, ebr. 20, рр. 188-189 (прототип).

9039?2

Яц7

Ж

Составитель E. Левитиан

Редактор H. Чубелко Техоев Ж.„Кастелевич: Коорвктор, 4. Гриценко аказ 3 5 Тираж 623 Подписное .

ВНИИПИ Государственного комитета СССР ло делам изобретений и открытий .1I O)5,- Москва Ж-Я Раушская Hà0. 8. ЦД

Филиал ППП "Патент", г. Ужгород, ул. Проектная,