Запоминающее устройство с обнаружением отказавших блоков

Иллюстрации

Показать всеРеферат

- И. B. Огнев, Ю. А. Розанов, 6. М. Шам

О. В. Исаев и К. ф. Сарычев (72) Авторы изобретеиия (71) Заявитель

Московский ордена Ленина энергетическ институт (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ

ОТКАЗАВШИХ БЛОКОВ

Изобретение относится к запоминающим устройствам и может быт ь примене.но для создания полупроводниковых блоков памяти с локализацией отказов до уровня микросхем.

Известно. запоминающее устройство с обнаружением отказавших блоков, которое содержит полупроводниковые блоки памяти, схемы согласования, блок микропрограммного управления, схему сравнения, блок индикации Щ .

Недостатком этого устройства является то, что оно не позволяет диагностировать отказавшие элементы.

Наиболее близким к предлагаемому является запоминающее устройство, содержащее полупроводниковые блоки памяти (запоминающие микросхемы), дешифратор, блок адресных формирователей, блоки согласования, блок микропрограммного управления, схему

ИЛИ, схему сравнения, коммутатор, регистры неисправной строки и столбца соответственно и схему локализации ошибок (23.

Недостатком этого устройства является невысокий уровень локализации неисправностей, поскольку отсутству5 ет возможность определения номера неисправного адреса формирователя,разделения отказов адресных формирователей и формирователя режима, разрядных формирователей и усилителей с4итыва10 ния.

Цель и зобрет ени я - по вышение уро вня локализации неисправностей запоминающего устройства до элемента и

15 монолитного блока (микросхемы) .

Указанная цель достигается тем, что в запоминающее устройство с обнаружением отказавших блоков, содержащее полупроводниковые блоки памяти, адресные входы которых соединены с выходами адресных формирователей, а входы выборки - с выходами первого дешифратора адреса, вход которого и вход второго дешифратора адреса под3 903974 ключены к одним из адресных шин, блоки согласования уровней сигналов, первые входы и одни из выходов которых соединены соответственно с выходами и с информационными входами полупроводниковых блоков памяти, блок микропрограммного управления, адресные выходы которого подключены соответственно.к адресным шинам

I выход режима соединен с шиной управ- 10 ления и вторыми входами блоков согласования уровней сигналов, а информа° ционный выход - с третьими входами блоков согласования уровней сигналов, входной числовой шиной и первым вхо- 15 дом схемы сравнения, второй вход конторой подключен к другим выходам блоков согласования уровней сигналов и выходной числовой шине, а выход - ко входу первого регистра и элемента го

ИЛИ, выход которого соединен со входом стробирования второго дешифратора адреса, выход которого подключен ко входу второго регистра, вход установки регистров соединен с шиной 25 сброса, введены третий регистр, элементы И-НЕ, элементы НЕ, элемент И и группа элементов И, причем одни из входов первого и входы второго элементов И-НЕ подключены соответствен- 5О но к прямым и к инверсным выходам первого регистра, одни из входов третьего и входы четвертого элементов

И-НЕ соединены соответственно с прямыми и с инверсными выходами второго регистра, первые входы элементов И группы подключены к одним из прямых выходов первого и второго регистров соответственно, а выходы являются соответственно первым и вторым выхо- 4в дами устройства, второй вход одного из элементов И группы соединен с выходом первого элемента И-НЕ, входом первого элемента НЕ и первым входом элемента И, выход которого подключен ко второму входу другого элемента И группы, второй вход элемента И соединен с выходом второго элемента И-НЕ, третий вход - с выходом третьего элемента И-НЕ и входом. второго элемента

НЕ, четвертый вход - с выходом четвертого элемента И-НЕ, а пятый входс другими входами первого и третьего элементов И-НЕ и выходом третьего элемента НЕ, входы трет ьего регистра подключены к другим адресным шинам, вход ст робирования соединен с выходом элемента ИЛИ,а прямые выходы подключены ко входам пятого элемента И-НЕ,вы4 ход которого соединен со входом третьего элемента HE,èíâåðñíûå выходы трет ьего регистра являются третьим выходом устройства, выходы первого элемента

НЕ, элемента И, второго элемента НЕ и пятого элемента И-НЕ являются соответственноо четвертым, IlR fbIM шестым и седьмым выходами устройства.

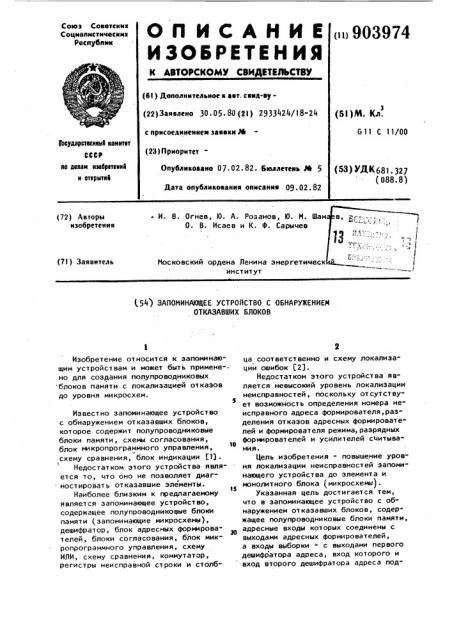

На чертеже изображена структурная схема устройст ваУстройство содержит полупроводниковые блоки 1 памяти, организованные в матрицу, первый дешифратор 2 адреса, группу адресных формирователей 3, адресные шины 4 и 5, блоки 6 согласо,вания уровней сигналов, блок 7 микропрограммного управления, схему 8 сравнения, элемент ИЛИ 9, второй дешифратор 10 адреса, первый 11, второй 12 и третий 13 регистры, шину 14 управления, входные 15 и выходные 16 числовые шины, первый-пятый элементы

И-НЕ 17 - 2 1, элемент и 22, первый

23.1, второй 23.2 и третий 23.3 weменты НЕ и группу 24 элементов И. На чертеже обозначены выходы 25-31 устройства, служащие для выдачи сигналов об отказе, и шина 32 сброса.

Одни из входов первого:17 и входы второго 18 элементов И-НЕ подключены соответственно к прямым и к инверсным выходам регистра 11. Одни из входов третьего 19 и входы четвертого 20 элементов И-НЕ соединены соответственIo с прямыми и с инверсными выходами регистра 12. Первые входы элементов

И группы 24 подключены к одним из прямых выходов регистров 11 и 12 соответственно, а выходы являются сооТ ветственно первым 25 .и вторым 26 выходами устройства. Второй вход одного из элементов И группы 24 соединен с выходом элемента И-НЕ 17, входом элемента HE 23. 1 и первым входом элемента И 22, выход которого подключен ко второму входу другого элемента И группы 24. Второй вход элемента И 22 соединен с выходом элемента И-НЕ 18, третий вход — с выходом элемента И-НЕ

20 и входом элемента НЕ 23.2, четвертый вход - с выходом элемента И-HE

20, а пятый вход — с другими входами элементов И-НЕ 17 и 19 и выходом элемента НЕ 23. 3. Входы регистра 13 подключены к другим адресным шинам 5, вход стробирования соединен с выходом элемента ИЛИ 9, а прямые выходы подключены ко входам элемента И-НЕ

21, выход которого соединен со вхо5 903974

6 дом элемента HE 23.3. Инверсные вы- мяти - тестовое слово, а по управляюходы регистра 13 являются третьим щей шине 14 - сигнал разрешения запивыходом 27 устройства, выходы элемен- си тестового слова по указанному та НЕ 23. 1, элемента И 22, элемента адресу в блоки I памяти. При считыНЕ 23.2 и элемента И"НЕ 21 являются g ванин блок 7 формирует сигнал считысоответственно четвертым 28, пятым вания и адрес, которые поступают со-.

29, шестым 30 и седьмым 31 выходами ответственно на информационные входы устройства. Одни из адресных шин 4 по шине 14 ) и на адресные входы и соответствуют номерам столбцов матри- входы выборки блоков 1 памяти (no цы полупроводниковых блоков 1 памяти, 1о шинам 4 и 5). Считанная информация а другие 5 - адресам элементов памя- поступает на схему 8 сравнения, где ти внутри блоков 1 памяти. происходит поразрядное сравнение ее

Разрядность регистра 13 и количе-. с соответствующим тестовым словом, ство входов элемента И-НЕ 21 равно поступающим из блока 7. Схема 8

К =1о N! 1з сравнения в каждом разряде вырабатыгде N - количество элементов памяти вает сигнал "0", если произошло совв полупроводниковом блоке 1 памяти. падение, и "1" - в противном случае.

Разрядность регистра 11 равна коли Результаты сравнения записываются в честву строк, а регистра 12 - коли- регистре 11. В случае несовпадения честву столбцов матрицы. блоков 1 па- щ элемент ИЛИ 9 вырабатывает сигнал . мяти. стробирующий дешифратор 10, и в

Устройство работает следующим об- Разряд Регистра 12, соответствующий разом.,адресу проверяемого столбца, посту0 исходном состоянии во все разря- пающему по шинам 5 из блока 7, запи" ды регистров 11- 13 записывается "0" при подаче сигнала по шине 32 сбро- Одновременно по сигналу с элемен" са. g устройстве производится цикли- та И!1И 9 стРобиРУющемУ РегистР 13 ческая перезапись набора текстовых . в него записываетсЯ текУщий адРес с слов по всем адресам. Адреса и набор адРесных шин 5 блока 7. тестовых слов задаются блоком 7. Ко- 30 рассмотрим неисправности адресных личество тестовых слов должно быть формирователей 3 типа постоянный "0"

ll ll не менее трех для определения отка- или 1 на входе или выходе. Для алгоза адресных формирователей 3, так Ритма Работы устройства (табл. 2) как в этом случае по адресам, крат- >Т< пРиводит к искажению записанной ным двойке, записываются разные тес-, З и формации в группе элементов блоков товые слова (см. табл. 1), 1 памяти, кратной степени 2. Например, при отказе адресного формироваОсобенностью последовательности теля первого разряда адреса несовпатестовых слов является то, что каж-, дение записанного и считываемых тес" дый разряд хотя бы один раз переклю- товых слов произойдет по 0,2,4,6 и чается из одного состояния в другое. т.д. адресам, при отказе адресного

8 каждом такте работы устройства формирователя второго разряда - по производятся последовательно цикл 0,1,4,5,8,9 и т.д. адресам. Представопераций записи последовательности ляя последовательности адресов в тестовых слов и цикл операций считы- двоичной форме для nepsoro (000, 010, 45 вания. Число тактов равно количеству 100, 110) и второго (0000, 0001, тестовых слов, при этом в каждом 0100, 0101, 1000, 1001) случаев и последующем такте осуществляется за- - сравнивая поразрлдно последовательпись и считывание последовательности ности, обнаружим, что в первом притестовых слов, циклически сдвинутой. мере переключаются из "0" в "1" все на один разряд по сравнению с преды- разряды, кроме первого, во втором

50 дущим. Алгоритм работы на примере примере - все, кроме второго разряда. запоминающего устройства емкостью Аналогичные результаты могут быть восемь слов проиллюстрирован в,получены для всех разрядов адреса. табл. 2. Таким образом, при отказе адресного

Из блока 7 по адресным шинам 4 и 5 з5 формирователя 3 все инверсные выходы на дешифратор 2 адреса и формирова- регистра 1,3 переключаются из "1" в тели 3 поступает адрес по шинам 15 "0", кроме выхода, соответствующего

Э на информационные входы блоков 1 па- отказу.

903974

Т а б л и ц а 2

После прохождения теста номера .строк,где зафиксированы отказы, накапливаются в регистре 11, соот ветствующие этим отказам номера столбцовв.регистре 12, номер отказавшего ад» ресного формирователя 3 — в регистре

13.

Определение типа отказавшего блока по содержимому регистров проводится согласно табл. 3. В ней указаны 1о значения прямых выходов соответствующих регистров. В каждом строке табл. 3 задаются необходимые условия, которые должны выполняться одновременно. 35

Тип отказа фиксируется логической единицей на соответствующем из выходов 28 - 31, а номер отказавшего блока - на выходах 25 - 27 устройства.

Для первых трех типов отказов (табл. 3) во всех разрядах регистра

13 содержатся "1", в результате чего на инверсных выходах регистра 13 (т.е. на выходе 27 устройства) и на выходе элемента И-НЕ 21 присутствуют

"0".

При отказе дешифратора 2 адреса содержимое регистра 11 - все "1".

Логический ноль на выходе элемента

И-НЕ 17 запрещает выдачу содержимого регистра 11 на выход 25 и через элеь ент И 22 на выход 26 устройства, а через элемент НЕ 23.1 устанавливает на выходе 28 устройства единичное состояние. При этом на выходе 30 уста3S навливается нулевое состояние. При отказе блоков 6 согласования уровней сигналов содержимое регистра 12 — все

"1". Логический ноль на выходе элемента И-НЕ 19 через элемент И 22 заю лрещает выдачу содержимого регистра

12 на выход 26, а логическая единица с выхода элемента И-НЕ 17 (в регистре 11 есть хотя бы один "0") разрешает выдачу на выход содержимого регистра 11, пердставляющего номер отказавшего блока 6 (микросхемы).

Сигнал логического ноля и логической единицы на выходе элементов

И-НЕ 19 и 17 устанавливают на выходе

30 сигнал "1", а на выходах 28 и 29сигнал "0".

При отказах полупроводниковых блоков памяти выходы элементов И-НЕ 1720 в соответствии с содержимым регистров 11 и 12 (табл. 3) переключаются в состояние логической единицы.

Логическ- единица на выходе элемента И 22 переключает выход 29 в состояние "1", одновременно разрешая выдачу содержимого регистра 12 на -выход 26, а логическая единица с выхо" да элемента И-НЕ 17 разрешает выдачу содержимого регистра 11 на выход 25.

Таким образом>номер отказавшего блока памяти задается содержимым регистром

11 и 12.

При отказе адресных формирователей

3 выход элемента И-НЕ 21 в соответствии с содержимым регистра 13 устанавливает нулевые сигналы на выходах 2, 26, 28 - 30, а сигналы на выходе 27 определяются содержимым регистра 13, что позволяет определить номер отказавшего адресного формирователя 3 и, следовательно, номер соответствующей микросхемы.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает локализацию неисправностей до уровня элемента и монолитного блока (микросхемы) .

Т а б л и ц а 1

903974

)О

Таблица) Тип от казавшего блока

Содержимое регистров

Дешифратор 2 адреса

Есть хотя бы один "0"

Все "1"

Все "1"

Блоки б согласования уровней сигналов

Ест ь хот я бы один "О". Все "1""

Все "1"

Полупроводни ковые блоки 1 . памяти

Есть хотя бы одна "1", но не все "1"

Адресные формирователи 3

Есть хотя бы один "0"

-Bce "1""

Все "1"

Формула изобретения

Запоминающее устройство с обнаружением отказавших блоков, содержащее полупроводниковые блоки памяти, адресные входы которых. соединены с выхо- дами адресных формирователей а входы выборки - с выходами первого дешифратора адреса, вход которого и вход второго дешифратора адреса подключены к од- З@ ним из адресных шин,блоки согласования уровней сигналов, первые входы и од-. ни из выходов которых соединены соответственно с выходами и с информационными входами полупроводниковых блоков памяти, блок микропрограммного управления, адресные выходы которого подключены соответственно к адресным шинам, выход режима соединен с шиной управления и вторыми входами блоков согласования уровней. сигналов, а информационный выход - с третьими входами блока согласования уровней сигналов, входной числовой шиной и первым входом схемы сравнения, второй вход которой подключен к другим выходам блоков согласования уровней сигналов и выходной числовой шине, а выходко входу первого регистра и элемента

ИЛИ, выход которого соединен со входом стробирования второго дешифратора адреса, выход которого подключен ко входу второго регистра, вход установки регистров соединен с шиной сброса, о т л и ч а ю щ е е с я тем„

I И что, с целью повышения уровня локали-. зации неисправностей устройства, оно содержит тре ий регистр, элементы

„И-НЕ, элементы НЕ, элемент И и групЕсть хотя бы одна "1", но не все "1" Все "1" пу элементов И, причем одни из входов первого и входы второго элементов

И-НЕ подключены соответственно к прямым и к инверсным выходам первого регистра, одни из входов третьего, и входы четвертого элементов И-HE соединены соответственно с прямыми и с инверсными выходами второг регистра, первые входы элементов И группы подключены к одним из прямых выходов первого и второго регистров соответственно, а выходы являются соответственно первым и вторым выходами устройства, второй вход одно" го из элементов И группы соединен с выходом первого элемента И-НЕ, входом первого элемента . НЕ и первым входом элемента И, выход которого подключен ко второму входу другого элемента И группы, второй вход элемента И соединен с выходом второго элемента И-НЕ, третий вход - с выходом третьего элемента И-НЕ и входом второго элемента НЕ, четвертый входс выходом четвертого элемента И-НЕ, а пятый вход - с другими .входами первого и третьего элементов И-НЕ и выходом третьего элемента НЕ, входы третьего регистра подключены к другим адресным шинам, вход стробирования соединен с выходом элемента ИЛИ, а прямые выходы подключены ко входам пяroro элемента И-НЕ, выход которого соединен со входом третьего элемента

НЕ, инверсные выходы третьего регистра являются третьим выходом устройства, выходы первого элемента НЕ, элемента И, второго элемента НЕ и пятого элемента И-НЕ являются соот11 ветственно четвертым, пятым, шестым и седьмым выходами устройства.

Источники информации, принятые во внимание при экспертизе

903974

1.Ерошин B.И, Методы, методика и аппаратура для функционального контроля ОЗУ на МОП-структурах. Челябинск,1 977.

2. Патент США М 394060 1, кл. 235153 АС, 1978 (прототип).

Корректор А. Дзят ко

Подписное

Составитель Т. Зайцева

Рецактоо Н. Ч белко Texpeg " ° "адь

Заказ 134/36 Тираж 623

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-Д Раушская наб. g. 4/g

Филиал ППП "Патент, г. Ужгород, ул. Проектная,4