Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ссиоэ Советскнк

Социалистические

Республик и 9()3980

Ф (61) Дополнительное к авт. свнд-ву (53) N. Кл .

G 11 С 11/40 (22) Заявлено 23.01 80 (21) 2873460!18-24 с присоединением заявки М

9вудврстеекны11 квинтет

СССР оо делам кзабретенкв я открытий (23) ПрнорнтетОпУбликовано 07.02.82. Бюллетень J4 -5 (53) УД К 681.327..67(088.8) Дата опубликования описания IO.02.82 (72) Авторы

Е. Б. Механцев, P. С, Кильметов и A. И. Сухоруков (54) ЗАПОМ ИНАЮКИИ ЭЛЕМЕНТ

Изобретение относится к области вычислительной техники и предназначено дпя использования в монолитных интегральных запоминающих устройствах различного назначения.

Известен триггер на полевых тран5 зисторах, который может быть использован как элемент памяти при построении матриц запоминающих устройств большой емкости (1

Недостатками такого элемента памяти является то, что он содержит два источника питания, потребляет значительную мощность в статическом режиме и содержит большое количество шин и полевых

15 транзисторов.

Наиболее близким по технической сущности к предлагаемому устройству является другой, более простой, микромощный триггер на полевых транзисторах. Микромошный триггер (элемент памяти) на полевых транзисторах содержит четыре последовательно соединенных взаимодо полняюших полевых транзистора и две шины питания. Последние подключены к стокам крайних транзисторов, затворы этих же транзисторов соединены;вместе и подключены к обшей точке внутренних транзисторов, которая служит выходной шиной. Затворы внутренних транзисторов подключение к соответствующим шинам источника питания. Для записи информации в элемент памяти используются два дополнительных полевых транзистора, которые подключены параллельно крайним транзисторам, а их затворы подключены к -информационным шинам. Этот элемент памяти потребляет очень малую мощность при хранении информации и имеет достаточно высокое быстродействие (23

Однако он имеет большое количество шин (две шины питания, две входные и одну выходную) и сложен в управлении.

При создании функциональных запоминаю ших узров большой емкости в интеграль ном исполнении на таких элементах твеличиваются площадь на кристалле и пара980

3 903 зитные емкости, снижается,быстродействие и надежность в работе.

Цель изобретения — упрощение запоминающего элемента и повышение его быстродействия за счет уменьшения паразитных емкостей.

Указанная цель достигается тем, что в запоминающем элементе, сбдержащем два полевых и -канальных транзистора и три полевых р -канальных транзистора, причем затвор первого и -канального транзистора соединен со стоками второго и -канального и первого р -канального транзисторов и с затвором второго р -канального транзистора, сток котороk го соедйнен с истоком третьего р -канального транзистора и с первой шиной питания, исток, второго р-канального транзистора соединен со стоком второго и -канального транзистора, исток первого л -канального транзистора соединен со стоком первого р -канального транзистора, затвор которого соединен со стоком первого и -канального транзистора и со второй шиной питания, сток третьего р -канального транзистора соединен с затвором второго и -канального транзистора, а затвор третьего р -канального транзистора подключен ко второй шине питания.

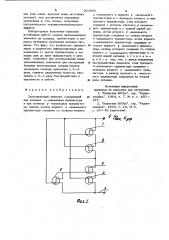

На фиг. 1 изображена принципиальная схема конкретного исполнения запоминающего элемента; на фиг. 2 — временные диаграммы работы, Запоминающий элемент содержит пять полевых транзисторов: первый транзистор

1 и -типа, первый транзистор 2 р -типа, второй транзистор 3 и -типа, второй транзистор 4 р --тийа, третий транзистор 5 р -типа — и две шины 6 и 7 питания подключенные соответственно к стокам крайних транзисторов. Шины питания совмещены с шинами управления.

Затворы крайних транзисторов соединены вместе и подключены к общей точке транзисторов 2 и 3, затвор первого транзистора р -типа подключен к-шине 6 нитания, а в цепь затвора второго транзистора и -типа включен третий транзистор 5

Р -типа, сток которого соединен с затвором второго транзистора и -типа, исток — с шиной 7 питания, а затвор - с шиной 6 питания. Напряжение отсечки третьего транзистора 5 р -типа выбрано таким, что оно превышает сумму напряжений отсечки лары транзисторов 1 и 2 и транзисторов 3 и 4.

Запоминающий элемент работает следующим образом..

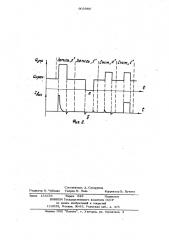

Транзисторы 1 и 2, 3 и 4 образуют попарно приборы с отрипательным сопГотивлением — Л -LtHoltbI, включенные последовательно. Л -диоды выбраны таким образом, что максимальный ток верхнего диода больше максимального тока нижнего диода. В режиме хранения информации

10 на шине 6 поддерживается положительный потенциал (U

И: -диода. Коду 1" соответствует состояgp ние, при котором верхний Л -диод открыт, а нижний закрыт. Ток в цепи также равен току утечки запертого Л -диода.

Таким образом, в статических состояниях

О и 1" ток в цепи запоминающего ц5 элемента практически не протекает и потребляемая мощность составляет малую величину.

При записи кода "О" в шину 6 подается положительный импульс, величина

ЗО которого превышает напряжение отсечки третьего транзистора 5 р -типа. Транзистор 5 закрывается и вольт-амперная характеристика нижнего Л -диода деформируется в пентодную, а напряжение на

35 его аноде уменьшается до нуля. При снятии импульса запоминающий элемент сохраняет это состояние. Для записи кода 1 в шине 6 потенциал уменьшается от "хрен до нуля, при этом за счет

4 того, что максимальный ток верхнего

A. -диода больше максимального тока нижнего Л -диода, при снятии импульса потенциал на аноде нижнего - -диода увеличивается до Охр щ, и запоминающий элемент сохраняет это состояние. й

Считывание информации осуществляется подачей импульса положительной полярности в шину 6, амплитуда которого выбирается из условия нераэрушающего считывания О чищ С О ц(р при этом в Вы» ходной цепи запоминающего элемента течет большой информационный ток, если хранится код 1", и малый, если хранится код "0

Таким образом, использование в запоминающем элементе третьего транзистора

-типа позволяет уменьшить общее количество шин до минимального значе5 9039 ния (две шины, включая шины источника питания), чем достигается упрощение управления и, тем самым, получение положительного технико-экономического эффек та. 5

Лабораторные испытания показали устойчивую работу модели запоминающего элемента на полевых транзисторах в широком интервале изменения входных сигналов. Тот факт, что количество транзис«30 торов и количество информапионных шин уменьшено (с шести транзисторов и четырех шин до пяти транзисторов и двух шин), позволяет при использовании таких запоминающих элементов для построения 1S больших интегральных матриц памяти уменьшить площадь кристалла в 3-4 раза, снизить паразитные емкости, увеличить в 2 -3 раза быстродействие и надежность в работе. 20

80 6 -канального и первого р -канального транзисторов и с затвором второго р -канального транзистора, сток которого соединен с истоком третьего р -канального транзистора и с первой шиной питания, исток второго р -канального транзистора соединен со стоком второго и -канального транзистора, исток первого и -канального транзистора соединен со стоком первого р -канального транзис-. тора, затвор которого соединен со стоком первого и »канального транзистора и со второй шиной питания, о т л и ч а юшийся тем, что, с целью повышения быстродействия элемента, сток третьего

Р -канального транзистора соединен с затвором второго и -канального транзистора, а затвор третьего р --канального транзистора подключен ко второй шине питания.

Формула изобретения

Запоминающий элемент, содержащий 25 два полевых и -канальных транзистора и три полевых р -канальных транзистора, причем затвор первого и -канального .транзистора соединен со стоками второго

Источники информапии, принятые во внимание при экспертизе

1. "Известия ВУЗов", сер. "Радиотехника", 1964, т. 7, % 4, с. 430437.

2. "Известия ВУЗов, сер. "Радиотехника", 1976, т. 19, ¹ 9, с. 39 — 45 (прототип) .

903980

Составитель A. Сухоруков

Редактор Н. Чубелко Техред M. Надь Корректор В. Бутяга

Заказ 134/36 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул, Проектная, 4