Репрограммируемое постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

O fl N C A H N 6 (и 903984

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Севвтскнк

Сециапистичвскик рвсяубпии (б f ) Дополнительное к авт. свид-ву (22) Завалено 13. 06. 80 (21) 2940828/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 07. 02. 82Бюллетеиь М5

Дата опубликования описания 09. 02. 82 (51)М. Кл.

G 11 С 17/00

9сумрстеивм6 кеивтвт

CCCP

Ю дави взобретевкв я открытка (53) УДК 681,327. .66(088.8) С. И. Иальченко, А. Н. Иванов, В. П. Анд

П. С. Приходько и 10. И. Щетини (72) Авторы изобретения (71) Заявитель (54) РЕПРОГРАИИИРУЕИОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО

Изобретение относится к постоянным запоминающим устройствам (ПЗУ) .

Известны ПЗУ, содержащие адресные формирователи и дешифраторы, накопитель с адресными и разрядными шинами разрядные формирователи, дополнитель ные элементы памяти (ЭП) и шины управления (13 и L23.

Известно ПЗУ, в котором с целью проведения функциональной проверки

1а кодированием информации в дополнительных(тестовых) ЭП, последние введены в каждую разрядную шину, причем все

ЭП объединены дополнительной адрес- ной шиной L3).

Недостатком известного устройства является отсутствие возможности функциональной проверки электронного обрамления накопителя без наличия ЭП в основном (или дополнительном) поле накопителя. Данное условие обязательно при контроле электронного обрамления в микросхемах репрограммируемых постоянных запоминающих устройств

2 (РПЗУ}. В микросхемах РПЗУ некоторые виды элементов памяти могут быть из". готовлены лишь на последней стадии производства, .после установки кристаллов с исправным электронным обрамлением в корпус (например, при использовании ЭП на основе стеклообразных полупроводников) .

Цель изобретения - повышение на" дежности устройства путем обеспечения возможности функциональной проверки электронного обрамления.

Указанная цель достигается тем, что в устройство введены дополнительные контрольные адресные и разрядные формирователи, группы дополнительных кон трольных элементов памяти, причем входы дополнительных контрольных ад-. ресных формирователей подключены к выходам соответствующих адресных ин-. верторов одной из групп, а выходык одним из входов дополнительных контрольных элементов памяти одной из групп, другие входы которых подклю"

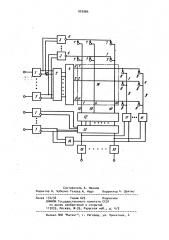

РПЗУ содержит адресные инверторы 1, адресный дешифратор 2, дополнительные контрольные адресные формирователи 3, адресные формирователи 4, адресные шины 5, дополнитель20 ные адресные шины 6, дополнительные контрольные элементы 7 и 8 памяти, дополнительные разрядные шины 9, разрядные шины 10, дополнительные

25 контрольные разрядные формирователи

11, разрядные формирователи 12, разрядный дешифратор 13, контрольный формирователь 14 разрешения выборки, усилители 15 считывания, накопитель 16.

Для контроля электронного обрам ления накопителя РПЗУ необходимо и достаточно убедиться в отсутствии замыканий и обрывов адресных и разрядных шин 5 и 10, так как отказ любого компонента электроники обрамления разрядной и адресной части можно интерпретировать как обрыв или замыкание соответствующих шин. Для контроля целостности и незамкнутос- 40 ти шин используются дополнительные контрольные ЭП 7 и 8 контрольных адресных шин 6 и контрольных разрядных шин 9. Дополнительные контрольные ЭП, например, могут быть выполнены в виде диодов, соединенных последовательно с резисторами, сопротивление которых соответствует сопротивлениям состояния "0" и "1" основных

ЭП. В процессе изготовления микросхе-50 мы РПЗУ в ЭП 7 и 8 путем изготовления резисторов с соответствующим сопротивлением кодируется информация, причем в группах ЭП 7, расположенных на разрядных шинах 10, фик- 55 сируются все возможные комбинациикода, разрядность которого соответствует числу элементов в группе (числу

3 90398 чены к разрядным шинам накопителя, одни из входов дополнительных контрольных разрядных формирователей соединены с выходами соответствующих усилителей считывания, другие - с выходами контрольного формирователя разрешения выборки, выходы дополнительных контрольных разрядных формирователей подключены к одним из

У входов дополнительных контрольных 10

„ элементов памяти другой группы, дру гие входы которых подключены к адресным шинам накопителя.

На чертеже изображена схема устройства. дополнительных адресных шин 6), в группах ЭП 8, расположенных на адресных шинах 5, закодированы все возможные комбинации с разрядностью

1 соответствующей числу элементов в группе (числу дополнительных разрядных шин 9) . При подобном кодировании дополнительных ЭП и при информационном объеме накопителя N=mxn количество 1 дополнительных адресных шин б составит

1 =log m, а количество k дополнительных разрядных шин 9 равно

k=log n, 2. где и и m соответственно информациI онная емкость и разрядность накопителя (число адресных и разрядных шин) .

При контроле целостности и незамкнутости разрядных шин 10 производится поочередный выбор дополнительных адресных шин 6 путем включения контрольных формирователей 3 от соответствующих адресных инверторов

1 (адресные шины 5, формирователи

4 и дешифратор 2 отключены вне зависимости от входного кода адреса) .

При поочередном выборе каждой шины б выбираются соответствующие разрядные шины 10 путем подключения их через разрядные формирователи 12 и дешифратор 13 к усилителям 15 чтения. Код, снимаемый с усилителей 15, сравнивается с эталонным. Совокупность всех считываемых кодов такова, что создаются условия одновременного чтения разнородной информации ("0" и "1") во всех разрядных шинах 10, что гарантирует обнаружение обрыва любой из них и любого их взаимного замыкания.

При контроле целостности и незамк-. нутости адресных шин 5 производится их поочередный выбор посредством формирователей 4, дешифратора 2 и соФ ответствующих инверторов 1. В разрядной части дополнительные шины 9 подключены к усилителям 15 через контрольные формирователи 11, управляемые от контрольного формирователя

14 разрешения выборки (разрядные шины

10, формирователи 12 и дешифратор 13 отключены вне зависимости or входного кода адреса) . Код,снимаемый с усилителей 15, сравнивается с эталонным, причем для камдой из шин 5 считывается характерный код, что гарантирует

5 9039 обнаружение любых обрывов и замыканий адресных шин 5.

Применение предлагаемого устрой- ства позволяет осуществлять контроль исправности электроники обрамления

Г микросхемы перед нанесением элементов памяти, что позволяет осуществлять .контроль выхода годных на более ранних стадиях производства микросхем

РПЗУ, уменьшая затраты на проведение 1О контроля выхода годных.

Формула изобретения

Репрограммируемое постоянное за-. поминающее устройство, содержащее группы адресных инверторов, причем входы адресных инверторов групп . являются входами устройства, выходы щ адресных инверторов одной из групп подключены к входам адресного дешифратора, выходы последнего адресного инвертора данной группы подключены к входам контрольного адресного фор- 2s мирователя, выходы адресных инверторов другой группы подключены к одним из входов разрядного дешифратора, другие входы которого соединены с выходами усилителей считывания, выходы зв последнего адресного инвертора данной группы подключены к входам контрольного формирователя разрешения выборки, выход которого соединен с одним из входов контрольного разрядного форми- з рователя, другой вход которого подключен к выходу соответствующего усилителя считывания, выходы адресного и разрядного дешифраторов подключены соответственно через адресные и раз-. рядные формирователи к адресным и разрядным шинам накопителя, контроль84 6 ные элементы памяти, подключенные к адресным и разрядным шинам накопителя и к контрольным адресным и разрядным шинам, которые, соединены соответственно с выходами контрольного адресного и разрядного формирователей, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены дополнительные контрольные адресные и раз" рядные формирователи, группы дополнительных контрольных элементов памяти, -причем входы дополнительных контрольных адресных формирователей подключены к выходам соответствующих адресных инверторов одной из групп, а выходы - к одним из входов дополнительных контрольных элементов памяти одной из групп, другие входь. которых подключены к разрядным шинам накопителя, одни из входов дополнительных контрольных разрядных формирователей соединены с выходами соответствующих усилителей считывания, другие - с выходами конт-. рольного формирователя разрешения выборки, выходы дополнительных контроль" ных разрядных формирователей подключенЫ к одним из входов дополнительных контрольных элементов памяти другой группы, другие входы которых подключены к адресным шинам накопителя.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

11 572849, кл. G 11 С 17/00, 1975.

2. Авторское свидетельство СССР

11 595792, кл. G ll C 11/34, 1976.

3. Авторское свидетельство СССР

N 711634, кл. G 11 С 17/00, 1978 (прототип).

903984

Составитель А. Иванов

Редактор Н ° 4убелко Техред M ° Надь Корректор A. Лзятко

Заказ 134/36 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4