Устройство для контроля и коррекции адресных сигналов для памяти последовательного действия

Иллюстрации

Показать всеРеферат

вявитель (g4) УСТР0АСТВО ДЛЯ КОНТГОЛЯ И КОРРЕКЦИИ АДГЕСНИХ

СИГНАЛОВ ДЛЯ ПАНЯТИ ПОСЛЕДОВАТЕЛЪНОГО ДЕЙСТВИЯ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля адресных сигналов, которое содержит регистр адреса, шифратор и схему сравнения. В этом устройстве конт" роль правильности обращения по заданному адресу осуществляется путем сравнения контрольного кода адреса. по некоторому модулю, поступающему одновременно с кодом адреса на регистр адреса, с контрольным кодом адреса, полученным на выходе шифратора кода адреса Г13 .

tS

Недостатком известного устройства является большой объем аппаратуры и невозможность коррекции неправильно выбранного адреса.

Наиболее близким к предлагаемому является устройство для контроля выборки адресов, содержащее последовательно соединенные формирователь продвигающих импульсов, регистр синхроимпульсов, усилитель считывания синхроимпульсов, счетчик синхроимпульсов, блок сравнения, второй вход которого соединен с выходом регистра адреса, и блок местного управления, причем выход формирователя продвигающих импульсов соединен также последовательно с маркерным регистром, усилителем считывания маркера и со вторым входом счетчика синхроимпульсов Г2J.

Недостатком известного устройства является отсутствие контроля правильности выбора адреса и невозможность его коррекции, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля и коррекции адресных сигналов для памяти последовательного действия, содержащее регистр адреса, формирователь продвигающих импульсов, регистр иар903989 кера, регистр синхроимпульсов, усилитель синхроимпульсов, усилитель маркерных и»пульсов, счетчик синхроимпульсов, первую схему сравнения и блок управления, причем выход формиро 3 вателя продвигающих импульсов подключен ко входам регистра синхрои»пульсов и регистра маркеров, выходы которых подключены соответственно ко входам усилителя синхроимпульсов и 1О усилителя маркерных сигналов, выходы которых соединены соответственно с первым и вторым входами счетчика синхроимпульсов, входы первой схемы cpasнения соединены соответственно с первым выходом счетчика синхроимпульсов и выходом регистра адреса, а выход подключен к одному из входов бло а управления, введены дешифратор, торая схема сравнения и счетчик npot- yi двигающих импульсов, входы которого подключены соответственно к выходам усилителя маркерных импульсов и формирователя продвигающих импульсов, выходы - к первым входам второй схемы сравнения и дешифратора, второй и третий входы которого соединены соответственно с выходом второй схемы сравнения и вторым выходом счетчика синхроимпульсов, одни из выходов дешифратора являются управляющими выходами устройства, другой выход подключен к первому входу счетчика синхроимпульсов, первый выход которого подключен ко второму входу второй схемы

3$ сравнения.

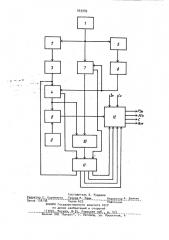

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит формирователь 1 продвигающих импульсов, регистр 2 синхроимпульсов, усилитель 3 синхроимпульсов, счетчик 4 синхроимпульсов, регистр 5 маркера, усили-. тель 6 маркерных импульсов, счетчик 7 продвигающих импульсов, первую схему 8 сравнения, регистр 9 адреса, вторую схему !О сравнения, дешифратор 11 и блок 12 управления.

Входы счетчика 7 подключены соответственно к выходам усилителя 6 и

50 формирователя 1, а выходы - к первым входам схемы 10 сравнения и дешифра" тора 11, второй вход которого соеди" нен с выходом схемы 10 сравнения, второй вход которой подключен к первому выходу счетчика 4, второй выход которого соединен с третьим входом дешифратора 11. Одни из выходов дешифратора 11 являются. управляющими

4 выходами устройства (соединены со входами блока t2), другой выход подключен к первому входу счетчика 4, второй вход которого соединен с выходом усилителя 6 °

Устройство работает следующим образом.

Перед началом работы счетчики 4 и

7 находятся в нулевом состоянии, а маркер находится на выходе регистра 5. В регистре 9 хранится код адре" са числа, с которого следует начать считывание (запись) . При пуске устройства маркерный импульс через усилитель 6 поступает на одни из входов счетчиков 4 и 7, разрешая прохождение соответствующих импульсов на их другие (,счетные) входы.

Каждый синхроимпульс соответствует одной адресной позиции, так что состояние счетчика 4 совпадает с адресом числа, которое в данный момент находится в зоне считывания. Этот адрес хемой 8 сравнения сравнивается с адесом, хранимым в регистре 9. При codпадении адресов в счетчике 4 и ре гистре 9 схема 8 сравнения выдает сигнал в блок 12, который в свою оче- . редь формирует сигнал разрешения считывания РСь или разрешения записи РЗ„ в зависимости от установленного режима работы запоминающего устройства (считывание Сь или запись 3,). Кроме того, блок 12 вырабатывает сигнал С, поступающий в ЦВМ и свидетельствующий о том, что поиск заданного адреса закончен и .запоминающее устройство готово к обмену информацией.

При..безошибочной работе устройст-. ва, описанной выше, схема 10 сравнения и дешифратор 11 не оказывают на него влияния.

Ошибки в работе запоминающего устройства, существенные с точки зрения взаимодействия его с ЦВМ, связаны со сбоями или отказами регистра 2 или усилителя 3, что приводит, например, к пропаданию синхроимпульса, счетчика синхроимпульсов 4, счетчика 7 продвигающих импульсов.

При этом одновременные отказы нескольких элементов считаются маловероятными.

В первом случае состояние счетчика 4 отличается на единицу (в сторону меньших адресов} от состояния счетчика 7, который фиксирует правильный текущий адрес. В связи с этим со схе5 9039 мы 10 сравнения на вход дешифратара 11 поступает си гнал несовпадения кодов.

Сигнал с соответствующего выхода дешифратора 11 поступает на вход счетчика 4, добавляя к его содержимому s единицу и тем самым корректируя ошибКу, Во втором случае, при неправильной работе собственно счетчика 4 ошибка обнаруживается схемой встроенного контроля счетчика 4 не показана} и сигнал с выхода счетчика 4 поступает на чход дешифратора 11. Kpo" ме того, срабатывает схема 10 сравнения, сигнал с выхода которой также поступает на вход дешифратора 11.

В соответствии с входными сигналами, возбуждается один иэ выходов дешифратора 11 и сигнал поступает на вход блока 12. При ошибочном 2о срабатывании схемы встроенного контроля счетчика 4 (при этом собственно счетчик 4 работает нормально) схема 10 сравнения не работает и возбуж« дается другой выход дешифратора 11, И сигнал с которого также поступает на вход блока 12.

3 третьем случае работа устройства происходит аналогично второму случаю. При неправильной работе счетчи- зо

)ка 7 срабатывают схема встроенного контроля счетчика 7 (не показана) и схема 10 сравнения. При ошибочном срабатывании схемы встроенного контроля ее сигнал поступает на вход деширфатора 11 Соответствующие сигналы дешифратора 11 подаются в блок 12.

Неправильная работа счетчиков 4 и 7, а также их схем встроенного контроля,. не могут быть скорректированы, в поэтому в таких случаях блок 12 вырабатывает сигнал останова устройства с одновременной фиксацией неисправного блока..

Таким образом, предлагаемое устройство позволяет повысить надежность выборки адресов в памяти последова тельного действия, так как оно не олько обнаруживает и локализует ошибки, возникающие в процессе его работы, но и устраняет последствия наиболее вероятных и опасных из нихошибок в работе регистра 2 синхроимпульсов и усилителя 3 синхроимпуль" сов< формула изобретения

Устройство для контроля и коррекции адресных сигналов для памяти последовательного действия, содержащее регистр адреса, формирователь продвигающих импульсов, регистр маркера, регистр синхроимпульсов, усилитель синхроимпульсов, усилитель маркерных импульсов, счетчик синхроимпульсов, первую схему сравнения и блок управления, причем выход формирова" теля продвигающих импульсов подклю" чен ко входам регистра синхроимпульсов и регистра маркеров, -выходы которых подключены соответственно ко входам усилителя синхроимпульсов и усилителя маркерных сигналов, выходы которых соединены соответственно с первым и вторым входами счетчика синхроимпульсов, входы nepal схемы сравнения соединены соответственно с первым выходом счетчика синхроимпульсов и выходом регистра адреса, а выход подключен к одному из входов блока управления, о т л и ч а ю щ е" е с я тем, что, с целью повышения надежности устройства, оно содержит дешифратор, вторую схему сравнения и счетчик продвигающих импульсов, входы которого подключены соответственно к выходам усилителя маркерных импульсов и формирователя продвигающих импульсов, а выходы - к первым входам второй схемы сравнения и дешифратора, второй и третий входы ко" торого соединены соответственно с

I выходом второй схемы сравнения и втОрым выходом счетчика синхроимпульсов> одни из выходов дешифратора являются управляющ ми выходами устройства, другой выход подключен к первому вхо» ду счетчика синхроимпульсов, первый выход которого подключен ко второму входу второй схемы сравнения.

Источни ки информации, принятые во внимание при экспертизе

1. Патент CLN L" 3270318, кл. 340-146. 1, опублик. 1966.

2. Иигин А.Г., Дерюгин А.Л. Цифро вые вычислительные машины. И., "Энер" гия", 1975, с. 355 (прототип).

903909 ь 8 илиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель B. Рудаков

Редактор С. Ерупенина Техред И. Надь Корректор А, Дзятко

Заказ 134/3б Тираж 623 По 1писное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий б

113035> Москвад И-35 Раушская наб. . 4/5