Дешифратор

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистичесиик

Респттбпии

ОП ИСАНИЕ

ИЗОВЕИтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii)905813 (61) Дополнительное к авт. свид-ву

{22)Заявлено 30. 04.80 (21) 2918693/18-24 (51) М. Кл. с присоединением заявки М

6 06 Г 5/00

3Ьаударатеенный комнтет

СССР ао делам нзооретеннй н открытн11 (23) Приоритет

Опубликовано 15. 02. 82. Бюллетень Мв 6

Дата опубликования описания 1 5 .02, 82 (53) УДК681 3

1 088. 81 (72) Автор изобретения

В.Н..Захаров (7I ) Заявитель (54) ДЕЫИфPATÎP

Изобретение относится к автоматике и технике управления, и может быть использовано для передачи информации в каналах связи.

Известен дешифратор, используемый в системе телеуправления, содержащий регистры, триггеры, элементы И (13.

Недостатком известного дешифратора является сложность конструкции.

Наиболее близким по технической сущности к предлагаемому является дешифратор, содержащий двоичный счетчик, сдвиговый регистр, первый, второй и третий элементы И, триггер, i-pyriny из и регистров (и — число десятичных разрядов в представлении номера дешифруемой команды),группу из и двоичных счетчиков, группу элементов И, входной распределитель импульсов, элемент И конца дешифрации, первый вход первого элемента И является входом устройства, выход, сдвигового регистра является восходом устройства, второй вход первого элемента И соединен с выходом триггера, выход первого элемента li соединен со входом триггера, первый вход второго элемента И соединен со входом устройства, выход второго элемента

И с первым входом третьего элемента

И, второй вход которого соединен с выходом элемента И конца дешифратора, входы которого соединены с выходами соответствующих элемен10 тов 11 группы, первые входы которых соединены с выходами соответствующих регистров группы, а вторые входы с выходами соответствующих двоичных счетчиков группы, входы регистров

15 группы соединены с соответствующими и выходами входного распределителя импульсов, (n+1)-й выход которого соединен со вторым входом второго элемента И, вход входного распре"

20 делителя импульсов соединен с выходом первого элемента И, выход третьего элемента И соединен со входом сдвигового регистра и со вхо20

3 90581 дом первого двоичного счетчика группы, вход 1-го двоичного счетчика группы (i=2,3,...,n) соединен с выходом (I-1)-го двоичного счетчика группы. 5

B двоичный счетчик записывается и-разрядное дешифрованное двоичное число госледовательно, поразрядно, начиная со старшего разряда.

Импульсная последовательность со !0 входа через первый и второй элементы И поступает на счетный вход двоичного счетчика и через распределитель импульсов на регистры группы, Когда входной распределитель импульсов заполнит все и регистров группы, начиная с и до 1, открывается третий элемент И, и импульсная последовательность со входа дешифратора поступает на вход счетчиков группы.

При последовательном заполнении счетчиков группы балансируются соответствующие элементы И группы, и когда они сбалансируются, на выходе элемента И конца дешифрации сформируется сигнал управления, закрывающий третий элемент И. Положение импульса в этот момент в сдвиговом регистре соответствует номеру переданной команды .23.

Недостатком такого дешифрую!тора является наличйе группы из п регистров, где дешифруемое число поразрядно запоминается на время от начала цикла дешифрации до момента, когда открывается третий элемент И, и импульсная последовательность поступает на вход счетчиков группы и одновременно в сдвиговый регистр. При этом время дешифрации равно сумме времени заполнения группы из и регистров и времени заполнения счетчиков группы.

Целью изобретения является упрощение и повышение быстродействия дешифратора.

Поставленная цель достигается тем, что дешифратор, содержащий элемент И, счетчик, триггер, первый сдвиговый регистр, группу из и последо50 вательно соединенных счетчиков, группу из п элементов И, выход элемента И соединен с входом первого счетчика группы и входом первого сдвигового регистра, выход счетчика

> соединен с входом триггера, выходы

55 разрядов первого сдвигового регистра являются выходами дешифратора,дополнительно содержит элемент ИЛИ

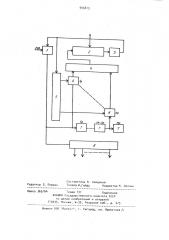

3 4 и второй сдвиговый регистр, причем первый вход элемента И подключен к шине тактовой частоты дешифратора. а второй вход подключен к выходу триггера и входу второго сдвигового регистра, первые входы элементов И группы подключены к входам счетчиков группы соответственно, выходы разрядов второго сдвигового регистра соединены со вторыми входами эле ментов И гругпы соответственно, выходы которых соединены с выходами элемента ИЛИ, выход которого соединен со счетным входом счетчика, входы разрядов которого подключены к входам записи информации дешифратора. На чертеже представлена блоксхема дешифратора.

Схема содержит элемент И 1, счетчик 2, триггер 3, элемент ИЛИ 4, сдвиговый регистр 5, гругпу элементов И 6, группу счетчиков 7 и сдвиговый регистр 8.

Устройство работает следующим образом.

B счетчик 2 записывается и-разрядное дешифрируемое число последовательно, поразрядно, начиная со старшего разряда. В исходном состоянии элемент И 1 открыт,на выходс п сдвигового регистра 5 разрешающая 1" и последний элемент И 6 группы открыт. Импульсная последовательность со входа через элемент И 1 поступает на вход первого из группы счетчиков 7, одновременно на вход сдвигового регистра 8. Начинает перемещаться 1и на выходах сдвигового регистра 8, и заполняется счетчик 7 группы, В момент записи первого импульса в и-ый счетчик 7 группы через последний п.-ый! элемент И 6 группы и элемент ИЛИ 4 этот импульс поступает s счетчик 2, В момент записи следующего импульса в п-ый счетчик 7 группы через ту же цепочку: и-ый элемент И 6 группы и элемент

ИЛИ 4, - импульс снова заносится в счетчик 2.3 момент переполнения счетчика 2 с него поступает импульс на триггер 3, который запрещает прохождение импульсов через элемент И 1 и вызывает сдвиг, разрешаю ;,ий "1 в сдвиговом регистре 5. Затем в счетчик

2 записывается число разряда меньшего на единицу.

Аналогично вышеизложенному ерез открытый (n-1)-ый элемент И 6 группы и элемент ИЛИ 4 импульсы с выхо905813 4 начала цикла дешифрации до момента, когда в сдвиговый регистр начинает поступать импульсная последовательность, т.е. на время поразрядной записи дешифрированного числа в группу из п регистров.

5 да (n-2)-го счетчика 7 группы поступают на входы счетчика 2. В момент его переполнения триггер 3 закрывает элемент И 1 и вызывает очередной сдвиг 1" в сдвиговом регистре 5.

При записи в счетчик 2 последнего младшего разряда дешифруемого числа импульсная последовательность с выхода элемента И 1 поступает на вход 1Q первого счетчика 7 группы, сдвигового регистра 8 и через первый элемент И 6 группы и элемент ИЛИ 4 в счетчик 2. При переполнении счетчика 2 триггер 3 закрывает элемент И 13

1 и устанавливает регистр 5 в исходное состояние. Положение импульса в этот момент в сдвиговом регистре

8 соответствует номеру переданной команды. 20

По сравнению с известным дешифратором в предлагаемом отсутствуют два элемента И и группа и регистров.

Входной распределитель импульсов и элемент И конца дешифрации известно- 23 го дешифратора, сдвиговый регистр 5 и элемент Jll 4 в предлагаемом дешифраторе по числу применяемых при их построении элементов одинаковы.

В образце дешифратора по схеме 30 известного для дешифрации двухразрядных десятичных чисел с общим числом команд 99 применено 26 микросхем. А в предлагаемом дешифраторе на то же число команд применено 35 только 14 микросхем. Такая разница объясняется не только отсутствием

2-х регистров группы, но и значительным уменьшением числа элементов V группы. Так в известном дешифраторе для каждого счетчика группы необходимо четыре (по числу разрядог счетчика) элемента И, для двух счетчиков — всего 8. Тогда как для предлагаемого дешифратора необходи- 45 мо только 2 элемента И.

Кроме того, время дешифрации предлагаемого дешифратора меньше, чем у известного на величину времени от

Формула изобретения

Дешифратор, содержащий элемент И, счетчик, триггер, первый сдвиговый регистр, группу из п последовательно соединенных счетчиков, группу из и элементов И, выход элемента И соединен с входом первого счетчика группы и входом первого сдвигового регистра, выход счетчика соединен с входом триггера, выходы разрядов первого сдвигового регистра являются выходами дешифратора, о т л ич а ю шийся тем, что, с целью упрощения и повышения быстродействия, дешифратор содержит элемент ИЛИ и второй сдвиговый регистр, причем первый вход элемента И подключен к шине тактовой частоты дешифратора, а второй вход подключен к выходу триггера и входу второго сдвигового регистра, первые входы элементов И группы подключены к входам счетчиков группы соответственно, выходы разрядов второго сдвигового регистра соединены со вторыми входами элементов И группы соответственно, выходы которых соединены с входами элемента ИЛИ,выход которого соединен со счетным входом счетчика, входы разрядов которого подключены к входам записи инФормации дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

1" 434405, кл. Г 06 Г 5/02, 1974.

2. Авторское свидетельство СССР

744547, кл. Г 06 Г 5/02, 1977 (прототип).

О05813

Составитель В. Кайданов

Техред И.Гайду Корректор M. немчик

Редактор Л. Повхан

Тираж 731 .Подписное

ННИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 365/64

Филиал ППП Патент", r. Ужгород, ул. Проектная,4