Цифровой синусно-косинусный преобразователь

Иллюстрации

Показать всеРеферат

(22) Авторы изобретения

А.И. Агизим и Б.К. 1(рамаренко

Львовский ордена Ленина политехническ и институт (7) ) Заявитедь (=4) q e OeON CWnHO- О ИНУ Нцй ГБ Б1 А БА БЛБ

15

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки информации, осуществляющих определение синусной и косинусной составляющих вектора, преобразование координат, генерирование синусоидальных сигналов, сдвинутых на четверть периода.

Известен синусно-косинусный преобразователь, содержащий запоминающее устройство, в котором хранятся табличные значения синуса и косинуса всех точек преобразования (13.

Недостатком преобразователя является значительное увеличение оборудования при увеличении количества точек преобразования и точности получаемых значений.

Наиболее близким по технической сущности к предложенному является преобразователь, содержащий регистры синуса и косинуса и сумматоры синуса и косинуса и блок синхронизации, при ем выход регистра синуса подключен к первому входу сумматора синуса, выход регистра косинуса подключен к первому входу сумматора косинуса, установочные входы регистров синуса и косинуса соединены с входами устройства, выходы сумматоров синуса и косинуса подключены ко входам регистров синуса и косинуса соответственно, вход блока синхронизации соединен с управляющим входом устройства, выход тактовых импульсов блока синхронизации соединен с импульсными входами регистров синуса и косинуса, управляющие входы которых соединены с выходом управления установкой блока синхронизации (2).

Недостатком устройства является значительная погрешность интерполя20 ции, что вынуждает для повышения точности вводить дополнительные узловые точки внутри квадранта, т.е усложнять шифратор.

3 90581

Цель изобретения - повышение точности преобразования и расширение функциональных возможностей преобразователя.

Поставленная цель достигается

5 тем, что в устройство, содержащее регистры синуса и косинуса и сумматоры синуса и косинуса и Глок синхронизации, причем выход регистра синуса подключен к первому входу сумматора синуса, выход регистра косинуса подключен к первому входу сумматора косинуса, установочные входы регистров синуса и косинуса соединены с входами устройстаа,выходы сумматоров синуса и косинуса подключены ко входам регистров синуса и косинуса соответственно, вход блока синхронизации соединен с управляющим входом устройства, выход тактовых импульсов блока синхронизации соединен с импульсными входами регистров синуса и косинуса, управляющие входы которых соединены с выходом управления установкой блока синхронизации, дополнительно введены два сумматора синуса и косинуса соответственно, причем первые входы дополнительных сумматоров синуса и косинуса соединены с выходом реЗО гистра синуса, вторые входы дополнительных сумматоров подключены к выходу регистра косинуса, выходы дополнительных сумматоров синуса и косинуса подключены ко вторым входам сумматоров соответственно синуса и косинуса.

40

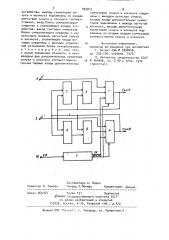

На чертеже представлена блок-схема устройства.

Устройство содержит регистр синуса .1, сумматор синуса 2, дополнительный сумматор синуса 3, регистр косинуса 4, сумматор косинуса 5,дополнительный сумматор косинуса б и блок синхронизации 7, установочные входы регистров 8 и 9, управляющий вход устройства 10. Блок синхронизации 7 содержит два стандартных генератора: генератор одиночного им50 пульса установки регистров в исходное состояние и генератор тактовых импульсов преобразования. Управление генераторами осуществляется коо мандой со входа 10, длительность

55 которой пропорциональна величине фазового угла.

Устройство работает следующим образом.

5 4

С поступлением команды управления установкой и преобразованием со входа 10 блок синхронизации 7 вырабатывает импульс установки исходного состояния. Импульсом установки исходного состояния регистр 1 устанавливается в состояние н0" со входа 8, а в регистр 4 в двоичном коде заносится значение амплитуды вектора со входа 9. На дополнительном сумматоре 3 синуса из значения, установленного в регистре 4 косинуса,вычитается со сдвигом на (Р + 1) разрядов B сторону младших значение, установленное в регистре 1. Результат со сдвигом на Р разрядов в сторону младших подается на сумматор 2 синуса и суммируется со значением, установленным а регистре 1. На дополнительном сумматоре 6 косинуса значение, установленное а регистре суммируется со сдвинутым на (Р + 1) разрядов в сторону младших значением1устаноаленным в регистре 4. Полученное значение со сдвигом на P разрядов а сторону младших подается на сумматор 5 косинуса и вычитается из значения, установленного в регистре

По команде управления преобразованием со входа 10 блок синхронизации 7 вырабатывает тактовые импульсы преобразования, количество которых пропорционально фазоаому углу, которые поступают на импульсные входы регистров 1 и 4. С приходом тактового импульса преобразования происходит занесение полученных на выходах сумматоров 2 и 5 значений соответственно в регистры 1 и 4. С поступлением каждого нового тактового импульса преобразования в регистрах 1 и устанавливаются новые значения, величины которых изменяются по синусоидальному и косинусоидальному законам соответственно. Таким образом, поступление очередного импульса преобразования как бы осуществляет поворот вектора на определенный фазовый угол. Если количество тактов преобразования соответствует заданному фазовому углу, то в регистрах

1 и 4 устанавливаются соответственно значения синусной и косинусной составляющих заданного вектора.

A — значение синусной составляюYi щей, полученной Hà К-ом шаге преобразования, В 1 — значение косинусной составляющей, полученной на К-ом шаге преобразования; C g — значение ам5 90 плитуды вектора на К-ом шаге преобразования; P - -количество разрядов сдвига в сторону младших разрядов на входе сумматора одного слагаемого по отношению к другому (Р = О, 1, 1

2...), сь = — -р-. Г О.

Ъ = arctp -- — --„ а1—

Цифровой синусно-косинусный пре50; образователь, содержащии регистры синуса и косинуса, сумматоры синуса и косинуса и блок синхронизации,причем выход регистра синуса подключен к первому входу сумматора синуса, 55 выход регистра косинуса подключен к первому входу сумматора косинуса, установочные входы регистров синуса и косинуса соединены с входами

Тогда на {Е + 1) шаге преобразования в соответствии со схемой, представленной на чертеже, получают

Р+„- к="к " — cLS1, >

Р

4-1 «- — -A Ь - - Д

Рр < р к к

Определяют амплитуду вектора после (K + 1) шага преобразования (,,1" А К,1 4 1 ° )1 - — /1 Ф(1. Ц

С Р Е 1 к В "

-Щ(А1t,">4) "= « = „ где

4 4

1+ 1+- —

Поскольку о. ((1, то с большой степенью точности можно считать

К4 Ь )

1, тогда к

Таким образом, на,K + 1) шаге преобразования осуществляется поворот вектора Ск на угол ь 1. За и шагов преобразования происходит поворот вектора С и на угол Я ф1 1 щд1

Ф" 0 11

Иножитель 1, определяет погрешность преобразования, обусловленную изменением амплитуды вектора в процессе преобразования. Увеличивая значение Р, можно производить преобразование с меньшим шагом по фазе и меньшей погрешностью, однако при этом увеличивается время преобразования.

Сравнивают погрешности преобразования (интерполяции1, получаемые вследствие изменения амплитуды вектора, для известного и предлагаемого устройств. Аналогичным образом и с аналогичными допущениями найденное для известного значение множи 81 6 теля, определяющего изменение амплитуды вектора за один шаг преобра- зования, равно

t7 ())1

1 + где (x-х ) — шаг аргумента.

Применяя принятые обозначения, получают для известного — +—

9 предлагаемом устройстве .1."

1+-—

Таким образом, погрешность преобразования предлагаемого устройстЦ ва в — раэ меньше чем у известногс го. Например, для значения Р-=1) (шаг преобразования по фазе g g = > 34)1, погрешность преобразования r редлагаемого устройства меньше примерно в 1000 раз, чем у известного.

Расширение функциональных возможностей предлагаемого устройства заключается в том, что, во-первых, в предлагаемом устройстве синус-косинусному ) реобразованию подвергается установленная амплитуда вектора. Во-вторых, предлагаемое устройство позволяет осуществить операцию определения амплитуды вектора. и фазового угла по устанавливаемым

35 в регистры значениям синусной и косинусной составляющих. Для этого осуществляется поворот вектора до изменения знака одной из составляющих. 8 момент изменения знака одо ной составляющей в регистре другой составляющей устанавливается значение амплитуды вектора, а количество шагов преобразования свидетельствует о фазовом сдвиге.

Формула изобретения

9058

Составитель А. Зорин

Техред Л.Йекарь Корректор1М. Демчик

Редактор Jl. Повхан

Тираж 731 Подписное

В41ИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, (-35, Раушская наб., д.4/5

Заказ 365/64

Филиал ППП "Патент, r Ужгород, ул. Проектная,4

7устройства, выходы сумматоров синуса и косинуса подключены ко входам регистров синуса и косинуса соответственно, вход блока синхронизации соединен с управляющим входом устройства, выход тактовых импульсов блока синхронизации соединен с импульсными входами регистров синуса и косинуса, управляющие входы которых соединены с выходом управле- 1о ния установкой блока синхронизации, отличающийся тем, что, с целью повышения точности, в него введены два дополнительных сумматора синуса и косинуса соответственно, причем первые входы дополнительных

15 8 сумматоров синуса и косинуса соединены с выходом регистра синуса, вторые входы дополнительных сумматоров подключены к выходу регистра косинуса, выходы допочнительных сумматоров синуса и косинуса подключены ко вторым входам сумматоров соответственно синуса и косинуса.

Источники инФормации, принятые во внимание при экспертизе

1. Патент США И 3898446, кл. 235-156, опублик. 1975.

2. Авторское свидетельство СССР и 464006, кл. С 08 С 9/04, 1972 (прототип).