Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социапнстмчесиик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22)Заявлено 08.05.80 (21) 2921480/18-24 (51)Ч. Кл.

G 11 С 11/00 с присоединением заявын,%

9вудврственвй квинтет

СССР

No авлвм взабрвтеияй и открытий (23) Приоритет

Опубликовано 15.02.82. Бюллетень № 6

Дата опубликования описания 17.02.82 (53) УДК 681.327..6 (088.8) (72) Автор изобретения

В. Л. Яцкевич

I

Гомельский государственный у иверсИтет

1 ( (74) Заявитель (54) ЗАПОМИНЛЮШЕЕ УСТРОЙСТВО

Изобретение относится к вычислитель: ной технике и может быть использовано в качестве запоминаюшего устройства в вычислительных машинах.

Известно устройство для выборки адреса в постоянном запоминаюшем устройстве, содержашее дешифратор адреса, запоминаюшие элементы, кольцевую пересчетную схему, генератор кодов и выходные вентили. Код адреса числа, пришедший на дешифратор адреса, возбуждает одну из адресных шин, с которой сигнал поступает на соответствуюший запоминаюший элемент L1) .

Известны постоя нные залом инаюшие устройства, содержашие ячейки запоминаюших элементов и устройство управления, обеспечиваюшее поиск и считывание информации. Устройство управления состоит из регистра адреса, дешифратора и

2О усилителей считывания. Дешифратор в соответствии с кодом адреса выбирает одну..ячейку, а усилители считывания усиливают сигнал с этой ячейки до необходимого уровня f2).

Недостаток указанных устройств заключается в том, что обрашение к ячейке запоминаюшнх элементов и считывание информации одновременно может происходить только по одному адресу. При обрашении по разным адресам считывание информации происходит последовательно, при этом суммарное время выборки имеет большое значение.

Наиболее близкой к изобретению по технической сушности является двухкоординатная матрица с двумя ступенями дешифрации, содержашая матрицу запоминаюших элементов, блок адреса с дешифраторами адресов и адресными формирователями и блок считывания с усилителями считывания. При поступлении на дешифраторы адресов кода адреса определенного запоминаюшего элемента возбуждаются определенные шины дешифраторов и с помошью адресных шин по двум координатам выбирается запоминаюший эле3 9058 мент, с которого по обшей для всех элементов разрядной шине считывается его состояние (31.

Однако укаэанное устройство обеспечивает обращение к запоминающим элементам и считывание информации только по одному адресу. Обращаться и считывать информацию независимо и одновp< менно по разным адресам невозможно.

Таким образом, общее время выборки ре по разным адресам имеет большое зна чение и определяется суммой времен выборки по каждому адресу отдельно.

Цель изобретения — повышение быст родействия устройства. 15

Указанная цель достигается тем, что в запоминающее устройство, содержащее элементы памяти, выходы которых подключены ко входу блока считывания, и адрес-20 ный блок, введены дополнительные адресные блоки, аналоговые сумматоры и дополнительные блоки считывания, входы которых подключены ко входу блока считывания, выходы аналоговых сумматоров подключены к соответствующим входам элементов памяти, а входы аналоговых сумматоров подключены к соответствующим выходам адрзсных блоков.

Кроме того, элемент.памяти содержит 5© триггер, ключ, согласующий элемент, выход которого подключен ко входу ключа, а управляющий вход ключа подключен к выходу триггера.

Адресный блок содержит первый и вто- З5 рой дешифраторы, первую и вторую группы ключевых элементов и генератор, первый выход которого подключен к первым входам первой группы ключевых элементов, а второй выход - к первым входам второй группы ключевых элементов, вы- . ходы первого адресного дешифратора подключены к соответствующим входам ключевых элементов первой группы, а выходы второго адресного дешифратора

45 подключены к соответствующим входам ключевых элементов второй группы.

Блок сч итывания содержит преобразователь и полосовой фильтр, выход которого подключен ко входу преобразователя.

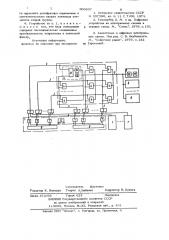

На чертеже представлена схема предлагаемого запоминающего ycTpolcTB&.

Запоминающее устройство содержит адресные блоки 1, аналогЬвые суммато° ры 2, адресные шины 3, элементы памя55 ти 4, общую разрядную шину 5, блоки считывания 6, включевые элементы 7, первый 8 и второй 9 адресные дешифра57 4 торы, первый 10 и второй 11 выходы генератора, генератор 12, согласующий элемент 13, ключ 14, триггер 15, полосовой фильтр 16 и преобразователь напряжения 17.

Устройство работает следующим обраКоличество адресных блоков 1 равно количеству блоков считывания 6. В состав адресного блоке 1 входит генератор 12, а в состав каждого блока считывания 6 входит полосовой фильтр 18, причем в полосе пропускания фильтров

18 находятся соответственно несущие частоты задающих генераторов 12, а значения несущих частот задающих генераторов 12 не равны между собой.

Обращение к матрице элементов памяти 4 происходит цри подаче кодов адреса на входы адресных блоков 1, причем каждый из них обеспечивает обращение в каждый момент времени только к одно му элементу памяти 4, т.е. только по одному адресу. Одновременное и независимое обращение по одному или разным адресам обеспечивается одновременным обращением нескольких адресных блоков

1 к общей матрице элементов памяти 4, прн этом адресные блоки 1 вырабатывают сигналы опроса в виде колебаний с разными несущими частотами, имеющими различный спектр, а выделение сигналов считывания из общего происходит за счет частотного разделения системой полосовых фильтров 18 в блоках считывания 6.

Каждому адресному блоку 1 соответствует определенный блок считывания 6, полосовой фильтр 18 которого пропускает сигналы с частотой генератора 12 данного адресного блока 1.

Рассмотрим работу устройства в режиме считывания информации более подробно. Код адреса опрашиваемого элемента памяти 4 поступает на вход блока адреса 1, а точнее код адреса одной координаты поступает на вход первого дешифратора адреса 8 этой координаты, а код адреса другой координаты, поступает на вход второго дешифратора 9 другой координаты, при этом на одном выходе дешифратора 8 и одном выходе дешифратора 9 появляются логические сигналы, которые поступают на первые входы соответствующих ключевых элементов 7. Выходной сигнал генератора 12 в виде опао-. полярных i,ìïóëüñîâ с определенной несущей частотой действует между выходами 10 и 11, причем положительный по5 905857 6 тенциал приложен к выходу 10. Так как нкй .разных частот и кх частотное раьвыход 10 присоединен ко вторым входам деление в блоках считывания 6 позволяключевых элементов 7 первой группы, а ет одновременно обращаться к многим выход 11 присоединен ко вторым вхо- адресным блокам l и считывать информадам ключевых элементов 7 второй груп- цию со многих элементов памяти 4. Прн пы, то сигнал генератора 12 оказывает- этом поле памяти, образованное матрися приложен между вторыми входами цей элементов 4 памяти, остается общим. ключевых элементов 7 пер ой н второй Уменьшение общего времени выборки стагрупп. Логические сигналы с дешифрато- новится значительным при большом колнРов 8 и 9 являются разрешающими для >0 честве одновременно опрашиваемых адресключевых элементов 7, на которые они ных блоков. поступают, и сигнал генератора 12 оказывается приложенным между входами Применение предлагаемого з апомкнаюакалоговых сумматоров 2 разных коор- шего устройства по сравнению с извест ественно меньшкть тых ключевых элементов 7. Каждый ана- время выборки, при этом отпадает необлоговый сумматор 2 обеспечивает пере- ходимость поочередного обращения к обдачу сигналов с любого входа на общий шему цолю памяти и устаковлению прквыход, при этом обеспечивается и раз- оритета при обращении. Независк езавискмость вязка входных сигналов. Практически, рй,обращения в предлагае Устр агав мом стоойстве аналоговый сумматор 2 может быть реа- позволяет ксполъзовать его в к ест позволяет ксполъзовать его в качестве лизован в виде диодной сборки, одинако- запоминающего Устрой а запоминающего ст оФства в вычислительвые электроды которой присоединены к ных системах с большим количеством общему выходу. Таким образом, сигнал кктных сит аций при обюащеыии в генератора 12 оказывается приложенным 25 между адресными шинами 3, соединенными с выходами соответствующих аналоговых сумматоров 2, и поступает на входы Ф Р У

Фо м ла изобретения опрашиваемого элемента памяти 4. Этот сигнал через согласующий элемент 13 Зй 1. Запоминающее устройство, содержащее элементы памяти, выходы которых поступает на вход ключа 14. В триггере подключены ко входу блока считывания, 15 элемента памяти 4 хранится один и ад есный блок, о т л и ч а ю щ е вбит информации. Если триггер 15 нахо- адр с я тем, что, с целью повышения быст днтся в нулевом состоянии, то ключ 14 родействия устройства, оно содержит дозакрыт к на его выход никакие сигналы не проходят, а если в триггере 15 хра- полнктельные адресные блоки, аналоговые сумматоры и дополнительные блоки нится логическая "1 ", то сигнал с триггера 15 поступает на ключ 14 и держит считывания, входы которых подключены его в открытом состоянии. B этом случае ко входу блока считывания, выходы акасогласуюший элемент 13 обеспечивает,,е> логовых су тор логовых с мматоров подключены к соответств юшкм входам элементов памяти, согласование и передачу сигнала со вхо» ветству да через открытый ключ на

14 общую а входы — к соответствУюшим выходам разрядную шину 5. C выхода обшей раз- адРесных блоков.

2. Ус ойство по ц. 1, о т л и ч арядной шины 5 сигнал поступает на 2. Устройство ю ш е е с я тем, что элемент памяти входы блоков считывания 6, причем вхос жит последовательно соединенные дом каждого блока считывания 6 являет- содеРж триггер, ключ к согласующий элемент.

3. Устройство по и. 1, о т л к ч аявляется на выходе только того полосою ш е е с я тем, что адресный блок вого фильтра 16, в полосе пропускания содержит первый и второй дешифраторы, которого находится несущая частота дан- в содер ц в ю к вторую группу ключевых эленого колебания. Далее этот сигнал с вы- ер У ментов и генератор, первый выход котохода фильтра 16 поступает на вход прерого подключен к первым входам ключеобразователя 17, на выходе которого и второйвых элементов первой группы, а второ он преобразуется в логический сигнал. выход - к первым входчм ключевых

Аналогично происходят опрос и считывание элементов второй группы, выходы первс информации с элементов памяти 4 другиго адресного дешифратора подключены к ми адресными блоками 1.

Использование в устройстве в качест- соответствующим входам ключ ве сигналов опроса переменных колеба- ментов п вой группы, а выходы второменто ер гру

3. Аналоговые и цифровые интегральные схемы. Под ред. С. В. Якубовского.

М., "Советское радио, 1979, с. 132

16 (прототип) .

7 9058 го адресного дешифратора. подключены к соответствуюшим входам ключевых элементов второй группы.

4. Устройство по и. 1, о т л и ч а— ю щ е е с я тем, что блок считывания содержит последовательно соединенные преобразователь напряжения и полосовой фильтр.

Источники информации, принятые во внимание при экспертизе

57 8

1. Авторское свидетельство СССР

N< 357590, кл. G 11 С 7/00, 1971.

2. Гольдербер П. М. и др, цифровые устройства на интегральных схемах в технике связи. М., "Связь", 1979, с. 101.

С оставитель Шустенко

Редактор К. Волошук Техред А.Бабинец Корректор В. Бутяга

Заказ 373/66 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Мссквв, Ж-35, Рвушсквя яяб., я. 4У5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4