Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстнческнк респубики

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Дополнительное ы авт. свнд-ву (22) За я вл е ио 29. 06. 7 9 (21 } 27 86 17 4/ 18-24 (51)М. Кл.

G 11 С 17/00 с присоединением заявки М

9)еударстаанвй кеиктет

ИСР по двлан нзабретеккй и открытий (23) Приоритет

Опубликовано 15„02.82. Бюллетень Ют 6

Дата опубликования описания 17.02.82 (53) УДК, 681.327. . 66 (088. 8) B. A. Знаменский, В. А. Мипоспавов, В. В. 5 бин н Т. И. Содовьева (22) Авторы изобретения (7l) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАКЗШЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике, в частности запоминаюшим устройствам трансформаторного типа.

Известно запоминаюшее устройство, которое содержит трансформаторные эпе« менты памяти, прошитые числовыми шинами, вентили считывания, регистр числа, блок стробирования и формирователи тока выборки. Шина считывания каждого эпемента памяти соединена одним концом с вентилем считывания (эпемент И-HE), а другим — с обшей шиной "корпус " C Q .

Недостатком известного устройства является значительный ток выборки, необходимый для выборки в шине считывания трансформаторного элемента памяти сигнала, достаточного, чтобы сработал вентиль считывания. Кроме того, при считывании большого количества "единиц" или иудей" происходит генерация помех по цепи питания вследствие одновременн<>-

ro открывания вентилей считывания. Подключение одного конца выходной обмотки элементов памяти к обшей шине ухудшает соотношение сигнал/помеха на входе вентилей считывания.

Наиболее близким по технической cymности и достигаемому результату к предлагаемому изобретению является запоминаюшее устройство, содержашее трансформаторные элементы памяти, прошитые числовыми шинами и соединенные с формирователями тока выборки, регистр, соединенный с трансформаторными элементами памяти и блоком стробирования.

Шина считывания каждого элементе памяти соединена одним выводом с входом усипитепя считывания соответствуюшего разряда регистра, а вторым выводом к обшей шине. Регистр известного устройства состоит из усилителей считывания и R5 -триггеров, собранных на. элементах И-ИЛИ-HE. Выход каждого усилите» пя считывания соединен с одним входом

И соответствуюшего элементы И-ИЛИ-НЕ

RS -триггера, а другой вход И этого

3 . 9058 цемента соединен с блоком стробирова» ния С2).

Недостатком известного устройства является сложность регистра и недостаточная надежность работы запоминающего устройства. Так как мощность считываемых сигналов недостаточна для срабатывания логических элементов, то необходимы усилители считывания, что усложняет устройство. Подключение одно- 16 го конца шины считывания трансформаторных элементов памяти к обшей шине ухудшает соотношение сигнал/помеха на входе усилителей, а одновременное срабатывание усилителей при считывании "единиц"

«15 или нулей вызывает генерацию помех по цепи питания, что снижает надежность работы запоминающего устройства.

Цель изобретения - упрощение устройства и повышение надежности его работы.

Поставленная цель достигается тем, что в постоянном запоминающем устройстве, содержащем накопитель, трансформаторные элементы памяти которого

25 прошиты числовыми шинами и шинами считывания, подключенными соответственно к выходам формирователей тока выборки и к входам каждого разряда регистра„ и блок стробирования, средние точки

30 шин считывания трансформаторны эле ментов памяти накопителя подключены к выходу блока стробирования.

Кроме того, каждый разряд регистра содержит элементы НЕ и RS -триггер, установочные входы. которого являются

35 входами регистра, а выходы RS -триггера соединены с соответствующими входами элементов НЕ, выходы которых являются выходами регистра.

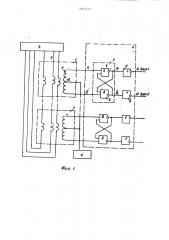

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2— временная диаграмма работы регистра.

Устройство содержит трансформаторные элементы памяти 1, прошитые числовыми шинами 2, соединенными с формирователями тока выборки 3, регистр 4, каждый разряд которого соединен с шиной считывания 5 соответствующего трансформаторного элемента памяти 1 и блок стробирования 6. Каждый разряд регистра содержит RS -триггер 7, построенный на двух элементах И-НЕ 8, и два элемента HE 9, между устайовочными вхо дами RS -триггера 7 включена шина считывания 5 трансформаторного элемента памяти 1, средняя точка 10 шины считывания 5 соединены с блоком строби59 4 рования 6 и каждый элемент И НЕ 8 соединен с элементом НЕ 9.

Устройство работает следующим образом.

В исходном состоянии с выхода блока стробирования 6 потенциал уровня логического «нуля". через среднюю точку 10 пТины считывания 5 поступает на установочные входы RS -триггера 7, При этом на выходах 8 и 8 RS -триггера 7 сохраняются потенциалы логической "единицы", а на выходах элементов HE 9 потенциалы логического нуля $>tx„° 0 фцу, (сме фиГа 2)

Ток, протекающий от формирователей тока выборки 3 по одному из числовых проводов 2, возбуждает на выходах шины считывания 5 трансформаторного элемента памяти l разнополярные сигналы U< и

О, например на входе R RS -триггера

7 положительный, а на входе $ этого триггера — отрицательный. Сразу после подачи от блока стробирования 6 в среднюю точку 10 шины считывания 5 импульса U p, RS -триггер 7 переходит в активное состояние и усиливает разность сигналов U u Uz . В результате однонаправленного регенеративного процесса переключения ЯЬ -триггера 7 на его выходе Э устанавливается потенциал логического "нуля", а на выходе элемента

HE 9, соединенного с R S -триггером 7, уровень логической "единицы" U z„

Состояние RS -триггера 7 определяется фазой сигналов Ц и U< на входах К и

S в момент подачи стробируюшего импульса Uq p и сохраняется в течение его длительности. В идеальном случае увеличение заряда на одном из входов RSтриггера 7, когда он находится в активном состоянии, и уменьшение заряда на другом его входе на бесконечно малую величину вызывает переключение RSтриггера 7 в заранее известное состояние. В реальной схеме количество заряда, которое необходимо внести для переключения RS -триггера 7 в нужное со-стояние, определяется неидентичностью электрических параметров логическиХ элементов И-НЕ 8. Чем больше отличаются электрические параметры логических элементов И-HE 8, тем меньше чувствительность RS -триггера 7. Кроме того, на скорость регенеративного процесса и чувствительность R S -триггера 7 влияет разброс емкостей выходных шин триггера и неидентичность параметров нагрузки.

9058

Чтобы исключить влияние нагрузки и монтажных.соединений на процесс переключения Яб -триггера 7 и устранить генерацию помех по цепи питания при одновременном считывании "единиц или "нулей", % каждый выход 9 и 9 RS -триггера 7 соединен с соответствующим элементом

HE 9. При включении одно.о из элементов И-HE 8 соединенный с ним элемент1 IO.

HE 9 выключается, поэтому ток, потребляемый регистром при считывании информации, не изменяется, тем самым устраняется генерация помех по цепям питания.

Таким образом, совмещение в одной

t5 схеме чувствительного усилителя и триггера уменьшает количество оборудования и упрощает запоминающее устройство.

Включение шины считывания 5 каждого трансформаторного элемента памяти между входами К и S триггера 7 и соединение средней точки 10 шины считывания

5 с блоком стробирования 6 ослабляет действие синфазных помех, а соединение каждого выхода RS -триггера 7 с элементом НЕ 9 устраняет генерацию помех по цепям питания, вследствие этого повышается надежность работы предлагаемого запоминающего устройства по сравнению с известным. В регистре 4 целесообразно использовать логические элементы, физически размещенные в одном корпусе на общем кристалле. Вследствие того, что интегральные логические элементы, расположенные на общем кристал35 ле, изготовлены в едином технологическом цикле, параметры их идентичны с высокой степенью точности. B настоящее время для хранения констант, табличных функций и программ используется извест40 ное. запоминающее устройство Б ОП

2048-33 ПР3.061.000 ТО, разработанное в СССР для EC-1033 ЭВМ. Оно имеет плотность информации 30 бит/см .

Ъ

Для того, чтобы считанная информация записалась в регистр известного устройства, величина считанного сигнала доли на превышать 2 В. В отличие от базового образца, предлагаемое техническое реше59 6 ние позволяет повысить плотность информации за счет упрощения регистра, снизить требование к величине считанного сигнала вследствие возросшей чувствительности последнего и повысить надежность запоминающего устройства благодаря уменьшению генерации помех по цепям питания. Макет запоминающего устройства имеет плотность информации 50 бит/см .

Чувствительность RS -триггеров регистра, собранного по схеме фиг. 1 на микросхемах 133 серии 133llA3, как показали измерения, - 10... 20 мВ, что на два порядка выше чувствительности приемной части регистра базового образца.

Формула изобретения

l. Постоянное запоминающее устройство, содержащее накопитель, трансформаторные элементы памяти которого прошиты числовыми шинами и шинами считывания, подключенными соответственно к выходам формирователей тока выборки и к входам каждого разряда регистра, к блок стробирования, о т л и ч а ющ е е с я тем, что, с целью упрощения устройства и повышения его надежности, средние точки шин считывания трансформаторных элементов памяти накопителя подключены к выходу блока стробирования.

2. Устройство по и. 1, о т л и ч аю ш е е с я тем, что, каждый разряд регистра содержит элементы HE и R5— триггер, установочные входы которого являются входами регистра, а выходы

RS -триггера соединены е соответствующими sxceàìè элементов HE„выходы которых являются выходамн регистра. !

Источники информации, принятые во внимание при экспертизе

1. "Электроника" 1967, Ж 19, с. 27.

2. ЭВМ ЕС-1033, ПР3.061.000 ТО (прототип).

905859

Составитель Л. Амусьева

Редактор К. Волошук Техред A. Бабинец Корректор В. Бутяга

Заказ 373/66 Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4 .4