Ячейка памяти для буферного регистра

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

<п>905860 (61) Дополнительное к авт. свид-ву (22) Заявлено 1104.80 (21) 2908505/18-24 (1)М К з

G 1l С 19/00 с присоединением заявки МГосударственный комитет

СССР ио делам изобретений и открытий (23) Приоритет—

1 3) УДК 681. 327 (088. 8) Опубликовано 150282. Бюллетень Но 6

Дата опубликования описания 150282 (12) Автор изобретения

Б.С. Цирлин

Институт социально-экономических пробг ем AH СССР (11) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ БУФЕРНОГО РЕГИСТРА

Изобретение относится к запоминаю@им устройствам.

Известна ячейка памяти для буферного регистра, построенная на основе трехстабильного триггера на элементах И-2ИЛИ-НЕ, причем в этой схеме входы первого элемента И каждого из трех элементов И-2ИЛИ-HE соединены с выходами двух других элементов

И-2ИЛИ-НЕ (1).

Недостатком этой ячейки является невысокое быстродействие.

Наиболее близким техническим решением к данному изобретению является ячейка памяти для буферного регистра, содержащая три элемента

И-ИЛИ-НЕ, включенные по схеме трехстабильного триггера так, что входы первого элемента И каждого элемента

И-ИЛИ-НЕ соединены с выходами двух других элементов И-ИЛИ-НЕ; и шесть входных шин, причем первая шина соединена с входами первого и третьего элементов И-ИЛИ-НЕ, вторая — с входами первого и второго, третья - с входом первого, а остальные шины— с входами второго и третьего элементов И-ИЛИ-НЕ (2).

Однако в буферном регистре, собранном из ячеек памяти указанного типа каждая порция информации продвигается от первой ячейки к последней, причем время, через которое информация появляется на выходе регистра, . зависит как от собственных (реальных) задержек элементов последнего, так и от его заполнения информацией, что делает невозможной параллельную

10 запись информации в регистр, так как одновременно с записью информации в какую-либо ячейку по шинам параллельной записи в ту же ячейку может поступить порция информации по шинам сдвига из предыдущей ячейки, что нарушает правильность работы регистра. Отсутствие возможности параллельной записи в ячейку ограничивает область ее применения.

Цель изобретения - расширение области применения ячейки памяти за счет обеспечения возможности параллельной записи информации.

Поставленная цель достигается тем, что в ячейку памяти для буферного регистра, содержащую первый, второй и третий элементы H-ИЛИ-НЕ, соединенные по схеме трехстабильного триггера, входные шины, причем первые входы второго и третьего элеменЗО тов И-ИЛИ-НЕ подключены к первой

9О5860

60 входной шине, первый и второй входы соответственно первого и второго элементов И-ИЛИ-НŠ— к второй входной шине, вторые входы первого и третьего элементов И-ИЛИ-HE — к третьей входной шине, третьи и чет- 5 вертые входы второго и третьего элементов И-ИЛИ-НŠ— к четвертой входной шине, пятые и шестые входы второго и третьего элементов И-ИЛИ-НЕ— .к пятой входной шине, третий и чет- lp вертый входы первого элемента И-ИЛИНŠ— к шестой входной шине, введены четвертый и пятый элементы И-ИЛИ-НЕ, соединенные по схеме ))S -триггера, и входные шины с седьмой по десятую, )5 причем седьмые входы второго и третьего элементов И-ИЛИ-HE и первый вход четвертого элемента И-ИЛИ-НЕ соединены с седьмой входной шиной, восьмые входы второго и третьего элементов И-ИЛИ-НЕ соответственно— с восьмой и девятой входными шинами, пятый вход первого элемента

И-ИЛИ-НЕ и второй вход четвертого элемента И-ИЛИ-НЕ подключены к десятой входной шине, третий и четвер25 тый входы четвертого элемента И-ИЛИНЕ соответственно к второй и третьей входным шинам, вход пятого элемента

И-ИЛИ-НЕ соединен с выходом первого элемента И-ИЛИ-НЕ, выходы четвертого и пятого элементов И-ИЛИ-НЕ подключены соответственно к девятым и десятым входам второго и третьего элементов И-ИЛИ-НЕ.

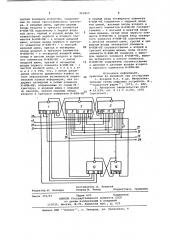

На чертеже представлена схема 35 ячейки памяти для буферного регистра.

Ячейка памяти содержит элементы

И-ИЛИ-НЕ 1-3 с элементами И 4-12, образующие трехстабильный триггер ячейки, и элементы И-ИЛИ-НЕ 13 и 14 . 4Q с элементами И 15-18, образующие

Rs -триггер ячейки. Ячейка памяти со держит. также входные шины 19-28 (с первой 19 по десятую 28).

Первые входы элементов И-ИЛИ-НЕ 45

1 и 3 подключены к шине 19, первый и второй входы элементов И-ИЛИ-НЕ 1 и 2 соответственно к шине 20, вторые входы элементов И-ИЛИ-НЕ 1 и 3 — к шине 21, третьи и четвертые входы элементов И-ИЛИ-HE 2 и 3 — к шине 22, пятые и шестые. входы элементов И-ИЛИНЕ 2 и 3 - к шине 23. Третий и четвертый входы элемента И-ИЛИ-НЕ 1 подключены к шине 24. Седьмые входы элементов И-H)IH-HE 2 и 3 и первый вход элемента И-ИЛИ-НЕ 13 соединены с шиной 25, восьмые входы элементов

И-ИЛИ-HE 2 и 3 - с шинами 26 и 27, пятый вход элемента И-ИЛИ-НЕ 1 и второй вход элемейта И-ИЛИ-НЕ 13 подключены к шине 28, третий и четвертый входы элемента И-ИЛИ-HE 13 соответственно к шинам 20 и 21.

Вход элемента И-ИЛИ-НЕ 14 соединен о выходом элемента И-ИЛИ-НЕ 1, выходы элементов И-ИЛИ-НЕ 13 и 14 подключены соответственно к девятым и десятым входам элементов И-ИЛИ-НЕ

2 и 3.

Ячейка работает следующим образом.

Трехстабильный триггер ячейки памяти имеет следующие состояния, которые определяются значениями на выходах элементов 1-3: OII — информация в ячейке стерта;.. IIO — в ячейке записана 1 ; IOI — в ячейке записан 0 .

Состояния Яз-триггера, которые оп ределяются значениями на выходах элементов 13 и 14 соответствуют:

OI — ячейка находится в режим параллельной записи; I0- ячейка находится в режиме сдвига.

В режиме параллельной записи запись информации в определенную ячейку регистра по шинам 26 и 27 через элементы И 9 и 12 происходит только после того, как (i+1) — ÿ ячейка переходит в режим сдвига и информация в ней стерта. После того, как информация в трехстабильный триггер записана и на выходе его элемента 1 устанавливается 1, RS-триггер переходит в состояние IO, т.е. ячейка будет работать в режиме сдвига.

При этом изменение состояний трехстабильного триггера i-й ячейки в режиме сдвига происходит также, как и в известной, за исключением того, что информация, полученная ею в режиме параллельной записи, стирается после того, как передана в (1+1)-ю ячейку, независимо от состояния трехстабильного триггера (1+1)-й ячейки (последняя в это время находит ся в режиме параллельной записи). ((S-триггер 1-й ячейки возвращается в состояние OI (режим параллельной записи) после того, как в этот режим переходит (i-.1)-я ячейка, а информация в трехстабильном триггере i-й ячейки стерта. Таким образом, процесс перехода ячеек буферного регистра в режим параллельной записи распространяется последовательно от первой ячейки к последней, а процесс перехода ячеек в режим сдвига распространяется также последовательно, но в обратном направлении — от последней ячейки к первой.

Буферный регистр, построенный на основе описанных ячеек памяти, позволяет осуществлять параллельную запись информации в регистр его целесообразно использовать для преобразо. вания параллельного кода в последовательный.

Формула изобретения

Ячейка памяти для буферного регистра, содержащая первый, второй и

905860

2S 9

21

РЯ

2Ф

Составитель В. Рудаков

Техред М. Тепер Корректор A. Гриценко

Редактор К. Волощук

Заказ 375/67

Тираж 623 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 третий элементы И-ИЛИ-НЕ, соединенные по схеме трехстабильного триггера, и входные шины, причем первые входы второго и третьего элементов

И-ИЛИ-НЕ подключены к первой входной шине, первый и второй входы соответственно первого и второго элементов И-ИЛИ-НŠ— к второй входной шине, вторые входы первого и третьего элементов И-ИЛИ-Н вЂ” к третьей входной шине, третьи и четвертые 10 входы второго и третьего элементов

И-ИЛИ-НŠ— к четвертой входной шине, пятые и шестые входы втсрого и третьего элементов И-ИЛИ-НŠ— к пятой . входной шине, третий и четвертый ,входы первого элемента И-ИЛИ-НŠ— к шестой входной шине, о т л и ч а ющ а я с я тем, что, с целью расширения области применения ячейки за счет обеспечения воэможности параллельной записи информации, она содержит четвертый и пятый элементы

И-ИЛИ-HE соединенные по схеме RS— триггера, и входные шины с седьмой по десятую, причем седьмые входы второго и третьего элементов И-ИЛИ-HE и первый вход четвертого элемента

И-ИЛИ-НЕ соединены с седьмой входной шиной, восьмые входы второго и третьего элементов И-ИЛИ-НЕ соответственно — с восьмой и девятой вход- ными шинами, пятый вход первого эле-. мента И-ИЛИ-HE и второй вход четвертого элемента И-ИЛИ-НЕ подключены к десятой входной шине, третий и чет вертый входы четвертого элемента

И-ИЛИ-НЕ соответственно к второй и третьей входным шинам, вход пятого элемента И-ИЛИ-НЕ соединен с выходом первого элемента И-ИЛИ-НЕ, выходы четвертого и пятого элементов

И-ИЛИ-НЕ подключены сбответственно . к девятым и десятым входам второго и третьего элементов И-ИЛИ-НЕ.

Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М., Советское радио, 1973, с. 182.

2. Авторское свидетельство СССР

9 661606, кл. G 11 С 11/00, 1976 (прототип) .