Устройство для измерения параметров конденсаторов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик р11905878 (61) Дополнительное к авт. свид-ву (22) Заявлено 200580 (21) 2927103/18-21 с присоединением заявки Йо (23) Приоритет

Опубликовано 150 28 2 Бюллетень Мо 6

Дата опубликования описания 150 282 р М К1з

G 01 R 27/26

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 337 (088. 8) И,.Ю. Сергеев, В.И. Губарь, В.N. Лунин, Н.М. Павлишин, B.Ñ. Артеменко, В.Й. Русин и В.К. Рощин

\ t

)

Киевскнй ордена Ленина политехни еский институт им. 50-летия Великой Октябрьской < оциалис гической революции (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ

КОНДЕНСАТОРОВ

20

Изобретение относится к информационно-измерительной технике и автоматическому управлению и может быть использовано при построении различных информационно-измерительных систем и систем автоматического контроля.

Известен .преобразователь, используемый при построении информационноизмерительных систем, представляющий собой преобразователь кода в напряжение интегрирующего типа, использующие в процессе преобразования итерационную аддитивную коррекцию погрешностей. Основными блоками являются интегратор, схемы выборки-хранения и ключи. 3а счет использования в этих структурах итерационной аддитивной коррекции погрешности достигается высокая точность преобразования при относительной простоте устройства и сравнительно низким требованиям к элементам и блокам, входящим в их состав (1).

Недостатком этого преобразователя является ограниченность функциональных возможностей, в частности, невозможность преобразования емкости в напряжение и определения тан. генса угла диэлектрических потерь.

Наиболее близким по технической сущности к предложенному является функциональный преобразователь,содержащий интегратор, с подключенными к его входу первым и вторым ключами, схему выборки-хранения, включенную между выходами интегратора и преобразователя, источник эталонного напряжения и устройство управления, соединенное с первым и вторым ключами и со схемой выборки-хранения, третий ключ, подключенный к источнику эталонного напряжения, первому ключу и устройству управления, четвертый ключ, подключенный к выходу преобразователя, второму ключу и устройству управления, а также два конденсатора, один из которых подклю. чен к первому ключу, а второй — к второму ключу. функциональный преобразователь работает циклично. Каж.дый цикл состоит из поочередных замыканий в Обратной цепи (сначала ключа, который соединен с выходом преобразователя„ а затем ключа, соединенного со входом интегратора), прямой цепи (сначала ключа, который соединен с выходом преобразователя, а затем ключа, ".îåäèíåííîãî со входом интегратора), а также ключа в

905878 схеме выборки-хранения. Этот преобразователь может быть использован для преобразования емкости или отношения двух емкостей в напряжение, а также для получения экспоненциальной зависимости выходного напряжения от входного кода (2}.

Недостатком известного функцио,нального преобразователя является низкое быстродействие и ограниченные функциональные возможности. l0

Цель изобретения — повышение быстродействия и расширение функциональных возможностей устройства.

Поставленная цепль достигается тем, что в устРойство измерения парамет- f5 ров конденсаторов, содержащее последовательно соединенные источник эталонного напряжения, первый и второй ключи, интегратор, блок выборкихранения, а также третий и четвертый ключи, два конденсатора и блок управления, причем выход блока выборки-хранения через третий и четвертый ключи соединен с другим входом интегратора, первый конденсатор соединен с выходом первого ключа, второй — с выходом третьего ключа, блок управления соединен с первым, третьим и четвертым ключами, с блоком выборки-хранения, введены коммутатор, два запоминающих блока, вычислитель и формирователь калибровочных сдвигов, причем выход блока выборки-хранения через коммутатор соединен со входами первого и второго запоминающих блоков, выход первого запоминающего блока соединен с первым выходным зажимом устройства и первым входом вычислителя, выход второго запоминающего блока соеди нен с другим входом вычислителя, вы- 4Р ход которого соединен со вторым выходным зажимом, а управляющие входы коммутатора, запоминающих блоков, вычислителя, формирователя калиброванных сдвигов, выходом соединенного со 45 вторым ключем, соответственно соединены с выходами блока управления.

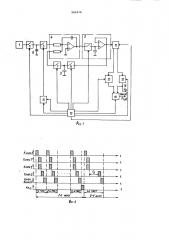

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 и 3 — временные диаграммы работы ключей. устройство содержит источник 1 эталонного напряжения, ключи 2 и 3, интегратор 4, блок 5 выборки-хранения, ключи б и 7, конденсаторы 8 и 9, 5 блок 10 управления, коммутатор 11, запоминающие блоки 12 "14, формирователь 15 калиброванных сдвигов,,измерительную камеру 16. Вычислитель может представлять собой логарифма- 60 тор либо вычитающее и делительное устройство в зависимости от выбранного алгоритма работы. Формирователь калиброванных сдвигов представляет собой управляемую линию задержки.

Устройство работает B два цикла, каждый из которых состоит из нескольких тактов. В каждом такте первого цикла осуществляется заряд конденсатора 9 выходным напряжением блока 5 выборки-хранения с последующим разрядом на вход интегратора 4; заряд конденсатора 8 от источника 1 эталонного напряжения с последующим разрядом на вход интегратора 4; выборка ,выходного напряжения интегратора 4 блоком выборки †хранен 5 с последующим запоминанием в течение следующего такта.

Временная диаграмма работы ключей в первом цикле (1-й цикл) приведена на фиг. 2. Здесь импульсы соответствуют времени замыкания соответствующих ключей. Предположим, перед началом преобразования напряжение на выходе блока выборки †хранен 5 V a заряды на конденсаторах 8 и 9 равны нулю. При замыкании ключа 6 на время

Т конденсатор 9 заряжается. При последующем замыкании ключа 7 конденсатор разряжается на интегратор, тем самым изменяется напряжение на выходе интегратора 4. При замыкании ключа 2 на время Т происходит заряд конденсатора 8. При замыкании ключа

3 на время Т (ключ 3 замыкается строго в момент размыкания ключа 2), при достаточно большом Т, конденсатор разряжается на интегратор, тем самым изменяется напряжение на выходе интегратора 4. При замыкании ключа блока 5 выборки-хранения производится выборка и запоминание выходного напряжения интегратора 4, в результате чего появляется напряжение на выходе блока 5 выборки-хранения.

По окончании -ного такта напряжение на выходе схемы выборки-хранения 5 станет

1I =йи Ч =с й1.

На практике процесс заканчивается за 4-6 тактов. При и -б после окончания шестого такта 1-ro цикла блок управления вырабатывает команду,k„. по которой выходное напряжение с помощью коммутатора 11 записывается в запоминающий блок 12 (см. фиг. 2).

Если конденсатор 9 эталонный, то напряжение на выходе запоминающего блока 12 пропорционально емкости конденсатора 8.

Второй цикл работы устройства необходим для определения тангенса угла диэлектрических потерь конденсатора 8 (в качестве которого может быть исследуемый конденсатор). Во втором цикле (диаграмма работы ключей представлена на фиг. 3) устройст во работает аналогично предыдущему циклу. Последовательность замыкания ключей внутри такта сохраняется.

Отличие состоит в том, что момснты

905878 (5) размыкания ключа 2 и замыкания ключа 3 разнесены во времени на интервал Tс, (см. фиг. 3). Сдвиг на время ,T,îñóùåñòâëÿåòñÿ формирователем

15 калиброванных сдвигов, который может представлять собой в простей- 5 шем случае линии задержки на RC-цепочках или одновибраторы. Формирователь временных сдвигов имеет два входа — информационный и управляющий. В первом цикле импульс на от- !О ,крывание ключа 3 проходит без задержки. Во втором цикле блок управления 10 вырабатывает сигнал, который подается на управляющий вход формирователя 15 временных сдвигов и импульс на открывание ключа 3 задерживается на время Тв . Во время Т ключи 2 и 3 разомкнуты и конденсатор 8 разряжается через собственное сопротивление утечки Rgg . Напряжение 20 на выходе блока 5 выборки-хранения

U по команде блока управления k« выл с помощью коммутатора 11 записывается в запоминающий блок 13 после окончания шестого такта 11-го цикла.

То (1 (), С (2)

Sex Из выражения (2) можно получить

Тв

C,„Veri

I вы

Тангенс угла диэлектрических потерь определяется как

t)5шв„,с, (3)

35 где и) — частота переменного тока, на которой работает конденсатор.

Или

Овых

Cè Uó ó

ы) т. 40

Используя в качестве вычислительного устройства логарифматор, íà его выходе получается напряжение, пропорциональное тангенсу угла диэлектрических потерь конденсатора 8. Про-45 нормировав его теперь по требуемой частоте (d и измерив, получаем, Если не требуется высокая точность определения tg F, то формуру (3) можно заменить приближенной. 50

Ue -.U e ., 4 а/ = — ° sa ((То > Ивыу Usw»

I ,где k

То

Таким образом, логарифматор можно 55 заменить вычитающим и делительным блоками.

Введение и устройство коммутатора, двух запоминающих блоков вычислителя, формирователя калиброванных сдвигов с соответствующими св яз ями отличают предлагаемое устройство измерения параметров конденсаторов от известного, поскольку расширены его функциональные возможности; устройство может быть использовано для определения тангенса угла диэлектрических потерь конденсаторов. Эта характеристика важна для определения сферы использования данного типа конденсаторов и для разбраковки некондиционных конденсаторов внутри партии.

Формул а и з обре те н и я устройство для измерения параметров конденсаторов, содержащее последовательно соединенные источник эталонного напряжения, первый и второй ключи, интегратор, блок выборки-хранения, а также третий и четвертый ключи, два конденсатора и блок управления, выход блока выборки-хранения через третий и четвертый ключи соединен с другим входом интегратора, первый конденсатор соединен с выходом первого ключа, второй — с выходом третьего ключа, блок управления соединен с управляющими входами первого, третьего и четвертого ключей, и блоком выборки-хранения, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей, в него введены коммутатор, два запоминающих блока, вычислитель и формирователь калиброванных сдвигов, причем выход блока выборки-хранения через коммутатор соединен со входами первого и второго запоминающих блоков",выход первого запоминающего блока соединен с первым выходным зажимом устройства и первым входом вычислителя, выход второго запоминающего блока соединен с другим входом вычислителя, выкод которого соединен со вторым выходным зажимом, а управляющие входы коммутатора, запоминающих блоков, вычислителя) фор. мирователя калиброванных сдвигов, выходом. подключенного ко второму ключу, соединены соответственно с выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Патент США 9 3. 346.545, 1972.

2 ° Авторское свидетельство СССР

9 679997, . G 06 G 7/26,15.04.77 (прототип).

905878

Кпама

Фиг.

Закаэ 377/67

Тираж 718 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель Л. Сотникова

Редактор К. Волощук Техред М. Тепер Корректор A. Гриценко