Регенератор импульсов

Иллюстрации

Показать всеРеферат

Союз Советсинк

Соцналнстнческнк

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1905991 (6l ) Дополнительное к авт. свид-ву (22) Заявлено 230580 (2I ) 2927818/18-21 с присоединением заявки йй (23) Приоритет

Опубликовано 150282. Бюллетень Юю 6

Дата опубликования описания 1502И (51) М. Кл.

Н 03 К 3/64

3Ьеударетвеиаый комитет

СССР па делам иэобретеиий и атерытий о (53) УДК621.395..4 (088.8) (72) Автор изобретения

В.Д.Десятков

Одесский отдел Центрального научно-HccaegoaaWNÔ oà (7 I ) Заявитель института связи (54) PEI EHEPAT0P ИМПУЛЬСОВ

Изобретение относится к импульсной технике и может быть использовано в устройствах связи, в частности в качестве устройства для автоматической регулировки усиления в регенераторе сигналов с импульсно-кодовой модуляцией.

Известны регенераторы импульсов, содержащие усилитель и решающее устройство (13.

Недостатком их является малая помехозащищенность.

Наиболее близким к изобретению является регенератор импульсов, который содержит усилитель с управ— ляемым коэффициентом усиления, выход которого соединен со входами первого и второго решающих устройств с памятью, другие входы которых подключены к источнику тактовых импульсов, а выходы по„LK„.ïîчены ко вхо-, дам логической памяти, выход кото— рой через интегратор соединен с управляющим входом усилителя с переменным коэффициентом усиления.

В процессе автоматического регулиро вания, если импульсы проходят через оба решающих устройства, то коэффициент усиле ния усилителя умень—

5 шается, если импульсы проходят только через первое решающее устройство, то коэффициент усиления усилителя увеличивается. Поскольку величина порога второго решающего устройства

10 выбирается вдвое большей величины порога первого решающего устройства, то первое решающее устройство работает в onтимальном режиме t21.

Недостатком известного устройст— ва является снижение помехозащищенности при наличии межсимвольных влияний.

Цель изобретения — повьппение помехозащищенности регенератора импульсов.

Поставленная цель достигается тем, что в регенератор импульсов, содержащий усилитель, выхоп которого

90599

45 соединен со входами перно ".. и вто,рого решающих ус "ройстн... ругие входы кстэрых подключены к источни.ку тактовых импульсов, а выход второго решающего устройства подключен к первому входу первого блока памяти, выход которого соединен со входом первого интегратора, введены вторые блок памяти и интегратор, первый и второй ключи, формирователь lð записи, элемент ИЛИ, решающее устройство второго канала, анализатор чередования и третий блок памяти, причем первые два входа третьего блока памяти и анализатора чередования, а также входы элемента ИЛИ соединены с выходами первого решающего устройства и решающего устройстна второго канала, выход первого решающего устройства соединен со входом формирователя записи, инверсный выход усилителя соединен со входом решающего устройства второго канала, другой нход которого, а также- третий вход третьего блока памяти соединены д с выходом источника тактовых импульсов, два выхода третьего блока памяти соединены со вторыми двумя входами анализатора чередования, первый из которых подключен к дополнительному входу формирователя записи, два выхода которого подключены ко вторым входам первого и второго блоков памяти, выходы которого подсоединены соответственно через первые и вторые интеграторы и ключи к управляющему входу усилителя, кроме того, первый вход второго блока памяти соединен с выходом второго решающего устройства, инверсный и

4Р прямой выходы элемента ИЛИ соединены с управляющими входами первого и второго ключей соответственно, а пер— вый и второй выходы анализатора чередования соединены с дополнительными входами первого решающего устройства и решающего устройства второго канала соответственно.

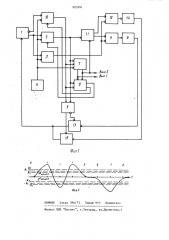

На фиг. l представлено устройство, блок-схема; на фиг. 2 — кназитроичный сигнал. 50

Г е нера тор имп уль с ов выполнен по двухканальной схеме и содержит усилитель 1 с уп равляемым коэффициентом усиления, выход которого соединен сс входами первого 2 и второго 3

55 решающих устройств, другие входы которых подключ епы к источнику 4 тактовых импульсов, я выход второго

1 Д решающего устройства 3 подключен к первому входу блока 5 памяти, выход которого соединен со входом первого интегратора 6, причем первые два входа третьего блока 7 памяти и анализатора 8 ч ер едования, а также в ходы элемента HJIH 9 соединены с выходами первого решающего устройства 2 и решающего устройства 10 второго канала, кроме того, выход первого решающего .устройства 2 соединен со входом формирователя 11 записи, инверсный выход усилителя 1 с управляемыми коэффициентом усиления соединен сс входом решающего устройства 10 второго канала, другой вход которого, а также третий вход третьего блока памяти соденинен с выходом источника 4 тактовых импульсов, дна выхода третьего блока 7 памяти соединены со вторыми двумя входами ана †лизатора 8 чередования, причем один из них подключен к дополнительному входу формирователя !l записи, два выхода которого подключены ко вторым входам первого 5 и второго 12 блоков памяти, выходы которых соединены соответственно через первый интегратор 6, первый ключ 13, нто— рой интегратор 14 и второй ключ 15 к унранляющему входу усилителя 1 с управляемым коэффициентом усиления, кроме того, первый вход второго блока 12 памяти соединен с выходом второго решающего устройства 3, инверсный и прямой выходы элемента

ИЛИ 9 соединены с управляющими входами первого 13 и второго 5 ключей соо тв е тс тв енно .

Работа устройства поясняется фиг. 2, где изображен квазитроичный сигнал на выходе усилителя 1 с управляемым коэффициентом усиления. Уровень «+А! соответствует порогу реше ния в известном устройстве, уровни

+А2 и +АЗ соответствуют порогам решения в данном устройстве. Первые блок памяти 5 и интегратор 6 формируют уровень порога А2, в том случае, если предыдущий символ был "0".

При этом на выходах решающих устройств 2 и 10 "нули", открывается первый ключ 13 и величина усиления усилителя с переменным коэффициентом усиления устанавливается согласно уровню порога А2. Если последующий символ 1", то, напр гчер, на выходе первого решающего устройства

2 формируется "1", которая с помощью, 5 905991 формирователя записи 11 коммутируется на первый блок памяти 5 и разрешает считывание информации со второго решающего устройства 3.

Второй блок 12 памяти и интегратор 14 формируют уровень порога АЗ в том случае, если предыдущий символ "1". При этом, например, на выходе первого решающего устройства второго канала "1", открывается 10 второй ключ 15 и величина усиления усилителя I с переменьим коэффициентом усиления устанавливается согласно уровню порога А3. Если последующий символ I" (т. е. кодовая комби- !5 нация "11 ), то на выходе первого решающего устройства 2 формируется

1I II которая комм утируется с помощью формирователя 1 1 записи на в торой блок памяти 1 2 и разрешает 20 считывание информации со второго решающего устройства 3.

Уровни порогов решения хранятся в первом 6 и втором 14 интеграторах, выходы которых подключаются к управ- 25 ляющему входу усилителя с управляемым коэффициентом усиления с помощью первого IЗ и второго 15 ключей соответственно по следующему алгоритму: после каждого принятого 5р

11 Н

0 следующее решение принимается с помощью порога А2, после каждой принятой "1" следующее решение принимается с помощью порога А3.

Таким образом, в устройстве при 35 кодовых комбинациях "01" и "11" существуют две независимых системы

АРУ, причем Al А2=АЗ, если межсимвольные влияния отсутствуют и и

А2 >Аl АЗ, если межсимвольные влия- gp c ния имеются.

Формула изобретения

Регенератор импульсов, содержащий усилитель, выход которого соединен со входами первого и второго решающих устройств, другие входы которых подключены к источнику тактовых им50 пульсов, а выход второго решающего устройства подключен к первому входу

6 первого блока памяти, выход которого соединен со входом первого интегратора, отличающийся тем, что, с целью повышения помехоэащищенности, в него введены вторые блок памяти и интегратор, первый и второй ключи, формирователь записи, элемент ИЛИ, решающее устройство второго канала, анализатор чередования и третий блок памяти, причем первые два входа третьего блока памяти и анализатора чередования, а также входы элемента ИЛИ соединены с выходами первого решающего устройства и решающего устройства второго канала, выход первого решающего устройства соединен со входом формирователя записи, инверсный выход усилителя соединен со входом решающего устройства второго канала, другой вход которого, а также третий вход третьего блока памяти соединены с выходом источника тактовых импульсов, два выхода третьего блока памяти соединены со вторыми двумя входами анализатора чередования, первый иэ которых подключен к дополнительному входу формирователя записи, два выхода которого подключены ко вторым входам первого и второго блоков памяти, выходы которых подсоединены соответственно через первые и вторые интеграторы и ключи к управляющему входу усилителя, кроме того, первый вход торого блока памяти соединен с выходом в торо г о р ешающег о ус тр ойс тв а, инверсный и прямой выходы элемента

ИЛИ соединены с управляющими входами ервого и второго ключей соответтвенно, а первый и второй входы анализатора чередования соединены с дополнительными входами первого решающего устройства и решающего устройства второго канала соответственно.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9352366, кл. Н 03 G 3/00, 1971.

2. Авторское свидетельство СССР

У632064, кл. H 03 К 3/64, 1976 (прототип).