Интегральный динамический элемент

Иллюстрации

Показать всеРеферат

Союз Соввтскик

Соцяаяистмчвскмк

Рвсвубямк

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()906005 (41) Дояолммтеаьмое к ввт. свмд-ву И 559381 (22)Заявасмо19.05.80 (2l) 2925136/18-21 с ермсоedмкeмкee заявкм М (23) Прмормгет—

Ояублмковано 15.02.82. Вкшлстень М 6 (51jM. Кл.

Н 03 К 19/08

H 03 K 19/20

Н 03 K 3/286

Н 03 K 19/088 (53) УДК621. 375. .083(088.8) фвудзрстевввв кеввтвт

ВЮВР щ дввкв «м4регеей в вяфьпвм

Дата ояубанковвмяя оамсаммя 15 ° 02 82 (72) Авторы

«зобрете ням

Л. К. Самойлов, В. В. Гайворонский и С. В, Левонюк

I

t (73) 3вявятсль Таганрогский радиотехнический институт им. В. Д.. Калмыкова. (54) ИНТЕГРАЛЬНЫЙ ДИНАИИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к вычислительной технике и предназначено для построения интегральных схем обработки и хранения информации. йо основному авт. св. я 559381 известен динамический элемент, состоящий из триггера с непосредственными коллекторно-базовыми связями на двух транзисторах, причем один из них многоэмиттврный (НЭТ), Один из змиттеров

ИЭТ и эмиттер другого транзистора подключен к мине тактовых импульсов, базы транзисторов через токозадащие резисторы соединены с виной питания, коллекторы транзисторов являются выходами, а незадействованные в схеме эмиттеры ИЭТ - входами устройства.

С базой многоэмиттерного транзистора соединен анод диода фиксации, катод которого подключен к, источнику опорного напряжения. Данный элемент реалызует логические функции И и И-НЕ (в положительной логике ) соответственно на прямом и инверсном выходах 513 .

Недостатком известного устройства являются узкие функциональные возможности.

Цель изобретения - расширение функциональных возможностей интегрального динамического элемента, а именно обеспечение реализации логических функций и-а И-2ИЛИ, и m H-2ИЛИ-НЕ с задержкой в полпериода тактовых импульсов, где и и m число входов

Групп И.

Поставленная цель достигается тем, что в устройство введены третий транзистор и четвертый многоэмиттерный транзистор, база которого подключена к коллектору третьего транзистора и аноду диода Фиксации, а один из эмиттеров подключен к шине тактовых им- пульсов и эмиттеру третьего транзистора, база которого подключена к коллектору четвертого многоэмиттерного транзистора и через резиСтор к шине питания> причем остальные эмиттеры четвертого многоэмиттерного транзис906005 тора подключены к дополнительным входам устройства.

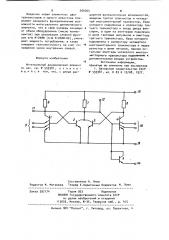

На чертеже представлена принципиальная электрическая схема устройства. S

Устройство содержит первый многоэмиттерный транзистор 1, второй и третий транзисторы 2 и 3, четвертый многоэмиттерный транзистор 4, диод 5 фиксации, резисторы 6, 7 и 8, входы 10

9 устройства, дополнительные входы

10 устройства, соответственно прямой

11 и инверсный 12 выходы устройства, шина 13 питания, шина 14 опорного напряжения, шина 15 тактовых импульсов. >s

Устройство работает следующим образом.

Если в исходном состоянии на шине

15 тактовых импульсов низкий уровень напряжения, логические входы 9 и 10

"отключены" и динамический элемент хранит информацию. Если открыт также многоэмиттерный транзистор 1, то его коллектор вунтирует базу транзистора

2 на шину синхронизации. Транзисторы

2 и 3 закрыты, а многоэмиттерный транзистор.4 ооттккррыытт, так как ои включен параллельно многоэмиттерному транзистору 1. На выходах !1 и 12 усЗЬ танавливаются логические уровни соответственно логические "0" и "!".

При поступлении импульса напряжения на шину 15 тактовых импульсов включаются в работу эмиттеры иногоэмиттерных транзисторов 1 и 4, связанные с логическими входами. Пусть на всех входах и и в - логическая и!и, тогда все транзисторы 2 и 3, и многоэмиттерные транзисторы 1 и 4 за- . крыты по эмиттерам, Однако уровни напряжения на коллекторах транзисторов различны. Диод 5 Фиксации ограничивает напряжение на коллекторах транзисторов 2 и 3. Образуются пути токов: шина 13, резистор 6, база транзистора 2 диод 5, шина 14, а также шина 13, резистор В база, коллектор транзистора 3, диод 5 шина 14.

Данные токи создают в базах транзисторов 2 и 3 неравновесный избыточ- ® ный заряд и при окончании действия импульса на шине 15 данные транзисторы открываются, 4Т0 приводит к удержанию многоэмиттерных транзисторов 1 и 4 в закрытом состоянии. На выходах устройства .устанавливаются логическая "!" на выходе 11 и логический "О" на выходе 12.

Если при наличии высокого уровня напряжения (импульса) на шине !5 хотя бы на одном из m входсв !0 присутствует логический "0", а на всех Il входах 9 — логическая "1", то открыт многоэмиттерный транзистор 4, а много эмиттерный транзистор l и транзисторы 2 и 3 закрыты. Образуется путь тока: шина !3 резистор 6, база, коллектор транзистора 2 база, эмиттер многоэмиттерного транзистора 4, логический вход, на котором присутствует логический "0". Этот ток создает неравновесный избыточный заряд в базе транзистора 2. При окончании действия импульса на шине 15 транзистор 2 открывается и своим коллектором шунтирует входные цепи многоэмиттерных транзисторов l и 4, которые закрываются, а транзистор 3 открывается.

На прямом выходе 11 устанавливается логическая "1", на инверсном выходе l2 - логический "0".

Поскольку схема симметрична относительно входных сигналов, то и вариант, когда на всех m входах !Ологическая "1", а хотя бы на одном из и входов 9 - логический "0", также приводит к результату предыдущего варианта, т. е. в режиме хранения на выходе ll логической "!", на выходе 12 - логического "О".

Если we хотя бы на одном из п входов 9 присутствует логический "0", и хотя..бы на один из m входов !О подан логический "О", то при подаче импульса напряжения на шину 15 открывается многоэмиттерный транзистор 1, при этом транзистор 2 закрывается цодачей запирающего напряжения на переход база - эмиттер. Иногоэмиттерный транзистор 4 также открывается, а транзистор 3 закрывается. При переходе к режиму хранения состояние элемента фиксируется. На выходе 11 устанавливается логический "О", а на выходе

l2 - логическая "1".

Следовательно, как видно из принципа действия устройства, установка нового состояния производится после окончания действия импульса напряжения на шине тактирования, т. е. прИ двухфазной системе синхронизации задержка выполнения логической функции составляет полпериода тактовых импульсов, реализуемая функция при этом на выходе 11 и-m И.-2ИЛИ, а на выходе !

2 и-в И-2ИЛИ-НЕ, 90600

Составитель А. Янов

Редактор И. Митровка Техред Е.Харитончик Корректор М ° Пожо

Тираж 953 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Заказ 397/74 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Введение новых элементов: двух транзисторов и одного резистора позволяет расширить функциональные возможности интегрального динамического элемента, что в свою очередь сокраща- S ет объем оборудования (число компонентов) при реализации сложной функции и-m И-2ИЛИ (n-в И-2ИЛИ-НЕ), уменьшает мощность потребления; а также повышает технологичность за счет сокращения числа внутренних связей.

Формула изобретения

Интегральный динамический элемент по авт. св. М 559381, о т л и ч а ю шийся тем, что, с целью рас5 б ширения функциональных возможностей, введены третий транзистор и четвертый многоэмиттерный транзистор, база которого подключена к коллектору тре тьего транзистора и аноду диода фиксации, а один из эмиттеров подключен (к шине тактовых импульсов и эмиттеру третьего транзистора, база которого подключена к коллектору четвертого многоэмиттерного транзистора и через резистор к шине питания, причем остальные эмиттеры четвертого многоэ» ,миттерного транзистора подключены к дополнительным входам устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР.

11 559381, кл. Н 03 К 19/08, 1977.