Делитель частоты импульсов

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцналнстнческнв

Рес ублнн

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свнд-ву И 675603 (22) Заявлено 20. 05. 80 (21) 2926060/18-21 с присоединением заявки JCt (23) Приоритет—

Опубликовано 15.02.82. бюллетень М 6

Дата опубликования описания 15.02.82 (5 l ) N. Кл.

Н 03 К 23/02

РвударстввнвыФ кемктвт

СССР ае двлвн кэварвтвкий н втврытМ (53) УДК621.374 ° .3(088.8). (72) Авторы изобретения

А. M Воловик, А. В. Павлов и В. П. Грибок-0 с (7I) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИНПУЛЬСОВ

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники.

Ilo основному авт. св. И 675603 известен делитель частоты импульсов, содержащий элемент И-НЕ, один вход которого соединен с входной шиной, второй вход которого через элемент

НЕ соединен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика им15 пульсов и выходной шиной делителя, при этом выход дешифратора соединен с единичным входом триггера, нулевой вход которого подключен к входной ши- не 11.

Недостаток известного устройстваограниченные функциональные возможности, так как устройство работает только в том случае, если счетчик импуль сов срабатывает по заднему фронту входного импульса.

Цель изобретения - расаирение функциональных возможностей.

Цель достигается тем, что в делитель частоты импульсов, содержащий логический элемент И-НЕ, один вход которого соединен с входной анной, второй вход которого через логический элемент НЕ соединен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика импульсов и выходной шиной делителя и нулевой вход триггера подключен к входной шине, введен дополнительный логический элемент

И-НЕ, первый вход которого подключен к выходу логического элемента И-НЕ; элемента 2 во время действия (К+1) -го входного импульса. По переднему Фрон ту (К+1)-гo входного импульса триггер 3 устанавливается в единичное состояние, так как на его входе нулевой потенциал, а на единичном входе единичный потенциал. Нулевой сигнал с ну3 906007 второй вход - к выходу дешифратора, а выход - к единичному входу триггера.

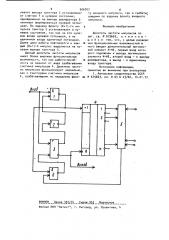

На чертеже представлена структурная схема устройства.

Устройство содержит логический элемент 1 И-НЕ, логический элемент

2 НЕ, RS триггер 3, счетчик 4 импульсов, дешифратор 5, дополнительный логический элемент б И-НЕ. 1О

Делитель частоты импульсов работает следующим образом.

Счетчик 4 увеличивает свое содержимое на единицу по заднему фронту входного положительного импульса.

8 исходном состоянии счетчик 4 в нулевом состоянии, а триггер 3 устанавливается в нулевое состояние нулевым потенциалом входного сигнала, 20 при этом на вине сброса счетчика 4 единичный потенциал, на единичном выходе триггера 3 - нулевой потенциал, который поддерживает на выходе элемента 2 единичный, разрешающий прохождение входных импульсов нв вход счетчика 4 потенциал. На входы девифратора 5 подается прямой код управления коэффициентом деления на единицу меньший, чем требуемый коэффициент деления частоты импульсов, 30

Дешифратор 5 осуществляет сравнение кода управления коэффициентом с содержимым счетчика 4. При равенстве кодов на выходе деаифратора 5 формируется единичный потенциал, а в случае неравенства кодов на выходе дешифратора 5 присутствует нулевой потенциал.

Таким образом, каждый входной импульс, прошедший через элемент 1, по . заднему Фронту положитсльного входного импульса увеличивает содержимое счетчика 4 на единицу и по заднему фронту входного импульса подтверждаетея нулевое состояние триггера 3; йжле прихода k-ro входного импульса гю его заднеиу фронту содержимое счетчика 4 становится равным коду управления коэффициентом деления K.

При этом на выходе девифратора 5 фор- о иируется единичный потенциал, который поступает на второй вход элемента 6, на первом входе которого это время - высокий потенциал, поступающий с выхода элемента 1. Передний фронт отрицательного сигнала с выхода элемента 6 устанавливает на единичном выходе триггера 3 высокий потенциал, а на нулевом выходе триггера 3 также высокий потенциал, поддерживаемый нулевым потенциалом паузы между К и (К+1) входными импульсами, Следующий, (К+!) -й входной импульс не проходит на вход счетчика 4, так нак на втором входе элемент 1 присутствует нулевой потенциал с выхода элемента 2 во время действия (К+1)го входного импульса. По переднему фронту (К+!) -го входного импульса триггер 3 устанавливается в единичное состояние, так как на его нулевом входе нулевой потенциал, а на единичном входе единичный потенциал. По заднему фронту (K+1)-го импульса триггер 3 устанавливается в нулевое состояние. Состояние всех элементов устройства совпадает с исходным. Далее цикл работы повторяется.

Счетчик 4 увеличивает свое содержимое на единицу по переднему фронту входного г1оложительного импульса.

Каждый входной импульс, проведший через элемент 1 по переднему фронту положительного входного импульса, увеличивает содержимое счетчика 4 на единицу и по заднему фронту входного импульса подтверждает нулевое состо яние .триггера 3. По переднему фронту

К-ro входного импульса содержимое счетчика 4 становится равным коду управления коэффициентом деления К.

При этом на выходе деаифратора 5 образуется высокий потенциал. Только по заднему фронту К-го импульса на выходе элемента 6 начинает формироваться нулевой потенциал, так как на обоих входах элемента 6 присутствуют высокие потенциалы. Передний фронт отрицательного сигнала с выхода элемента 6 устанавливает на единичном выходе триггера 3 высокий потенциал, а на нулевом выходе триггера 3 также высокий потенциал, поддерживаемый нулевым потенциалом паузы между К и (К+1)-ым входными импульсами.

Следующий (К+1) -й входной импульс не проходит на вход счетчика 4, так как на втором входе элемента 1 присутствует нулевой потенциал с выхода

5 9060 левого выхода триггера 3 устанавливает счетчик 4 в нулевое состояние, одновременно на выходе дешифратора 5 начинает формироваться нулевой потенциал. flo заднему фронту (K+1) -го импульса триггер 3 устанавливает в нулевое состояние, так как на его нулевом входе нулевой потенциал, а на единичном входе единичный потенциал.

Далее цикл работы повторяется и каж- 10 дый (К+1)-й импульс выделяется на нулевом выходе триггера 3.

Данный делитель частоты импульсов имеет более широкие функциональные возможности, так как работоспособ- 1% ность не зависит от вида срабатывания счетчика импульсов 4 ° Делитель частоты импульсов функционирует нормально, как с триггерами счетчика импульсов

4, срабатывающими по переднему фрон- 2о

07 6 ту входного импульса, так и срабатывающими по заднему Фронту входного импульса.

Формула изобретения

Делитель частоты импульсов по авт. св. И 675603, о т л и ч а юшийся тем, что, с целью расшире ния функциональных воэможностей в него введен дополнительный логический элемент И-НЕ, первый вход которого подключен к выходу логического элемента И-НЕ, второй вход - к выходу дешифратора, а выход — к единичному входу триггера, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР.

0 675603, кл. Н 03 K 23/02, 14.01.77, 8НИИПИ Заказ 397/74 Тираж 5 Нодписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4