Устройство фазового пуска

Иллюстрации

Показать всеРеферат

Союз Советск ив

Социвлистическик

Республик

ОП ИСДНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii906017 (6I) Дополнительное к авт. свид-ву (22) Заявлено 27.05.80 (21) 2932662/1 8-09 с присоединением заявки М(23 } Приоритет

Опубликовано1 5.02.82. Бюллетень М 6

Дата опубликования описания 1 5 02 82 (51) М. Кл.

Н 04 Ь 7/02

Геоударстееиный комитет

СССР до делам нзооретеиий и открытий (.53) УДК 621.394.

° 662 (088.8) (72) Авторы изобретения

В. Н. Пряхин, П.Д. Расторгуев, Г.М. Резник и (7l) Заявитель (54) УСТРОЙСТВО ФАЗОВОГО ПУСКА

Изобретение относится к связи и мо.жет использоваться при передачи дискретных сообщений в системах сеансной связи.

Известно устройство фазового пуска, содержащее на входе декодер, информационные выходы которого через соответствующие линии задержки подключены к входам коммутатора и через первый элемент ИЛИ к информационным входам п анализаторов, к другим входам которых

10 подключены контрольные выходы декоде ра, которые через последовательно соединенные второй элемент ИЛИ и первый дополнительный элемент задержки подклю

15 чены .к соответствующему входу коммутатора, выходы которого подключены к соответствующим входам регистратора информационных кодовых комбинаций (ИКК), выход сигнала ошибки декодера объединен с соответствующими входами анализаторов и через второй дополнительный элемент задержки подключен к соответствующему входу коммутатора 13.

Однако известное устройство имеет сравнительно невысокую точность фазового пуска.

Белью изобретения является повышение точности фазового пуска, Ueab достигается тем., что в устройство введены (rn -1 ) дополнительных элементов задержки и последовательно содиненные дополнительный коммутатор, сумматор и пороговый блок, при этом выходы (ч -1) анализаторов через с0» ответствующие дополнительны з элементы задержки, а выход rn-го анализатора непосредственно подключены к входам дополнительного коммутатора, выход порогового блока подключен к управляющим входам коммутатора и регистратора ИКК.

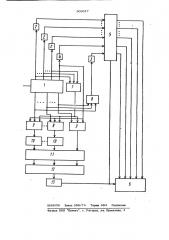

На чертеже приведена структурная схема предложенного устройства.

Устройство фазового пуска содержит декодер 1, линии 2 задержки, первый и второй иодолнительные элементы 3 н 4 задержки соответственно, коммутатор 5, регистратор 6 информационных кодовых

3 90601 комбинаций, первый и второй элементы

ИЛИ 7 и 8 соответственно, rn анализаторов 9, (w-1) дополнительных элемен» тов 10 задержки, дополнительный коммутатор 1 1, сумматор 3 2 и пороговый блок 1 3.

Устройство работает следуюшим образом.

В сеанс на вход декодера 1 поступают кодовые комбинации, используемые для tp передачи сообшений, и кодовые комбинации, определяюшие порядковые номера групп комбинаций. Сигналы декодирования с информационных выходов через первый элемент ИЛИ 7 поступают на информаци- 15 онные Входы m анализаторов 9, на дру» гие Входы KoTopbTx подаются сигналы QB» кодирования с контрольнъ х выходов декодера 1 и сигналы обнаружения ошибок с его Выхода сигнала ошибки. Кроме того,gp сигналы декодирования с информационных

Выходов декодера 1 и сигналы обнаружения ошибок с его Выхода сигнала ошибки Вводятся соответственно в линии .задержки 2 .и второй дополнительный элемент 4, а сигналы декодирования с контрольных выходов декодера 1 — через второй элемент ИЛИ 8 Вводятся В первый дополнительный элемент 3.

4 по количеству, так и по сочетанию. Суммарный сигнал в пороговом блоке 1 3 сравнивается с порогом, и в случае пре вышения на выходе порогового блока 13 появляется сигнал пуска . По этому сиг налу включается в работу регистратор 6 и замыкается коммутатор 5, обеспечивая подключение всех линий задержки 2 и первого и второго дополнительных элементов

3 и 4 на регистратор 6.

Предложенное устройство позволяет устанавливать и изменять в широком диапазоне в зависимости от помеховой обстановки и характеристики группирования ошибок в канале соотношение между вероятностями чеприема команды фазового пуска и вероятностью ложного пуска аппаратуры.

Формула изобретения

Устройство фазового пуска, содержашее на входе декодер, информационные выходы которого через соответствующие линии задержки подключены к входам коммутатора и через первый элемент ИЛИ к информационным входам m анализаторов, к другим входам которых подключены контрольные выходы декодера, которые

При правильном декодировали@ априорно известных на приеме одной из контрольнь1х комбинаций и отсутствии или необнаружении ошибок в информационных кодовых комбинациях группы на Выходе сс»

35 ответствующего анализатора 9 появляеч ся сигнал. Если сообшение содержит групп информационных комбинаций с соответствуюшими комбинациями порядкового номера контрольной комбинации во главе групп, то сигнал с выходов соответствующих анализаторов 9 появляется лишь в определенные моменты времени, соответствуюшие окончанию приема группы: для первой группы — через ВреМя 1, 45 для второй - через 2Т, для m-сй - Т.

Соответственно сигналы с выходов анализаторов 9 задерживаются в дополнительных элементах 1 0 для первого анализатора 9 на время (тл-1), для второго - на

50 (m-2) Т, для л -1 анализатора 9 - на

Т, с последнего анализатора 9 сигнал снимается без задержки. Этим обеспечивается одновременность поступления сигЭ налов с анализаторов 9 на сумматор 12.

55 С помощью дополнительного коммутатора 11 обеспечивается подключение к сумматору 12 выходных сигналов OT различных анализаторов 9 с изменением их как через последовательно соединенные второй элемент ИЛИ и первый дополнительный элемент задержки подключены к соответствующему входу коммутатора выходы которого подключены к соответствуюшим входам регистратора информационных кодовых комбинаций (ИКК), выход сигнала ошибки декодера обьединен с соответствуюшими входами л анализаторов и и через второй дополнительный элемент задержки подключен к соответствуюшему входу коммутатора, о т л и ч а ю ш е ес я тем, что, с целью повышения точности фазового пуска, введены (т -1 ) дополнительных элементов задержки и после довательно соединенные дополнительный коммутатор, сумматор и пороговый блок, при этом выходы (ю-1) анализаторов через соответствуюшие дополнительные элементы задержки, а выход т -го анализатора непосредственно подключены к входам дополнительного коммутатора, выход порогового блока подключен к управлявшим входам коммутатора и регистратора

ИКК.

Источники информации, принятые во внмание при экспертизе

1. Авторское свидетельство СССР

% 644045, кл. Н 04 4 7/02, 1976 (прототип) .