Устройство формирования сигнала отсчета для дифференциального кодера изображений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соцналнстических

Республнк

< 6906033 (61) Дополнительное к авт. свид-ву (22) Заявлено 02Л0.79 (21) 2824926/18-09 с присоединением заявки Hо(23) Приоритет

Опубликовано 150282. Бюллетень М 6

Дата опубликования описания 15.02.82

Р11М К з

Н 04 Н 7/13

Государственный комитет

СССР по делам изобретений. н открытий (53) УДК 621. 397 (088.8) (72) Автор изобретения

В ° В ° Сергеев

Краб евсина Ордена трудсво, Краснсг-,-зйад,„и . авиационный институт им. акад. С.П.Королева (71) Заявитель

„(54) УСТРОЙСТВО ФОРИН СОВАНИЯ СИГНАЛА ОТСЧЕТА

ДЛЯ ДИФФЕРЕНЦИАЛЬНОГО КОДЕРА ИЗОБРАЖЕНИЙ

Изобретение относится к радиотехнике и может использоваться при построении кодирующих устройств, прЪменяющих дифференциальное кодирование построчно развертываемых иэображений для их передачи по цифровому каналу.

Известно устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры (11.

Однако известное устройство имеет низкую точность формирования сигнала отсчета при наличии s изображении криволинейных контуров.

Цель изобретения — повьааение точности формирования сигнала отсчета при наличии в иэображении криволинейных контуров.

Цель достигается тем, что в устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры, введены восьмой блок задержки, двенадцать блоков вычисления модуля разности сигналов, третий и четвертый сумматоры, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подключен к выходу седьмого блока задержки, а к первому и второму входам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычисления, модуля разности сигналов подключены соответственно выходи второго и третьего, третьего и четвертого, четвертого и пятого первого и третьего, третьего и шестого, четвертого и седьмого, перaoro и четвертого, второго и шестого, четвертого и восьмого, первого и пятого, второго и седьмого, третьего и восьмого блоков задержки, прн этом к первому, второму н третьему входам первого, второго, третьего и четвертого сумматоров подключены соответственно выходы первого, второго и третьего четвертого, пятого и шестого седьмого, восьмого и девятого десятого, одиннадцатого и двенадцатого блоков вычисления модуля разности сигналов, выходы первого, второго, третьего и четвертого сумматоров подключены к соответствующим входам блока сравнения, первый, 906033

)0 (-, ) tlpM I a ч =1,4 Р Ч= Ч„.

1 1,4

5 (., "- )

Я(п,n) =

8 (m, n-<) 25

Формула изобретения

d0

65 второй, третий и четвертый выходы блока сравнения подключены к первым входам первого, второго, третьего и четвертого ключевых элементов соответственно, а ко вторым входам первого, второго, третьего и четвертого ключевых элементов подключены соответственно выходы первого, второго третьего и четвертого блоков задержки, причем восходы четырех ключевых элементов соединены между собой.

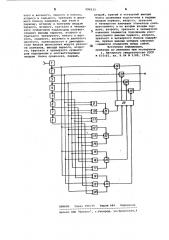

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство формирования сигнала отсчета для дифференциального кодера изображений содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки задержки

1 - 8 соответственно; первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый блоки

9-20 вычисления модуля разности сигналов соответственно; первый, второй, третий,и четвертый сумматоры 21, 22, 23 и 24 соответственно: блок 25 сравнения, четыре ключевых элемента 26, 27, 28 и 29.

Устройство работает следующим образом, На вход первого блока задержки 1 поступают отсчеты видеосигнала. С выходов всех блоков задержки 1 - 8 снимаются значения отсчетов, задержанные соответственно на один такт, на (N-l) такт, íà N тактов, на (И+1) такт, на (М+2) такта, на (2М-1) такт, на 2М тактов и на (2N+1) такт. Пусть изображение задано квадратной сеткой отсчетов s(m,n) где m - номер отсчета в строке (1 и m 4 M); n — номер строки (для простоты положим, что — ce (и а ж ), В результате построчной развертки, осуществляемой в направлении возрастания m (по отсчетам строки) и и (по строкам) и выполнения функциональных преобразований,в блоках

9-20 на выходе первого сумматора 21 имеет сигнал

У1 1Б(%+1 и 1) s(mðп 1)1 +

+ s (m,n-l)-s (m-l,п-1) +

+ s (m-l, n -1)-s (m-2, и-1)1 (l) на выходе второго сумматора 22

Y g = s (m-l),n -s (m,п — 1) I +, + s (m,ï-1)-s (пч1, и-2) I +

+ I s (m-1, и-1) -s (m,n-2) (2) на выходе третьего. сумматора 23

Yg = 1s(m-l,n)-s(m-1, и-1)! +

+ I в (в+1, и-1)-s (в+1, и-2)! +

+ I s (m-l, n-1)-s (m-l, n-2) (3) на выходе четвертого сумматора 24

Y i s (m-l, n) -s (m-2, и-1) +

+ Is(m+1, n-l)-.s(m,n-2)! +

+ I в (m, n-1)-s (m-l, и-2) l (4)

Сигналы У«У <„Y > и У< поступают соответственно на первый, второй, третий и четвертый входы блока сравнения 25. Блок сравнения 25 формирует управляющий сигнал на одном нз четырех своих выходов которому соответствует вход с наименьшим значением У; (i=1 4). Этот управляющий сигнал открывает один из ключевых элементов 26, 27, 28 и 29, которые пропускают на выход устройства значение задержанного видеосигнала с выхода соответствующего блока задержки. Таким образом получаем оценку текущего отсчета;

РРи Ч,= ï тЧ; (5)

1= 1,4

6 (@-1,ni4) РРи (".тм Ч„ . =1,4

Формирование оценки текущего отсчета в соответствии с (1) †(5) позволяет получить точное предсказание значения отсчета при пересечении в процессе развертки прямолинейных контуров, ориентированных под углами Оа, 45 о, 90ои 135 о к строке.

Таким образом, предложенное устройство формирования сигнала отсчета для дифференциального кодера изображений обеспечивает более высокую точность предсказания при пересечении в процессе развертки непрямолинейных контуров и при наличии %а изображении флуктуационной помехи.

Устройство формирования сигнала отсчета для дифференциального кодера изображений, содержащее последовательно соединенные семь блоков задержки, первый и второй сумматоры, отличающее с я . тем, что, с целью повышения точности формирования сигнала отсчета при наличии в изображении криволинейных контуров, введены восьмой блок задержки, двенадцать блоков вычисления модуля разности сигналов, .третий и четвертый сумматоры, блок сравнения и четыре ключевых элемента, причем вход восьмого блока задержки подключен к выходу седьмого блока задержки, а к первому и второму входам первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого блоков вычисления модуля разности сигналов подключены соответственно выходы второго и третьего, третьего и четвертого, четвертого и пятого, первого и третьего, третьего и шестого, четвертого и седьмого, первого и четвертого, второго и шестого, четвер906033

ВИИИПИ Заказ 399/75 Тираж 684 Подписное

Филиал IIIIII "Патент", г.ужгород, ул.Проектная,4 того и восьмого, первого и пятого, второго и седьмого, третьего и восьмого блоков задержки, при этом к первому, второму и третьему входам первого, второго, третьего и четвертого сумматоров подключены соответственно выходы первого, второго и третьего; четвертого, пятого и шестого, седьмого, восьмого и девятого> десятого, одиннаднатого и двенадцатого блоков вычисления модуля раэности сигналов, выходы первого, второго, третьего и четвертого сумматоров подключены к соответствующим входам блока сравнения, первый, второй, третий и четвертый выходы блока сравнения подключены к первым входам первого, второго, третьего и четвертого ключевых элементов соответственно а ко вторым входам первого, второго, третьего и четвертого ключевых элементов подключены соответственно выходы первого, второго, третьего и четвертого блоков задержки, причем выходы четырех ключевых

=лементов соединены между собой.

Источники информации, принятые во внимание при экспертиэе

1. Авторское свидетельство СССР

9 633162, кл. Н 04 N 5/00, 1976.