Источник калиброванных напряжений

Иллюстрации

Показать всеРеферат

СО903 Советск и к

Социалис тически к

Респубпии (iii907518

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву - 758095 (22) Заявлено 29.04.80 (2l ) 2917102/24-07 с присоединением заявки № (23) Приоритет

Опубликовано 23.02.82. Бюллетень №7

Дата опубликования описания 26.02.82

tSI)M. Кл.

005 Р- 1/44 Ьвударатынкм5 коиктвт

СССР

N шан изобретений и открытка (5З) УДК 621.316. . 722.1 (088. 8) 1 "

А. Е. Волынский, Г. В. Мирошников, Ю. А. Нечаев, С. А. Рачин и А. А. Смирнов (72) Авторы изобретения (7t) Заявитель (54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

Устройство относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. N 758095 известен источник калиброванных напряжений, содержащий блок опорного напряжения, последовательно включенные коммутатор и два блока интегрирования, преобразователь кода во временной интервал, регистр памяти, блок управления, преобразователь код-напряжение и аналоговый сумматор, в котором первый и второй входы коммутатора соответст венно связаны с выходом блока опорного напряжения и входом аналогового сумматора, а входы управления коммутатора через блок управления связаны с выходом преобразователя кода во временной интервал, первый и второй входы аналогового сумматора соответственно подключены к выходу преобразователя код-напряжение и выходу второго блока интегрирования, а выход, сумматора связан с выходом устройства, вход регистра памяти связан с входной клеммой устройства, соответствующие выходы регистра подключены к входам преобразователей код-напряжение н кода во временной интервал, а вход синхронизации регистра памяти, вход сброса, первого блока интегрирования и вход управления второго блока интегрирования соединены с,соответствующими выходами второго блока интегрирования. о

Недостатком известного устройства является его низкое быстродействие.

Цель изобретения — увеличение быстродейс твия.

Поставленная цель достигается тем, 15 что в источник калиброванных напряжений введен блок выработки сигнала сброса при изменении входного кода, второй блок интегрирования дополнительно снабжен входом сброса, а блок управления оборудован дополнительными входом и выходом, причем вход и выход блока выработки сигнала сброса связаны соответственно с входной клеммой устЭ 90751 ройства и дополнительным входом блока управления, а вход сброса второго блока интегрирования подключен к дополнительному выходу блока управления.

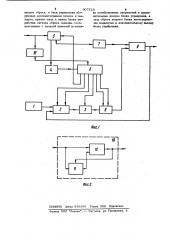

На фиг. l представлена структурная схема предлагаемого устройства; на фиг. 2 - вариант выполнения блока выработки сигнала сброса при изменении входного кода, Источник калиброванных напряжений содержит блок 1 опорного напряжения, коммутатор 2, первый блок 3 интегрирования, преобразователь 4 кода во временной интервал, регистр 5 памяти, блок 8 управления, преобразователь 7 код-напряжение, второй блок 8 интегрирования, аналоговый сумматор 9 и блок 10 выработки сигнала сброса при изменении входного кода.

Устройство работает следующим образом.

При изменении входного кода блок 10 выдает разрешение блоку 6 на проведение внеочередного сброса в блоке 3, а также на сброс в блоке 8. Возможная реализация блока 10 предусматривает наличие запоминающего регистра ll и цепи 12 сравнения кодов. Пель сравнения кодов осуществляет сравнение.текущего значения кода и его предшествующего значения, хранимого в регистре ll, при наличии разницы в данных кодах цепь 12 сравнения вырабатывает импульсный сигнал, по которому в регистр 11 переписывается новое значение входного кода и выдается сигнал блоку 6, разрешающий сброс в блоке интегрирования.

В результате последней операции на выходе блока 8 устанавливается уровень.

Далее, в соответствии с алгоритмом, производится перепись нового значения кода М в регистр 5 и преобразование данного кода блоком 7 в напряжение, при этом выходное напряжение сумматора 9 равно ивьиСО)=-91е с ) где — весовой коэффициент аналого4 вого сумматора по первому входу; опорное напряжение. 50

8 4 интегрируется блоком 8, и выходное напряжение которого равно " =, о" " 1 где < 1 — постоянная времени второго блока интегрирования, à Хо — фиксированный временной интервал, в течение которого в данном блоке интегрируется выходное напряжение первого блока интегрирования.

Это напряжение суммируется с выходным сигналом преобразователя 7.

Таким образом, повторение данного шпсла lyl раз обеспечивает на выходе сумматора 9 напряжение при динамической,погрешности блока 8, а следовательно и устройства в целом, не зависящей от "привязки" изменения входного кода к определенным моментам цикла. Последнее обстоятельство позволяет при заданной погрешности установления сократить количество требуемых итерационных циклов, Возможный вариант реализации блока 10 включает, например, запоминающий регистр 11 и цепь 12 совпадения кода, в данном блоке первый вход цепи 12 совпадения кодов и вход регистра 11 соединенны со входом блока 10, выход регистра 11 подключен ко второму входу цепи совпадения кодов, выход которой связан с выходом блока 10 и входом синхронизации регистра 11. Работа блока 10 заключается в том, что цепь 12 совпадения кодов осуществляет сравнение текущего значения кодов и его предшествующего значения, хранимого в регистре 11, при наличии разницы в данных кодах цепь совпадения 12 выдает на выход блока 10 импульсный сигнал, который также подается на вход синхронизации регистра 11, обеспечивая перепись в регистр нового значения входного кода, Таким образом, предлагаемое изобретение позволяет повысить быстродействие источника калиброванных напряжений.

Формула изобретения

Дальнейшая работа источника калиброванных напряжений аналогична итерационному процессу основного устройства: сперва блоком 3, на вход которого через коммутатор 2 разновременно поступают выходные напряжения блоков 1 и 3, определяется поправка, значение поправки

Источник калиброванных напряжений по авт. св. № 758095, о т л и чаюшийся тем, что, с целью увеличения быстродействия, в него введен блок выработки сигнала сброса при изменении входного кода, второй блок интегрирования дополнительно снабжен

5 9075 входом сброса, а блок управления оборудован дополнительными входом и выходом, причем вход и выход блока выработки сигнала сброса связаны соотг ветственно с входной клеммой источни18 6 ка калиброванных напряжений н допол иительным входом блока управления, а

% ьход сброса второго блока интегрирова сия подключен к дополнительному выходу блока управления.

ВНИИПИ Заказ 588/56 Тираж 908 Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4