Логарифмический усилитель

Иллюстрации

Показать всеРеферат

Союз Соввтскмк

С O4NOIINC TNT C KN X

Рвсвублпи

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1I)907559 (6! ) Донолннтелвнее к ввт. санд-ву (22) Заяалеие27.05.80 (2) ) 2970331/18-24 с присоединением заявки М (5! )М. Кл.

G06 g 7/24 (Ьеударатмеы5 щветат

tCCP ю делан иабрвтвиМ в еткрытвй (23) Приоритет

Онублвиевано 23.02.82. Бюллетень М .7

Дата опубликования описания 25.02.82 (53) УДК С81. .335(088.8) с

А. П. Шушкевич, А, Ф. Борода, Г. Н. Орлов g B. Ë. Фадеев

1 (72) Авторы изобретения (7I) Заявитель (54) ЛОГАРИФМИЧЕСКИМ УСИЛИТЕЛЬ

Изобретение относится к усилительным устройствам с логарифмической амнлитудной характеристикой и может быть испол эовано в аналоговых вычислительн ых м аш ни ах.

Известен логарифмический усилитель, соцержаший операционные усилители, лологарифмуюшие элементы и масштабные резисторы (11 .

Нецостатком. этого логарифмического усилителя является значительное искажение преобразуемого импульсного сигнала.

Наиболее близким по технической сушности к предлагаемому является логарифмический усилитель, содержащий т1 усилителей-ограничителей, И детекторов, вицеоусилителей, блок временной зацержки и сумматор (21 .

Нецостатком известного логарифмического усилителя является искажение формы преобразуемого сигнала, выражаюшееся в увеличении цлительности выходного виаеоимпульса при увеличении амплитуды входного сигнала.

llewü изобретения — уменьшение искажения формы преобразуемого сигнала, Эта цель достигается тем, что в известный логарифмический усилитель, содержащий соединенные последовательно т1 усилителей-ограничителей, вход первого иэ которых является вхоцом логарифмического усилителя, детекторов, sxort каждого иэ которых соецинен с выхоцом соответствующе го у си лителя-огр аничи те10 ля, выхоц каждого иэ И детекторов через соответствуюший видеоусилитель подключен к соответствуюшему входу блока временной эацержки, выходы которого соецинены со вхоцами сумматора, Вееае1$ ны элементы ИЛИ, формирователь импульса запрета, ключ и т) - 1 выцелителей заднего фронта импульса, причем выход кажцого из VI детекторов, кроме последнего, соединен с вхоцом соответствую20 шего из Н вЂ” 1 вьщелителей заднего фронта импульса, выход каждого иэ которых подключен к соответствуюшему входу элемента ИЛИ, выход которого через фор90755 мирователь импульса запре а соецинен с управляющим вхоцом ключа, вход которого подключен к выхоцу сумматора, выход ключа является выходом логарифмического у с или теля.

Причем выцелитель заднего фронта импульса содержит соединенные послецоватепьно дифференцируюшую цепь, ограничитель, эмиттерный повторитель, триггер Шмитта, вхоц цифференцируюшей цепи является входом вьщелителя заднего фронта импульса, а выхоцом которого является. выхоц триггера Шмитта.

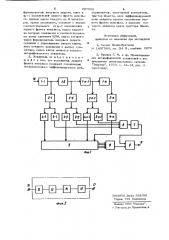

На фиг. 1 изображена функциональная схема логарифмического усилителя 15 на фиг. 2 — функциональная схема выделителя заднего фронта импульса, Логарифмический усилитель содержит усилитель-ограничитель 1-1, 1-2,..., 1- у, детектор 2-1, 2-2„... 2- Vt, вы- 20 делитель 3-1,3-2„., 3-(P-1) заднего фронта импульса, видеоусилитель 4-1, 4-3,..., 4-И, блок 5 временной зацер.жки, элемент ИЛИ б,формирователь 7 импульса запрета, ключ B,ñóììàòîð 9, вход 1 0 и выход 11 логарифмического усилителя, цифференцируюшая цепь 12, ограничитель

13, эмиттерный повторитель 14, триггер Шмитта 15, вхоц 16 и вьгход 17 выцелителя заднего фронта импульса. 30

Логарифмический усилитель работает следующим образом.

На вхоц 10 поступает сигнал с амплитуцой, соответствующей рабочему участку, например, первого усилителя- 35 ограничителя 1-1. При этом остальные усилители-ограничители 1-2, 1-й работают за прецелами линейного участка амплитудной характеристики, т.е. в режиме ограничения перегрузки, и выходные 40 вицеоимпульсы с каждого из них расши- рены по отношению к длительности сигнала на входе 10. Сильнее перегружен последний усилитель-ограничитель l-d, который раньше всех входит в режим д5 насыщения, так как цля него коэффициент усиления тракта максимальный следовательно, наибольшее искажение формы сигнала в нем — больше всего расширен выхоцной импульс. 56

Усиленные импульсы поступают на цетекторы 2-1, 2-2,..., 2-И, затем на видеоусилители, служащие цля согласования с блоком 5 временной задержки.

В блоке 5 временной зацержки компенсируются зацержки передних фронтов импульсов с усилителей-ограничителей

1-1, 1 2„... 1-Vl. С выходов блока 5

9 4 временной зацержки импульсы поступают на сумматор 9 и затем на вход нормально замкнутого ключа 8.

Оцновр менно с детекторов 2-1, 2-2, .

2-И расширенные импульсы поступают через вьшелители 3-1, 3-2,..., 3-(И-1) зацнего фронта импульса на входы элемента ИЛИ 6 и через него íà вход формирователя 7 импульса запрета. Формирователь 7 импульса запрета вырабатывает прямоугольный импульс с цлительностью, равной разности межцу цлительностями расширенного выходного импульса и входного импульса.

Запуск формирователя 7 импульса запрета производится каждым выделенным задним фронтом импульса. Поскольку все усилители-ограничители 1-1, 1-2,..., 1-И ицентичны и уровни в ограничение одинаковы, ro уровень запуска формирователя

7 импульса запрета выбирается равным началу отсчета выходного напряжения с ка;кдого из них.

С выхода формирователя 7 импульса запрета импульс с длительностью, равной величине приращения за счет расширения (искажения формы) поступает на управляющий вход ключа 8, запрещая. прохождение на вход 11 приращение расширенного имп уль с а.

В результате на выходе 11 во всем циапазоне входных сигналов длительность импульса равна цлительности импульса на вхоце 10.

Таким образом, прецлагаемый логарифмический усилитель по сравнению с иэ вестным характеризуется более точным воспроизвецением формы преобразуемого сигнала.

Формула изобретения

1, Логарифмический усилитель, содержащий соединенные послецовательно

И усилителей-ограничителей, вход первого из которых является вхоцом логарифмического усилителя, р цетекторов, вхоц кажцого из которых соединен с выхоцом со от ветс твующ е го уси ли те ля -огр аничи теля, выход кажцого из I1 детекторов через соответствующий вицеоусилитель подключен к соответствующему входу блоке временной задержки, выхоцы которого соединены со вхоцами сумматора, о т л и— ч а ю шийся тем„что, с целью уменьшения искажения формы преобразуемого сигнала, в него введены элемент ИЛИ, 5 9075 формирователь импульса запрета, ключ и -1 выцелителей зацнего фронта импульса, причем выхоц кажцого из И цетекторов, кроме послецнего, соецинен с вхоцом соответствующего из у -1 выаелителей заднего фронта импульса, выхоц кажцого из которых поцключен к соответствующему вхоцу элемента ИЛИ, выхоц которого через формирователь импульса запрета соецинен с управляющим вхоцом ключа, вхоц которого поцключен к выхоцу сумматора, выхоц ключа является выхоцом логарифмического усилителя.

2. Усилитель по п.1,о т л и ч а ю— шийся тем, что выцелитель зацнего фронта импульса соцержит соециненные послецовательн о цифференпирующую цепь, 59 6 ограничитель, эмиттерный повторитель, триггер Шмитта, вхоц цифференцируюшей цепи является вхоцом выцелителя зацнего фронта импульса, а выхоцом которого является выхоц триггера Шмитт а.

Истбчники .информации, принятые во внимание при экспертизе

1. Патент Великобритании

М 1437565, кл. G4 G, опублик. 1976

2, Крылов Г, М. и цр Проектирование логарифмических усилителей с не« прерывным цетектированием сигнала.

"Энергия, 1970, с. 12-14, рис. 3 (прототип) .

ВНИИПИ Заказ 592/58

Тираж 732 Поцписное

Филиал ППП Патент г. Ужгороц, ул. Проектная,4