Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

(72) Авторы изобретении

Д.А.Тодуа, Т.А.Клциашвили, М.А.Абрамян, АА,K.Йманов, О.Е .. у; свская и Н.A.Øåìÿãèí

Тбилисский научно-исследовательский институт приборостроения и средств автоматизации Научно-,:- производственного объединения ЭЛВА (73) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

IS

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Известно ассоциативное запоминающее устройство (.АЗУ), содержащее две матрицы запоминающих элементов, предназначенных для хранения одних и тех же данных. При сравнении информации, считываемой из обеих матриц, обнаруживается ошибка $1 ).

Недостатком этого устройства является низкая надежность работы вследствие того, что контроль ведется лишь при считывании. Кроме того, устройство имеет избыточное оборудование, так как содержит два одинаковых накопителя.

Наиболее близким по технической сущности,к изобретению является

АЗУ, содержащее матрицу элементов ассоциативной памяти, каждый из которЬ|х содержит запоминающую ячейку, блок считывания и блок сравнения, две группы блоков выдачи, шины выбора строки, информационные шины, шины выдачи данных и шины выдачи результатов поиска (2).

Однако известное устройство имеет низкую надежность ввиду отсутствия контроля работы в режимах записи .и считывания..

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в ассоциативное запоминающее устройство, содержащее накопитель, адресные входы которого являются адресными входами устройства, первую группу блоков считывания, входы которых подключены к выходам первой группы накопителя, а выходы блоков считывания первой группы являются одними выходами устройства, вторую группу блоков считывания, входы которых подключены к выходам второй группы накопителя, а выходы блоков считывания второй группы являются другими выходами устройства, 3 907 дополнительно введены элементы ИЛИ, первые входы которых подключены к выходам блоков считывания второй группы, вторые входы элементов ИЛИ подключены к адресным входам накопителя и элемент И, входы которого подключены к выходам элементов ИЛИ, а выход элемента И является управляющим выходом устройства.

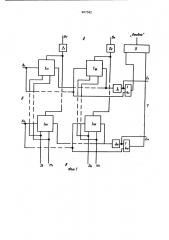

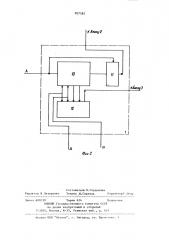

На фиг. 1 приведена структурная схема АЗУ; на фиг, 2 — схема запоминающей ячейки, АЗУ содержит накопитель запоминающих ячеек 14,1-! К, первую группу . блоков считывания 2 -2 у по числу столбцов матрицы, вторую группу блоков считывания 3! -3 1, по числу строк матрицы, элементы ИЛИ 4! -4и, элемент И 5, адресные входы 6, информационные выходы 7 и 8 и информационные входы 9. Запоминающая ячейка

1 содержит запоминающий элемент 10, выходной блок 11 и блок 1 2 сравнения.

Устройство работает следующим образом.

В режиме записи выбирается одна или несколько шин выбора строки, т.е. на шине присутствует уровень логического О", информация записывается в запоминающий элемент запоминающей ячейки 1 и одновременно производится сравнение записанной информации с входной информацией в блоке 12 сравнения, и в случае их совпадения с выхода блока считывания

3 выбранной строки снимается уровень логической "1", в это время невыбранные строки имеют на шинах выбора уровень логической "1" и про.верке не подвергаются, т.е. на выхо— дах соответствующих элементов ИЛИ 4 также присутствует уровень логической 1 . Присутствие на всех входах элемента И 5 уровней логической "1" не вызывает появления на его выходе сигнала "Ошибка". В случае неправильной записи или неправильной работы блока сравнения элементов памяти с выхода соответствующего элемента ИЛИ 4 снимается уровень логического 0, который вызывает появление с иг нала "Ошибка" .

В режиме чтения информационные шины блокируются и блоки 12 сравне582 ф ния при правильном функционировании имеют на входе уровень логической

"1"„ которые подаются через группу элементов ИЛИ 4 -4И на элемент И 5.

%

Присутствие на всех входах элемента И 5 уровней логической "1" не вызывает появления сигнала "Ошибка".

В противном случае> наличие хотя бы на одном входе элемента И 5 уровня логического О" вызывает появление сигнала "Ошибка".

Предлагаемое АЗУ обеспечивает самоконтроль в режимах записи и чтения, его применение позволит по высить надежность устройств памяти за счет контроля в рабочем режиме.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее накопитель, ад— ресные входы которого являк."ся адресными входами устройства, первую группу блоков считывания, входы которых подключены к выходам первой группы накопителя, а выходы блоков считывания первой группы являются одними выходами устройст . вторую группу блоков считывания, входы которых подключены к выходам второй группы накопителя, а выходы блоков считывания второй группы являются другими выходами устройства, о т— личающееся тем,что,сце35 лью повышения надежности устройства, оно содержит элементы ИЛИ, первые входы которых подключены к выходам блоков считывания второй группы, вторые входы элементов ИЛИ подклю40 чены к адресным входам накопителя, и элемент И., входы которого подключены к выходам элементов ИЛИ, а выход элемента И является управляющим выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Заявка Великобритании !! 1265645, кл. 5 Il С 15/00, 1974.

2. Биполярное ассоциативное запоминающее устройство. — "Электронная промышленность", 1975, Ф 11 (прототип1.

901582

Составитель В,Гордонова

Техред М.Гергель, Корректор Г.Огар

Редактор В.Лазаренко

Заказ ЬОО/59 Тираж 624 Подписное

ЯНИ1П1И Государственного комитета СССР о делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная . 4