Преобразователь постоянного напряжения в переменное

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву № 813629 (22) Заявлено 09.04:80 (21) 2906535/24-07 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 23.02.82. Бюллетень № 7

Дата опубликования описания 05.03.82 (51) M. Кл э

Н 02 М 7/48

Гасударственный камнтет

СССР (53) УДК 621.314..572 (088.8) по делам нзобретекий и еткрытий (72) Авторы изобретеиия

В. И. Сенько, В. С. Смирнов, Ю. К. Торопчинов и В. А. Скаржепа

Киевский ордена Ленина политехнический институт им. 50-летия (71) Заявитель

Изобретение относится к электротехнике, в частности к преобразовательной технике, и может быть использовано в преобразовательных установках с квазисинуносоидальным выходным напряжением для стабилизированного прецизионного электропривода.

По основному авт. св. № 813629 известно устройство содержащее последовательно соединенные суммирующий и инверторный блоки с управляемыми ключевыми элементами, блок управления, последовательно соединенные измерительный выпрямитель, входом подключенный к выходу инверторного блока, и аналого-цифровой блок, цифровой блок, цифровой коммутатор, один из входов которого соединен с выходом аналого-цифрового блока, а другой — с выходом блока управления, логические схемы совпадения, одни из входов которых соединены с выходами цифрового компаратора, а другие их входы подключены к выходу генератора импульсов, а также реверсивный счетчик, входами соединенный с выходами логических схем совпадения, а выходами связанный с управляющими входами соответствующих ключевых элементов суммирующего блока причем суммирующий блок выполнен в виде последовательно соединенных по выходу силовых ячеек каждая из которых представляет собой замкнутую цепь из последовательно включенных источника напряжения и двух ключевых элементов.

Недостатками устройства являются недостаточно высокое качество выходного напряжения, что иногда недопустимо в устройствах прецизионного электропривода, а также ограниченная точность стабилизации, о обусловленная определенным числом разрядности системы, т. е. в конечном счете числом уровней выходного напряжения (шагов квантования) . Причиной невысокого качества выходного напряжения преобразователя является положенная в основу работы сумми рующего блока двоичная система счисления, позволяющая получить только 2 m уровней выходного напряжения (m — число ячеек суммирующего блока).

Цель изобретения — повышение качества выходного напряжения за счет уменьшения его коэффициента нелинейных искажений при повышенной точности стабилизации.

Поставленная цель достигается тем, что в устройство введен дешифратор, входами соединенный с выходами реверсивного счет907734 чика, а выходами связанный с управляющими входами соответствующих ключевых элементов суммирующего блока, причем в каждую из ячеек суммирующего блока дополнительно введены последовательно соединенные источник напряжения и ключевой элемент, которые подключены параллельно одному из ключевых элементов ячейки, при этом силовые электроды другого ключевого элемента являются выходами ячейки.

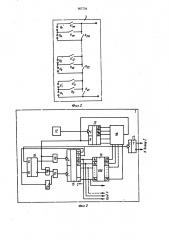

На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 — суммирующий блок; на фиг. 3 — блок управления; на фиг. 4 — схема сравнения кодов разрядностью М поразрядным сравнением; на фиг. 5 — дешифратор преобразующий четырехзарядный двоичный код в троичный.

Преобразователь (фиг. 1) содержит блок

1 управления, один из выходов которого связан с управляющими входами инвертора 2, силовой суммирующий блок 3, выход которого соединен с силовым входом инвертора, последовательно соединенные измерительный выпрямитель 4 и аналого-цифровой блок (АЦБ) 5, причем вход выпрямителя подключен к выходу инвертора, цифровой компаратор 6, одним из входов подключенный к выходу АЦБ, а другим — к цифровому выходу блока управления, логические схемы 7 и 8 совпадения, одни из входов которых соединены с выходами цифрового компаратора, а другие входы подключены к выходу генератора 9 импульсов, реверсивный счетчик 10, входами соединенный с выходами схем совпадения, а также дешифратор 11, входами соединенный с выходами реверсивного счетчика 10, а выходами связанный с управляющими входами суммирующего блока 3. Вы ход инвертора 2 является выходом преобразователя.

Блок 1 управления (фиг. 3) включает в себя задающий генератор 12, счетчик длительности ступеней 13, постоянное запоминающее устройство (ПЗУ) 14, реверсивный счетчик 15 управления, триггер 16 управления реверсивным счетчиком триггер 17 управления работой инвертора, схему 18 сравнения кодов, а также схемы И 19 и 20, ИЛИ 21 и НЕ 22 необходимые для функционирования блока управления. ПЗУ 14 содержит числа, записанные в двоичном коде, которые соответствуют длительности. Дешифратор 11 (фиг. 5) содержит декодер 23 и линейный дешифратор на схемах 24 — 27 совпадения.

Суммирующий блок 3 (фиг. 2) выполнен в виде последовательно соединенных по выходу силовых ячеек каждая из которых содержит две последовательно соединенных источника напряжения Uz u U причем

U —— U к точке соединения и выходным зажимом которых подключены ключевые элементы К1„,, К,„„и К2», . Другие силовые электроды ключевых элементов соединены в общую точку, а силовые электроды ключе4О

Блок 1 управления (фиг. 3) осуществляет формирование сигналов управления работой силовых ключей суммирующего блока 3 и инвертора 2 в виде двоичного параллель4s ного многоразрядного кода.

Когда в счетчиках 13 и 15 записаны нулевые коды, а триггер 16 находится в состоянии «1». При этом на выходе ПВУ 14 устанавливается код, выбираемый по адресу «О» и соответствующий длительности нуS0 левои ступени. С выхода генератора на счетный вход счетчика 13 непрерывно поступают импульсы опорной частоты. При наборе в счетнике 13 кода, соответствующей длительности первой ступени, сигнал с выхода

ss схемы 18 сравнения кодов через открытую схему 19 совпадения поступает на сумми.рующий вход реверсивного счетчика 15. При этом изменяется его состояние на «1». Кроs о

ss яо

25 вого элемента К,„являются выходами ячейки. При этом U> = U З ; Uz = Uo 3 ."Un

= U43, где Uo — шаг квантования.

Преобразователь работает следующим образом.

На цифровом выходе Х блока 1 управления формируется двоичный параллельный многоразрядный код, в любой момент времени соответствующий величине заданной аппроксимированной синусоиды. Квазисинусоидальное напряжение с выхода инвертора

2 после выпрямления в выпрямителе 4 поступает на вход АЦБ 5, где преобразуется в двоичный многоразрядный код У, соответствующий величине реального выходного напряжения. Управляющие коды Х и У поступают на входы цифрового компаратора 6, в котором постоянно происходит сравнение этих кодов и вырабатываются команды

«X)Y» и «Х(У». Эти команды в виде разрешающих сигналов поступают на один из входов схем 7 и 8 совпадения, в то время как на другие их входы поступают импульсы с выхода генератора 9. Таким образом, импульсы с выхода генератора 9 поступают на суммирующий либо на вычитающий входы реверсивного счетчика 10, на выходе которого формируется двоичный управляющий код, соответствующий увеличению или уменьшению выходного напряжения.

Далее управляющий код поступает на входы дешифратора 11, в котором в каждый момент времени осуществляется преобразование двоичного управляющего кода в троичный. Троичный управляющий код с выхода дешифратора 11 поступает на соответствующие управляющие входы суммирующего блока 3.

Суммирующий блок 3 позволяет преобразовать троичный управляющий код в аналоговое напряжение и при этом включает в себя минимальное число ключевых элементов, так как троичный код является оптимальным по числу реализующих элементов.

907734

Формула изобретения фиг.1

5 ме того, обнуляется счетчик 13. Изменение состояния счетчика 15 вызывает изменение информации на выходе ПЗУ 14, которая теперь соответствует длительности первой ступени, а также вызывает включение источника в сумматоре 3.

Счетчик 13 длительности ступеней повторно заполняется импульсами генератора

12 до того момента, пока не произойдет набор кода, соответствующего длительности первой ступени, поступающего с ПЗУ.

Аналогичным образом происходит формирование управляющего кода реверсивного счетчика 15 для всех последующих ступеней первой четверти периода за исключением верхней ступени.

В ПЗУ записывается число, соответствующее половине длительности верхней ступени.

При наборе этого кода в счетчике 13 импульс с схемы 18 сравнения переполняет реверсивный счетчик 15 (его состояние становится 000.0) . Импульс переполнения счетчика 15 с выхода + P опрокидывает триггер 16 и задним фронтом через сборку

21 вычитает единицу из счетчика. Таким образом, после формирования первой половины верхней ступени выход схемы сравнения оказывается подключенным к вычитающему входу счетчика 15, т.е. с выхода ПЗУ подается код, соответствующий длительности половины верхней ступени.

При наборе в счетчике 13 кода, соответствующего половине верхней ступени, импульс с выхода схемы 18 сравнения поступает на вычитающий вход счетчика 15, уменьшает его состояние на единицу и т. д.

При переходе счетчика 15 через «О» происходит опрокидывание триггеров 16 и

17 и аналогично формируется отрицательная полуволна выходного напряжения. Триггер 17 предназначен для управления работой ключей инвертора 2.

Использование новых блоков и связей обеспечивает более высокое качество выходного напряжения при одновременном повышении точности стабилизации. При наличии, например, 6 ячеек, т. е. 12 ключевых элементов, в составе суммирующего блока

1 известное устройство позволяет реализовать 64 уровня выходного напряжения, а предлагаемый преобразователь при наличии 4 ячеек, т. е. тоже 12 ключевых,элементов, позволяет формировать 31 уровень выходного напряжения. Кроме того, шаг квантования выходного напряжения в предлагаемом преобразователе существенно меньше, чем в известном, при равном числе ключевых элементов.

Таким образом, изобретение обеспечивает более высокое качество выходного напряжения, повышенную точность его стабилизации, более качественную стабильность гармонического состава выходного напряжения за счет повышенной точности стабилизации как в установившемся, так и в динамическом режимах работы.

Преобразователь постоянного напряжения в переменное по авт. св. № 813629, отличающийся тем, что, с целью повышения качества выходного напряжения путем уменьшения его коэффициента нелинейных искажений при повышенной точности стабилизации, в него введен дешифратор, вхоЗ0 дами соединенный с выходами реверсивного счетчика, а выходами связанный с управляющими входами соответствующих ключевых элементов суммирующего блока, при этом в каждую из ячеек суммирующего блока дополнительно введены последовательно

З5 соединенные источник напряжения и ключевой элемент, которые подключены параллельно одному из ключевых элементов ячейки, при этом силовые электроды другого ключевого элемента являются выходом ячейки.

90?734

В1

4-g

Ви

Фиг. 9

Фиг.5

Редактор Н. Джуган

Заказ 6!267

Составитель И. Никитин

Техред А. Бойкас Корректор У. Пономаренко

Тираж 719 Подписное

ВНИИПИ Государственного комитета СССР по ° делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4