Частотный манипулятор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ii)907857 (61) Дополнительное к авт. свид-ву— (22) Заявлено 07.04.80 (21) 2906789/18-09 с присоединением заявки №вЂ” (23) Приоритет—

Опубликована 23.02.82. Бюллетень № 7

Дата опубликования описания 28.02.82 (51) М. Кл.з

Н 04 L 27/12

Гоаударетеенный комитет (53) УДК 621.394..61 (088.8) дю делам изобретений и открытий с -! с

Г. Г. Болтач, В. М. Жижкин, В. К. Светлов и. В. К. Седвалд

j

Рижское производственное объединение ВЭФ им. В. И. Ленина (72) Авторы изобретения (71) Заявитель (54) ЧАСТОТНЫЙ МАНИПУЛЯТОР

Изобретение относится к радиотехнике и может использоваться в системах телеуправления и телесигнализации для осуществления частотной манипуляции, а также передачи дискретной информации по каналам тональной частоты частотным способом.

Известен частотный манипулятор, содержащий опорный генератор, выход которого подключен к тактовому входу адресного регистра, информационные входы которого соединены с выходами арифметического логического блока, а также последовательно соединенные цифро-аналоговый преобразователь и сглаживающий фильтр (1).

Однако известный частотный манипулятор имеет узкий частотный диапазон.

Цель изобретения — расширение частотного диапазона.

Для достижения этой цели в частотный манипулятор, содержащий опорный генератор, выход которого подключен к тактовому входу адресного регистра, информационные входы которого соединены с выходами арифметического логического блока, а также последовательно соединенные цифро-аналоговый преобразователь и сглаживающий фильтр, введены блоки памяти, инверторы, дешифраторы и регистр кода, выходы которого подключены к одним входам арифметического логического блока, дополнительный выход которого соединен со входом первого блока памяти, выход которого:подключен к соответствующему входу арифметического логического блока, другие входы которого соединены с выходами адресного регистра и информационными входами первого инвертора и дешифратора, первый выход которого подключен к управляющему входу первого инвертора, выходы которого через второй блок памяти соединены с информационными входами второго инвертора, к управляющему входу которого подключен второй выход дешифратора, тактовый вход которого соединен с выходом опорного генератора, причем выходы второго инвертора подключены ко входам цифро-аналогового преобразователя.

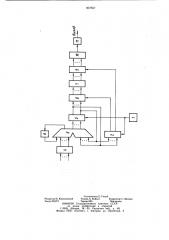

На чертеже представлена структурная электрическая схема предлагаемого манипулятора.

Частотный манипулятор содержит опорный генератор 1, дешифратор 2, адресный

907857

1е

Формула изобретения

2Е

3 регистр 3, регистр 4 кода, арифметический логический блок 5, первый 6 и второй 7 блоки памяти, первый 8 и второй 9 инверторы, цифро-аналоговый преобразователь 10, сглаживающий фильтр 11.

Частотный манипулятор работает следующим образом.

При подаче на.входы регистра 4 кода генерируемой частоты, происходит его запись в двоичном коде. В арифметическом логическом блоке 5 осуществляется сложение текущего адреса для второго блока 7 памяти, хранящего в адресном регистре 3 с кодом частоты, записанном в регистре 4 кода с последующей записью его в адресный регистр 3. Таким образом производится формирование текущей последовательности всех адресов синусоиды. Частота формирования адресов выбирается исходя из быстродействия выбранных элементов и верхней граничной генерируемой частоты манипуляции. Текущая последовательность адресов с выхода адресного регистра 3 через первый инвертор 8 подается на входы второго блока 7 памяти, где осуществляется последовательная выборка кодов синуса, которые через второй инвертор 9 поступают на входы цифро-аналогового преобразователя (ЦАП)

10. С выхода ЦАП 10 несглаженный синусоидальный сигнал поступает на вход сглаживающего фильтра 11, с выхода которого поступает сглаженный синусоидальный сигнал.

Адресный регистр 3 формирует текущую повторяющуюся последовательность адресов для одного квадранта синусоиды. Для формирования полной синусоиды, состоящей из четырех квадрантов, к выходу адресного регистра 3 подключен дешифратор 2, который через первый 8 и второй 9 инверторы обеспечивает формирование четырех квадрантов синусоиды.

Принцип формирования (обеспечение линейной зависимости) синусоидальных сигналов различных частот заключается в следующем.

Во втором блоке 7 памяти записаны коды синуса с числом координат аппроксимации m.

При генерировании самой низкой частоты манипуляции в регистр 4 кода записывается число, задающее частоту манипуляции п=1. При этом в адресном регистре 3 последовательно формируются адреса синусоиды всех m координат, которые поступают на входы второго блока 7 памяти. При более высокой частоте формируются адреса синусоиды, отстоящие друг от друга на, где

m — число координат аппроксимаций синузе зз ае

4з зе соиды, а и — число задающее частоту манипуляции, записанное в регистр 4 кода.

При этом выборка каждого кода синуса осуществляется через время М (шаг квантования). Шаг квантования при формировании любой из частот остается постоянным, что позволяет упростить сглаживающий фильтр

11, настроенный на одну частоту — частоту квантования.

Таким образом, положительный эффект от использования изобретения выражается в возможности работы в любой точке частотного диапазона за счет наличия линейной зависимости между подаваемым на вход кодом управления и генерируемой частотой на выходе, в возможности пользования постоянным шагом квантования во всем диапазоне генерируемых частот, что обеспечивает постоянство нелинейных искажений и в упрощении частотного манипулятора в целом.

Частотный манипулятор, содержащий опорный генератор, выход которого подключен к тактовому входу адресного регистра, информационные входы которого соединены с выходами арифметического логического блока, а также последовательно соединенные цифро-аналоговый преобразователь и сглаживающий фильтр, отличающийся тем, что, с целью расширения частотного диапазона, введены блоки памяти, инверторы, дешифраторы и регистр кода, выходы которого подключены к одним входам арифметического логического блока, дополнительный выход которого соединен со входом первого блока памяти, выход которого подключен к соответствующему входу арифметического логического блока, другие входы которого соединены с выходами адресного регистра и информационными входами первого инвертора и дешифратора, первый выход которого подключен к управляющему входу первого инвертора, выходы которого через второй блок памяти соединены с информационными входами второго инвертора, к управляющему входу которого подключен второй выход дешифратора, тактовый вход которого соединен с выходом опорного генератора, причем выходы второго инвертора подключены ко входам цифра-аналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 472474, кл. Н 04 1. 27/12, 1972.

907857

Редактор И. Юрковецкий

Заказ 623/73

Составитель Е. Голуб

Техред А. Бойкас Корректор С. Щомак

Тираж 685 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4