Устройство для приема частотно-манипулированных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 17.04.80 (21) 2910937/18-09

Союз Советских

Социалис тических

Республик ()907859 (51) М.К.

Н 04 L 27/14 с присоединением заявки №вЂ”

Гасударственный кюмнтет (23) Приоритет— по делам нзебретенн»

» открытий (53) УДК 621.376..3 (088.8) Опубликовано 23.02.82. Бюллетень № 7

Дата опубликования описания 28.02.82 (72) Автор изобретения

А. Л. Сартаков

h (/ !

/ р м ( (71) Заявитель (54) УСТРОЛСТВО ДЛЯ ПРИЕМА ЧАСТОТНОМАНИПУЛИРОВАННЫХ СИГНАЛОВ

Изобретение относится к технике связи и может использоваться для приема сигналов с комбинированной частотно-фазовой манипуляцией.

Известно устройство для приема частотно-манипулированных сигналов, содержащее входной согласующий блок, выход которого подключен ко входам двух каналов, каждый из которых состоит из последовательно соединенных блока фазовой автоподстройки частоты, фазового детектора, сумматора, интегратора и блока памяти, выход каждого канала соединен с соответствующим входом элемента ИЛИ, причем вторые входы фазовых детекторов каналов соединены с выходом входного согласующего блока, а вторые входы сумматоров каналов соединены с выходами фазовых детекторов противоположных каналов, и блок выделения значащих моментов сигнала (11.

Однако известное устройство не обеспечивает надлежащей помехоустойчивости.

Цель изобретения — повышение помехоустойчивости.

Для достижения этой цели в устройство для приема частотно-манипулированных сигн алов, содержащее входной согласующий блок, выход которого подключен ко входам двух каналов, каждый из которых состоит из последовательно соединенных блока фазовой автоподстройки частоты, фазового детектора, сумматора, интегратора и блока памяти, выход каждого канала соединен с соответствующим входом элемента ИЛИ, причем вторые входы фазовых детекторов каналов соединены с выходом входного corto ласующего блока, а вторые входы сумматоров каналов соединены с выходами фазовых детекторов противоположных каналов, и блок выделения значащих моментов сигнала, введены дополнительный блок выделения значащих моментов сигнала, первый и второй дополнительные фазовые декторы, дополнительный сумматор, усредняющий блок и управляемые генератор, соответствующие выходы которого соединены с соответствующими входами интеграторов и бло20 ков памяти каналов и первыми входами первого и второго дополнительных фазовых детекторов, вторые входы которых соответственно через блок выделения значащих моментов сигнала и дополнительный блок вы90?859 деления значащих моментов сигнала соединены с выходами соответствующих сумматоров каналов, а выходы первого и второго дополнительных фазовых детекторов соединены с первым и вторым входами дополнительного сумматора, выход которого через усредняющий блок подключен ко входу управляемого генератора.

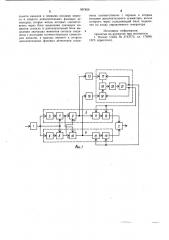

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит входной согласующий блок 1, элемент ИЛИ 2, два канала 3 и 4, каждый из которых содержит блок 5(6) фазовой автоподстройки частоты, фазовый детектор 7(8), сумматор 9(10), интегратотор !1(12) и блок 13(14) памяти, кроме того, устройство содержит блок 15 выделения значащих моментов сигнала, дополнительный блок 16 выделения значащих моментов сигнала, первый и второй дополнительные фазовые детекторы 17 и 18, дополнительный сумматор 19, усредняющий блок 20 и управляемый генератор 21.

Устройство работает следующим образом.

Входной сигнал, модулированный по фазе и частоте, через блок 1 поступает на блоки 5 и 6 фазовой автоподстройки частоты и фазовые детекторы 7 и 8. Исходный двоичный сигнал показан на фиг. 2а, а сигнал с частотно-фазовой манипуляцией — на фиг. 2 б. Сравнение фаз в блоке 5 осуществляется на удвоенной верхней характеристической частоте, а в блоке 6 — на удвоенной нижней характеристической частоте. Работа на удвоенных частотах устраняет влияние фазовой манипуляции сигнала. Опорные колебания характеристических частот (фиг. 2 в и г) поступают на соответствующие фазовые детекторы 7 и 8, где осуществляется фазовое детектирование принимаемого сигнала. Выходные напряжения фазовых детекторов 7 и 8 показаны на фиг. 2 д и е соответственно. На выходе сумматора 9 действует сумма выходных напряжений фазовых детекторов 7 и 8 (фиг. 2 ж), а на выходе сум матора 10 — их разность (фиг. 2 з) .

Блоки 15 и 16 выделения значащих моментов формируют короткие импульсы в момент перехода выходных напряжений сумматоров 9 и 10 через ноль (фиг. 2 и и к) соответственно. Максимальная частота следования значащих моментов в каждом канале равна половине тактовой частоты сигнала, а их взаимное смещение равно Ю.

Поэтому выходные сигналы блоков 15 и 16 поступают в блоке фазовой автоподстройки частоты на отдельные фазовые детекторы 17 и 18, на другие входы которых поступают выходные сигналы управляемого генератора 21 с частотой, равной половине тактовой частоты и сдвинутые по фазе íà и.

Формула изобретения

l$

$$

iе

$s

2S

З0 (фиг. 2 л и м). Суммирование выходных сигналов фазовых детекторов 17 и 18 в сумматоре 19 обеспечивает уменьшение времени синхронизации по тактам. После усреднения в усредняющем блоке 20 сигнал фазового рассогласования поступает на управляемый генератор 21, изменяя фазу его выходных сигналов в направлении уменьшения фазового рассогласования.

Выходные напряжения сумматоров 9 и 10 интегрируются в интеграторах 11 и 12.

По сигналам тактовой синхронизации, снимаемым с соответствующего выхода управляемого генератора 21, знак выходного напряжения интегратора 11 (12) запоминается в двоичном блоке 13(14) памяти. Затем осуществляется разряд интегратора 11(12).

Диаграммы выходных напряжений интеграторов 11 и 12 приведены на фиг. 2 н и о, а выходных напряжений двоичных блоков 13 и 14 памяти — на фиг. 2 и и р соответственно. Поступая на входы элемента ИЛИ 2, двоичные выходные сигналы блоков 13 и 14 формируют на его выходе двоичный сигнал в соответствии с данной логической операцией (фиг. 2 с). Этот сигнал является выходным сигналом устройства. Как видно из сравнения диаграммы фиг. 2 с и 2а, он совпадает с исходным двоичным сигналом, но задержан на два такта.

Техническая эффективность предлагаемого устройства заключаегся в возможности приема сигналов с произвольным индексом частотной модуляции и в повышении помехоустойчивости по отношени)о к приемникам частотно-манипулированных сигналов.

Устройство для приема частотно-манипулированных сигналов, содержащее входной согласующий блок, выход которого подключен ко входам двух каналов, каждый из которых состоит из последовательно,соединенных блока фазовой автоподстройки частоты, фазового детектора, сумматора, интегратора и блока памяти, выход каждого канала соединен с соответствующим входом элемента ИЛИ, причем вторые входы фазовых детекторов каналов соединены с выходом входного согласующего блока, а втбрые входы сумматоров каналов соединены с выходами фазовых детекторов противоположных каналов, и блок выделения значащих моментов сигнала, отличающееся тем, что, с целью повышения помехоустойчивости, введены дополнительный блок выделения значащих моментов сигнала, первый и второй дополнительные фазовые детекторы, дополнительный сумматор, усредняющий блок и управляемый генератор, соответствующие выходы которого соединены с соответствующими входами интеграторов и блоков

907859 памяти каналов и первыми входами первого и второго дополнительных фазовых детектрров, вторые входы которых соответственно через блок выделения значащих моментов сигнала и дополнительный блок выделения значащих моментов сигнала соединены с выходами соответствующих сумматоров каналов, а выходы первого и второго дополнительных фазовых детекторов соедииены соответственно с первым и вторым входами дополнительного сумматора, выход которого через усредняющий блок подключен ко входу управляемого генератора.

5 Источники информации, принятые во внимание при экспертизе

1. Патент США № 3743775, кл. 178/88, 1973 (прототип).

907859

Составитель Е. Смирнов

Редактор И. Юрковецкий Техред А. Бойкас Корректор Е. Рошко

Заказ 623 73 Тираж 685 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж — 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4