Система передачи и приема сигналов изображения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реснублик

<1 907869 (61) ???????????????????????????? ?? ??????. ????????-???? (?? ??. ??. (22) ???????????????? 21,1279 (21) 2856754>

H 04 N 7/12 с присоединением заявки ¹(23) Приоритет

ГосударственныЙ комитет

СССР по делам изобретений н открытий

Опубликовано 2302)32, Бюллетень № 7

Дата опубликования описания 23.02.82 (3 3) УДК 6 21, .0 97 (088.8) (72) Авторы изобретения

С.С.Коган и В.Н.Соколов (71) Заявитель (54) СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ

ИЗОБРАЖЕНИЯ

Изобретение относится к цифровым системам передачи информации.

Известна система передачи н приема сигналов иэображения, содержащая на передающей стороне N-разрядный аналого-цифровой преобразователь (где N =1, 2, 3...), соединенный через преобразователь кода с каналом связи, а на приемной стороне компараторы и преобразователь кода, подключенный входом к каналу связи, при этом к соответствующим выходам преобразователя кода подключено

N-входов цифро-аналогового преобразователя, при этом к каждому выходу преобразователя кода подключены пер- вый и второй входы сумматора по модулю два, причем первый вход непосредственно, а второй вход — .через блок задержки, а к выходу каждого сумматора по . модулю два подключен вход соответствующего интегратора (1) .

Однако такая система обладает невысокой надежностью синхронизации.

Бель изобретения — повышение надежности синхронизации.

Поставленная цель достигается тем, что в системе передачи и приема сигналов изображения, содержащей на передающей стороне N-разрядныи аналого-цифровой преобразователь (где N = 1, 2, 3...), соединенный через преобразователь кода с каналом связи, а на приемной стороне компараторы и преобразователь кода, подключенный входом к каналу связи, при этом к соответствующим выходам преобразователя кода подключено

N-входов цифро-аналогового преобразователя, при этом к каждому выходу преобразователя кода подключены первый и второй входы сумматора по модулю два„ причем первый вход непосредственно, а второй вход — через блок задержки, а к выходу каждого сумматора по модулю два подключен вход соответствующего интегратора, на приемной стороне введены дешифратор и блок управления, причем при N-четном к первому входу i-го (где i = 1, 2, 3,...N/2) компаратора подключен выход 1-го интегратора, а к второму входу 1-го кбмпаратора подключен выход (i + N/2) интегратора при И-нечетном, к пе)звому входу i-,го (где 1 = 1, 2, 3... — - ) компаратора подключен выход 1-Ъо интегратора, а к второму входу „1-ro компаратора

30 подключен внкод (— .."- )-гo ннтегва90786.9 ности элемента, строки или кадра для монохромного телевизионного сигнала и равным трем элементам изображения для сигналов цветного телевидения. (О Если система находится в состоянии синхронизма, то цифровые сигналы на

1-м выходе преобразователя 4 кода соответствуют сигналам на выходе

i-го разряда АЦП 1. В этом случае для напряжений на выходах интегратора 8, находящихся в цепях различных разрядов, выполняются неравенства, аналогичные неравенствам (1) для

N-четного и (2) для N-нечетного ° В соответствии с этими неравенствами между выходами интегратора 8 включены компараторы 9. При N-четном между выходами N-интеграторов включены компараторов. Входы каждоЯ

25 го -го компаратора 9 соединены соответственно с выходами 1-ro u (i + < )-ro интегратора 8 (li ig-).

При N-нечетном между ыхо ами N«1 интеграторов включены -я- компарато г ров. Входы каждого i-ro компаратора

9 соединены соответственно с выходами i-го и (" ) -го интегратора

N4

8 (1 <1< — ) °

Состояйте компараторов 9 преобразуются дешифратором 10 в (N = 1)

Ç5 сигналов, подаваемых на блок 11 управления. Таким образом, каждому состоянию компараторов 9 соответь ствует сигнал на одном из (N = 1) выходов дешифратора 10. (N = 1) зто число возможных комбинаций .положений разрядов на выходах преобразователя 4 кода при отсутствии синхронизации.

Тактирующий сигнал управления с

45 дополнительного выхода преобразователя 4 кода через блок 11 управления поступает на дополнительный вход преобразователя 4 кода. В блоке 11 управления тактирующий сигнал управ50 ления в соответствии с состоянием дешифратора 10 преобразуется таким образом, чтобы обеспечить установку преобразователя 4 кода в синхронизм после одного такта анализастатистическнх характеристик цифрового сигнала..

55 Пр, лагаемая система Обеспечивает уменьшение вероятности выхода сис. темы из синхрониэма, поскольку компараторы осуществляют сравнение статических характеристик разрядных последовательностей, разность номерОВ которых максимизирована, в связи с чем исключается влияние нарушения монотонной зависимости частоты переключения посылок в 1-й разрядной

65 последовательности от номера i этой тора, при этом выходы компараторов подключены к соответствующим входам дешифратора, выход которого соединен с входом блока управЛения, а выход блока управления подключен к входу синхронизации преобразователя кодов, выход синхронизации которого подключен к входу синхронизации блока управления.

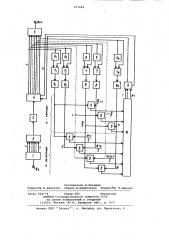

На чертеже представлена структурная электрическая схема системы передачи и приема сигналов изображения.

Система передачи и приема сигналов изображения содержит на передающей стороне аналого-цифровой преобразователь (АЦП) 1, преобразователь 2 кода, канал 3 связи, а на приемной стороне — поеобразовател

4 кода, цифро-аналоговый преобразователь (LIAII) 5, N элементов 6 задержки, N сумматоров 7 по модулю два, N интеграторов 8, компараторы 9, дешифратор 10 и блок 11 управления.

Устройство работает следующим образом.

На выход АЦП 1 подается аналоговый сигнал иэображения, à cего выхода снимается последовательность

N-разрядных двоичных кодовых групп, являющихся эквивалентом входного аналогового сигнала.

N-разрядные двоичные кодовые группы подаются затем на преобразователь 2 кода из параллельного в последовательный, сигнал с выхода которого поступает на вход канала

3 связи. C выхода канала 3 связи цифровой сигнал через преобразовател

4 кода из последовательного в параллельный поступает на входы цифро-аналогового преобразователя 5, с выхода которого снимается аналоговый сигнал изображения. Кодовые группы с выхода преобразователя 4 кода поступают также на .последовательно соединенные элементы 6 задержки, сумматоры 7 по модулю два, интеграторы 8, компараторы 9, которые анализируют статистические ха.рактеристики цифрового сигнала и проверяют выполнение неравенств ,() (и <)

1 (1) при N"÷åòíîì р Ср >1< 1 а — — (2) (() М 1 при N-нечетном, где р " вероятность изменения посылок.

Сигнал с каждого (i-го) выхода преобразователя .4 кода поступает на соответствующий сумматор 7 по модулю два непосредственно и через элемент 6 задержки. С выхода сумматора 7 по мо)акулю два сигнал поступает на интегратор 8. В зависимости от выбранной величины задержки в элементе 6 задержки напряжение на выходе интегратора 8 будет пропорционально вероятности изменения посылки 0 -ь 1 или 1 †0 в цифровом сигнале на данном (i-M) выходе пре" образователя 4 кода в позициях, разделенных интервалом, равным длитель907869

Формула изобретения

Система передачи и приема сиг-. налов изображения, содержащая на передающей стороне N-разрядный аналого-цифровой преобразователь (где N=l, 2, 3. ° .), соединенный через преобразователь кода с каналом связи, а на приемной стороне— компараторы и преобразователь кода, подключенный входом к каналу связи, при этом к соответствующим выходам преобразователя кода подключено Nвходов цифро-аналогового преобразователя, при этом к каждому выходу преобразователя кода подключены первый и второй входы сумматора по модулю два, причем первый вход непосредственно, а второй вход — через блок задержки, а к выходу каж!

5 последовательности, а также ооесне чивает уменьшение времени вхождения в синхронизм, а именно вхождение в синхронизм приемной части оборудования происходит за один такт анализа статистических характеристик 5 цифрового сигнала. дого сумматора по модулю два подклю чен вход соответствующ зro интегратора, о т л и ч а ю щ à s с я тем, что, с целью повышения надежности синхронизации, на приемной стороне введены дешифратор и блок управления, причем при Ы-четном к первому входу 1-ro (где 1 = 1, 2, 3...И/2) компаратора подключен выход i-го интегратора, а к второму входу 1-го компаратора подключен выход (1+N/2) интегратора при N-нечетном, к перному входу i-го (где i=li2,3... ) компаратора подключен выход 1-r > интегратора, а к второму входу i-го компаратора подключен выход (" )

-го интегратора, при этом выходы компараторявподключены к соответст" вующим входам дешифратора, выход которого соединен с входом блока управления, а выход блока управления подключен к входу синхронизации преобразователя кодов, выход синхронизации которого подключен к входу синхронизации блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 720776, кл. Н 04 L 25/40, 1978.

907869

Составитель В.Лякишев

Редактор. Н.Данкулич Техред Е.Харитончик Корректор М.Шароши, Заказ 624/74 Тираж 685 Подписное

ВНИИПИ Росударственного комитета СССР по делам изобретениЯ и открытиЯ

113035, Москва, Ж-35, Раушская наб., д. 4/5 .4

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4