Система для контроля электрических параметров цифровых узлов

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Ю. С. Рябус, В.Г. Калашников, Ю.A. Безбородько и В.М. Верченко (7I ) Заявитель (54) СИСТЕМА ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ

ЦИФРОВЫХ УЗЛОВ

По основному авт. св. % 660061 известна система, соцержащая группу бло.-: ков согласования по числу контролируемых параметров, блок измерений, входы

10 которого подключены к первым выходам соответствующих блоков согласования, первые входы которых соединены с вы ходом блока программируемых источни15 ков питания, блок управления, соединенный первыми входом и выходом соответственно с выходом и входом блока сопряжения, а вторым и третьим выходами — с управляющими входами соответ ственно блока программируемых источников пйтания и блока измерителей, информационный выход которого подключен к второму входу блока управления, Изобретение относится к вычислитель ной и контрольно-измерительной технике и может быть использовано при разработке автоматизированных систем конт роля цифровых узлов различной радиоS электронной аппаратуры. управляющую вычислительную машину и устройства ввода вывода, соединенные двухсторонними связями с блоком сопряжения, второй и третий входы каждого блока согласования соединены соответ ственно с четвертым выходом блока управления и выходом блока сопряжения, вторые выходы и четвертые входы блоков согласования соединены с соответствующими выходами и входами системы, lips» чем каждый блок согласования содержит регистр уставок; подключенный первым и BTopblM выходами соответственно K первым входам коммутатора и компаратора, второй вход которого подключен к первому выходу коммутатора, второй и третий входы которого соединены соответственно с первым и четвертым вхрдами блока согласования, а второй выход с вторым выходом блока согласования, первый вход регистра уставок является первым входом блока согласования, второй вход которого подключен к второму входу- регистра уставок и третыему входу компаратора, выхоц которого является первым выходом блока согласования, в каждый блок согласования ввецены цифроаналоговый преобразователь, группа элементов И и узел формирования эквивалентов нагрузки, причем третий вы.хоц и второй ."вход регистра уставок, соединены с соответствующими входами группы элементов И, соециненной выхоцом с вхоцом цифроаналогового преобразователя,выход которого подключен к четвертым вхоцам компаратора и коммутатора, пятый вхоц которого соецинен через угол формирования эквивалентов ,Нагрузки с четвертым выхоцом регистра, уставок 1).

Данная система позволяет обеспечить независимую установку уровней параметров в кажцом блоке согласования. Но так как в процессе работы системы уста- N ковка уровней по каждому параметру осуществляется последовательно, она обладает низким быстродействием (практически единицы кГц).

Цель изобретения - повышение быст 2S роцейстпия системы.

Поставленная цель цостигается тем, что в кажцый блок согласования ввецен блок памяти, соединенный входом с вы- З0 хоцом группы элементов И, а вйхоцомсо вхоцом цифроаналогового преобразователя.

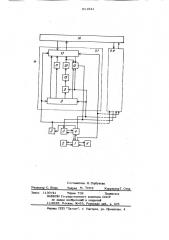

На чертеже представлена блок-схема предлагаемой системы. 35

Система соцержит. блок 1 сопряжения, управляющую вычислительную машину (УВМ) 2, блок 3 программируемых источников питания, блок 4 управления, блок 5 измерителей, устройство 6 ввоца-40 вывоца, блоки 7.1-7Я согпасования, включающие регистр 8 уставок, группу элементов И 9, цифроаналоговый преобразователь (ЦАП) 10, узел 1 1 формирования эквивалентов нагрузки, компаратор 1 2, коммутатор 1 3, объект 14 контропя, блок

1 5 памяти.

Система работает следующим образом.

По команце оператора осуществляется автоматический поиск программы провер- 50 ки объекта 14 контроля, поцключенного .к системе. Программа проверки выбран» ного объекта контроля, хранящаяся на внешнем носителе, вводится в УВМ 2 через устройство 6 ввода-вывоца и блок 1сопряжения, УВМ 2 в соответствии с введенной в нее программой контроля осуществляет программирование блоков 7.178 согласования, блока 5 измерите91 1541 4 лей и блока 3 рогрмируеьь1х источни ков питания. Программирование блоков согласования осуществляется слецующим образом. УВМ 2 через блок 1 сопряже- . ния и блок 4 управления по информационной магистрали выцает коды управления, которые фиксируются в регистре 8 установок, опрецеляя состояние блоков согласования, а именно коммутатора 13, ком паратора 12, узла 11 формирования эквивалента нагрузок и цифроаналогового преобразователя от управляющих сигналов, поступающих с регистра 8 уставок, коммутатор 13 подключает к объекту 14 контроля либо узел формирования эквивалента нагрузок и сигнальный вхоц ком» паратора 12, либо выхоц цифроаналогового преобразователя 1 О. Соответственно данный блок согласования в дальнейшем (цо перепрограммирования) осуществляется либо контроль сигнала, либо его генерирование, После этого УВМ 2 через блок 1 сопряжения блок 4 управления и через группы элементов И 9 соответствующих блоков 7.1-7, И согласования выбираемых из множества для данной проверки осуществляет послецовательную запись информации, соответствующей испытательной программе контроля, в блоке памяти всех выбранных блоков согласования, блок памяти прецставляет собой, например, ОЗУ с произвольной выборкой.

Программирование блока измерителей происхоцит слецующим образом. УВМ 2 выцает команды управления, которые через блок 1 сопряжения и блок 4 управ ления поступают в блок 5 измерителей, вхоцы которого в соответствии с команцами управления поцключается к выхоцам компараторов 12, выбранных программой из множества блоков 7.1-7йсогла-. сования. Программирование и поцключение .источников питания блоком 3 к соответствующим контактам объекта 14 контродя происхоцит в послецнюю очередь и в слеауюшем порядке. УВМ 2 выцает команды управления, которые через блок

1 сопряжения и блок 4 управления поступают на информационный вхоц блока 3,. гце в соответствии с этими команцами осуществляется поцключение вторых входов коммутаторов 1 3 соответствующих блоков 7.1-7 М,согласования к шинам питания блоков 3, потенциал на которых также программируется,по команцам от

УВМ 2. После этого в регистрь1 8 уставок выбранных блоков согласования заносится информация, которая формирует на первых выходах регистра 8 уставок

9115 потенциалы, которые поступают на первые входы коммутаторов 1 3 и разрешают подачу питания на входы объекта 14 конт роля.

Проверка объекта 14 контроля осу- 5 шествляется путем циклического формирования стимулирующих воздействий и оценки его реакций. В течение каждого цикла контроля УВМ 2 через блок 1 сопряжения и блок 4 управления и группы эле-1О ментов И 9 подает параллельно на все блоки 15, выбранных блоков согласования, управляющие команды, в результате которых код, записанный в определенном поле блока 15 памяти, поступает на цифроаналоговые преобразователи 10, которые преобразуют коды в аналоговые уровни. Эти уровни через коммутатор 13 поступают на объект 14 контроля. В ранее запрограммированных блоках 7 осуществляется контроль реакций. Уровень с цифроаналогового преобразователя

10 сравнивается посредством компараторов 12 с сигналом реакции, поступающим через коммутатор 1 3 с объекта 1 4 кон1 >> роля. Результат сравнения поступает с выхода компаратора 12 на вход блока.

5 измерителей и далее через 6цок 4 управления и блок 1 сопряжения в УВМ 2, где он анализируется и по мере надоб- ЗО ности выдается через блок 1 сопряжения. и устройство 6 ввода-вывода на ре гистрацию.

41 . 6

Аналогично .осуществляются последую шие циклы контроля, число которых ограничивается объемом блока 15 памяти.

Результаты контроля обрабатываются

УВМ 2 и поступают через блоки 1 сопряжения на блок 3.

За счет введения в каждый блок согласования собственного запоминающего устройства в данНой системе осуществляется параллельное формирование векторов контроля эталонных сигналов для компаратора. В результате чего частота выдачи, сигналов на объект контроля и аналйза сигналов с объекта кон фоля с прототипом повышается в Й раз, где Ячисло каналов согласования.

Формула изобретения

Система для контроля электрических параметров цифровых узлов по авт св.

¹ 660061, о т л и ч а ю ш а я с я тем, что, с целью повышения: быстродействия системы, в каждый блок согла» сования введен блок памяти, соединенный входом с выходом группы элементов И, а выходом - со входом цифроаналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

1 . Авторское свидетельство СССР

34 660061, кл. Q 06 F 15/46 1976 (прототип) .

91 1541

Составитель Н. Горбунова

Тех ед > Тенер Ко екто Г. Orap

Редакто С. Юско

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4

Заказ 1 130/41 Ч ираж 732 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

11303S, Москва, Ж-ЗВ, Раушская наб., д. 4/5