Устройство для извлечения корня заданного порядка

Иллюстрации

Показать всеРеферат

ОП КСАН И Е

ИЗОВГЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<>0 911554

Союз Советских

Социалистических

Респубпик (61) Дополнительное к авт.свкд-ву (22) Заявлено 04.08.80 (21) 296717 1/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 07.03.82. Бюллетень .рв 9

Дата опубликования описания 07.03.82 (51)N. Кл.

С 06 5 7/20

9куяарстокииый коиитрт

СССР во делам иаобретеиий и открытий (53) УДК 681 335 (088.8) (72) Автори изобретения

А. М. Бпагородов, А. Б. Прохорова и М. В. Ша (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ ЗАДАННОГО ПОРЯДКА

Изобретение относится к автоматике и вычислительной технике н может найти применение в аналоговых вычиспитепьных машинах.

Известно устройство дпя извлечения корня, содержашее управпяемые интеграS торы, кнючи, фильтр, одновибратор, блок формирования импульсов и блоки обнупения интеграторов 11.

Недостатком указанного устройства о является бопьшая инерционность, обусповленная наличием фильтра, выходной сит пап которого является выходным сигналом всего устройства.

Наиболее близким к предлагаемому явtS ляется устройство дпя извпечения корня заданного порядка, содержашее последовательно соединенные источник этапонного напряжения и ячеек, каждая из которых содержит поспедоватепьно соединен ные основной ключ и интегратор, ко входу основного ключа подключен вход инвер- ., тора, выход которого через допопнитепьный ключ подключен к входу интегратора, выход интегратора каждой ячейки соединен со входом инвертора поспедуюшей ячейки, выход интегратора последней ячейки подключен к одному из вкоаов компаратора, другой вход которого соединен с входом всего устройства, а выход компаратора подкпючен к управпяюшим входам основного и допопнитепьного ключей всех ячеек f23.

Недостатком известного устройства является накопление погрешностей в процессе работы, вызванное задержкой срабатывания кпючей и компаратора.

Бель изобретения - повышение точности работы устройства.

Поставленная цепь достигается тем, что в устройство дпя извпечения корня заданного порядка, содержашее источник эталонного напряжения и tl ячеек, каж дая из которых содержит поспедоватепьно соединенные инвертор и первый кпюч, выход которого соединен с входом интег ратора и выходом второго ключа, вход которого соединен с входом инвертора, 3 9115 выход интегратора каждой ячейки соединен с входом инвертора последуюшей ячейки, вход инвертора первой ячейки соединен с выходом источника эталонного напряжения, выход интегратора первой ячей- 5 ки является выходом устройства, а выход интегратора и -й ячейки соединен с первым входом компаратора, введены блок выборки-хранения, первый и второй элементы И, формирователь импульсов и триггер, причем первый вход блока выборки-хранения является информационным входом устройства, второй вход соединен с выходом триггера и первыми входами первого и второго элементов И, вторые вхо-15 ды которых соединены с выходом компаратора и через формирователь импульсов с вторым входом триггера, первый вход которого является управляющим входом устройства, выход блока выборки-хранения соединен с вторым входом компаратора, а выходы первого и второго элементов И соединены соответственно с управпяюшими входами второго и первого клк чей каждой ячейки.

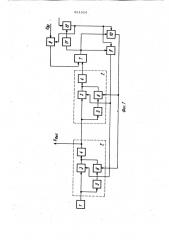

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы работы устройства.

Устройство содержит источник 1 эта30 лонного напряжения, ячейки 2-1, ..., 2-п, второй ключ 3, интегратор 4, инвертор

5, первый ключ 6, компаратор 7, блок

8 выборки-хранения, первый элемент И 9, второй элемент И 10, формирователь 11 импульсов, триггер 12.

Устройство работает следуюшим образом.

B исходном состоянии выходные напряжения интеграторов 4 всех ячеек 2-1, ..., 2-п равны нулю. Вне зависимости

40 от сигнала на входе блока 8 выборки-хранения второй кшоч 3 и первый ключ 6 всех ячеек закрыты, так как выходной сигнал триггера 12 равен нулю, а следовательно, выходные сигналы первого

45 элемента И 9 и второго элемента И 10 также равны нулю. При этом блок 8 выборки-хранения повторяет на своем выходе сигнал, поступаюший на его вход (фиг. 2б).

В момент <, прихода сигнала запроса (фиг. 2в) на вход триггера 12 он переходит в состояние "1" (фиг. 2ж), При этом блок 8 выборки-хранения переходит в состояние Хранение", т.е. сигнал на его выходе остается равными,„(,) вне зависимости от дальнейшего изменения входного сигнала (фиг, 2б). Включа54 4 ются вторые ключи 3 всех ячеек, и происходит интегрирование сигнала источника

1 эталонного напряжения до момента 11 наступления равенства U «(„) д ((б ) (фиг. 2е) на входе компаратора 7. В момент равенства этих напряжений компаратор 7 срабатывает и формирователь 11 импульсов вырабатывает короткий импульс (фиг. 2r}. Этот импульс переключает триггер 12 в исходное состояние. Вторые ключи 3 и йервые ключи 6 всех ячеек закрываются, а блок 8 выборки-хранения переходит в состояние "Выборка" (фиг. 2б}. В момент срабатывания компаратора

7 выходное напряжение интегратора 4 и первой ячейки равняется 0 < 0 ) (о}

Таким образом выходной сигнал устройетва будет ревев()В „=К .Дт(а ) (фиг. 2д).

В момент прихода очередного импульса запроса на вход триггера 12 работа устройства повторяется снова. В зависимости от знака величины0инт-„-u<>)< .} (рааность между значением входного сйгнала в момент прихода очередного импульса запроса и выходным напряжением интегратора последней ячейки, равным значению входного сигнала в момент прихода предыдушего сигнала запроса) открывается второй ключ 3 (если разность отрицательна) или первый ключ 6 (если разность положительна}, и происходит интегрирование сигнала источника 1 эталонного напряжения до момента наступления равенства

)дат а Ь)(Од} °

В. момент срабатывания компаратора

7 выходное напряжение интегратора 4 первой ячейки пропорционально корню заданной. степени от входного сигнала. Степень извлекаемого корня равна числу последо» вательно включенных идентичных ячеек.

В предлагаемом устройстве переключение первого 6 и второго 3 ключей происходит только по сигналу запроса, поступаюшему на вход триггера, и накопление р ошибки, вызванной разбросом переключаюшего напряжения ключей, исключено. В свою очередь, использование быстродействуюших ключей и высокочувствительных компараторов препятствует возникновению погрешностей, связанных с задержкой иереключения ключей, что приводит к повышению точности устройства.

Формула изобретения

УстройстЬо для извлечения корня заданного порядка, содержашее источник эта5 911554 6 лонного напряжения и и ячеек, каждая ства, второй вход соединен с выходом нз которых содержит последовательно сое» триггера и первыми входами первого н диненные инвертор н первый ключ, выход второго элементов И, вторые входы котокоторого соединен с входом интегратора рых соединены с выходом комцаратора и и выходом второго кшоча, вход которого у через формирователь импульсов с вторым соединен с входом инвертора, выход нн- входом триггера, первый вход которого тегратора каждой ячейки соединен с вхо- является управшпошим входом устройства, дом ннвертора последующей ячейки, вход:.:выход блока выборки-хранения соединен инвертора первой ячейки соединен с ис- с вторым входом компаратора, а выходы точником эталонного напряжения, выход tO первого и второго энементов И соедине» интегратора первой ячейки является вы» ны соответственно с управляющими вхськшочей каждой ходом устройства, а выход интегратора, дами второго и первого кшоче кажд д- ячейки соединен с первым входом ком- . ячейки. паратора, о т л и ч а ю щ е е с я тем, .Источники информации, ! что, с целью повышения точности работы ts .принятые во внимание при эксперт изе. устройства, в.него введены блок выборки- 1. Авторское свидетельство СС

СССР хранения, первый и второй элементы И, % 729596, кп. G 06 Ci 7/20, 1980. формироватеп импульсов и триггер, при- 2. Авторское свидетельство СС

СССР чем первый вход блока выборки-хранения % 482761, ки. С 06 Я 7/20, 1975 является информационным входом устрой- рй (прототи ).

91 1554

Составитель Ю. Петренко

Редактор В. Петраш Техред С.Мигунова Корректор М. Немчик

Заказ 1131/42 Тираж 732 Подписное g>HNHH Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаа наб., д. 4/5

Филиал ППП Патент, г. Ужгород, уп.,Проектная, 4