Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

(ii)91 1627

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рес у (61) Дополнительное к авт. свид-ву р 748515 (22) Заявлено11. 03. 80 (21 ) 2893521/18-24 с присоединением заявки ¹ (23) ПриоритетОпубликовано 07.03.82. Бюллетень ¹ 9 (51) М. Ктт.з

6 11 С 29/00

Государствеииый комитет

СССР ио делам изобретений и открытий (33) УДК 681. 327 (088. 8) Дата опубликования описания 07.0382 (72) Авторы изобретения

В.И.Николаев, А.С.Горбенко и В (71) Заявитель. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и является усовер« шенствованием запоминающего устройства с самоконтролем.

По основному авт.св.9 748515 известно устройствб содержащее накопитель, регистры числа, группы элементов ЙЛИ, регистры адреса, счетчик адресов, блок контроля, блок управления, блок местного управления, коммутаторы и счетчик разрядов,причем выход накопителя.подключен к первым входам первого, второго и четвертого регнстров числа и ко входу третьего регистра чиода, входы накопителя соединены с виходами еле ментов ИЛИ, входы элеМентов ИЛИ пер" ной группы подключены к выходам перного .регистра:адреса и второго регистра адреса, вход которого соединен с выходом счетчика адресов,первый выход второго регистра числа подключен к одним из входов второй . группы элементов ИЛИ, вторые вход и выход второго регистра числа,соединены соответственно с выходом блока местного управления и первым входом блока контроля второй вход которо2 го соединен с выходом третьего регистра числа, выходы блока управления подключены к управляющим входам накопителя, регистров адреса, счетчика адресов, регистров числа, блока контроля, блока местного управления и коммутаторовт второй вход четвер.того регистра числа подключен к выходам первого коммутатора, а выходы — к другим входам элементов ИЛИ второй группы и первому входу второго коммутатора, выход которого соединен со вторым входом первого регйстра числа, выход которого подключен к первому входу первого:коммута-, тора, вторые и третьи входы nepsoro и второго коввлутатора соединены соответственно с первыми выходами блока контроля и счетчика разрядов,втоj рые выходы которых подключены соответственно ко входам счетчика разрядов и блока управления (13.

В этом устройстве при последовательной записи линейного участка программы или массива чисел данные, подлежащие записи в отказавшие разря25 ды ячеек, компануются.на отдельном. регистре в слово и записываются в резервную ячейку. При считывании программы или массива чисел вместо значений отказавших разрядов используют30 ся их истинные значения, содержащие"

911627 ся в Резервной ячейке. Однако если после записи программы или массива чисел появляются еще отказавшие разряды, то разряды резервной ячейки могут быть вставлены в места отказавшим разрядов неверно (со смещением на количество дополнительно отказавших разрядов}, Это приводит к нару шению работоспособности устройства, снижению его надежности.

Цель изобретения — повышение надежности устройства, Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем введены последовательно соединенные формирователь контрольных сигналов, дешифратор и сумматор, причем входы формирователя контроль15 ных сигналов подключены соответственно к выходам первого, второго и четвертого регистра числа, а выход соеди20 нен с одним иэ входов элементов ИЛИ второй группы, выход дешифратора соединен с одним из входов блока контроля, вход сумматора подключен к входу второго, регистра числа, а выход — ко входам первого и четвертого

25 регистров числа.

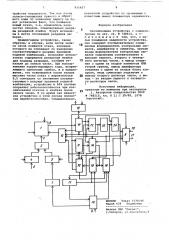

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит накопитель 1, имеющий входы 2, первую группу элементов ИЛИ 3, первый региСтр 4 адреса, второй регистр 5 адреса, нходы, 6 первого регистра адреса, счетчик

7 адресов. К выходам 8 накопителя подключены первые входы первого регистра 9 числа, второго регистра 10

35 числа, вход третьего регистра 11 числа и первый вход четвертого регистра 12 числа.

Устройство содержит также вторую группу элементов ИЛИ 13,блок 14 контроля, первый 15 и второй 16 коммутаторы, счетчик 17 разрядон, блок 18 управления, блок 19 местного управ40 ления, вход 20 и ныход 21 устройства, 45 формирователь 22 контрольных сигналов, дешифратор 23 и сумматор 24,представляющий собой группу сумматоров по модов элементов ИЛИ 13, выход которых подключен к входу накопителя 1.Вторые вход и выход регистра 10 числа соединены соответственно с выходом блока 19 местного управления и первым. входом блока 14 контроля, второй вход которого подключен к выходу третьего регистра 11 числа. Другой вход четвертого регистра 12 числа дулю два.

При этом входы 2 накопителя 1 сое- 50 динены с выходами элементов HJIH 3, входы которых подключены к выходам первого 4 и второго 5 регистра адреса. Вход регистра 5 соединен с выходом счетчика 7 адресов.-Выход регистра 9 числа и первый выход регистра

10 числа подключены к одним иэ выхоподключен к выходу первого коммутатора 15, а выходы регистра ) 2 — к другим входам элементов ИЛИ 13 и первому входу второго коммутатора 16, выход которого соединен с вторым вхо дом первого регистра числа 9, выход которого соединен с первым входом первого коммутатора 15.Вторые и третьи входы первого 15 и второго 16 коммутаторов соединены соответстненно с первыми входами блока 14 контроля и счетчика 17 разрядов. Второй выход блока 14 контроля подключен ко входу счетчика 17 разрядов, нторой выход которого соединен со входом блока 18 управления. Один из ныходов блока 18 управления подключен к управляющим входам накопителя

1, первого 4 и вторОго 5 регистров, адреса, счетчика (адресов первого 9, второго 10, третьего 11 и четвертого 12 регистров числа, блока 14 контроля и блока 19 местного управления, другие выходы блока 18 управления соединены с упранляющими нходами коммутаторов 15 и 16 ° Входы формирователя 22 подключены к выходам пер-" вого 9,второго 10 и четвертого 12 регистров числа, а выход — ко входам второй группы элементов ИЛИ 13 и входу дешифратора 23. Выход дешифратора 23 соединен со входами блока 14 контроля и сумматора 24. Другой вход сумматора 24 подключен к выходу второго регистра 10 числа, а выход - ко входам первого 9 и четвертого 12 регистрон числа.

Устройство работает следующим образом.

B исходном состоянии счетчик 17 разрядов обнулен, Для каждого линей, ного. участка программы или для массива чисел, которые будут записываться и считываться последовательно.выделяются резервные ячейки накопителя 1. В счетчик 7 адресов при этом записывается адрес первой резервной ячейки, а на вход ч регистра адреса

4 поступает адрес ячейки записываемого или считываемого массива чисел.

При записи число через вход 20 поступает в регистр 9,и содержимое регистра 4 адреса через элементы

ИЛИ 13 подается на вход накопителя 1 °

Обратный код из региства 9 черкез элементы ИЛИ 13 записываются в ячейку накопителя 1, Затем содержимое ячейки считывается на регистр 11.

После этого производится запись-счи-, тывание прямого кода числа на регистр

10. Причем при записи прямого кода одновременно с информационным разрядами записываются контрольные разряды корректирующего кода, которые формйруются формирователем 22 и через вторую группу элементов ИЛИ 13 поступают в накопитель 1. Содержимс е

911627

40 Если в маркерном разряде содержится код 1 и после записи массива чисел появится отказ, значение которого совпадает со значением соответствующего разряда хранимой кодовой

65 комбинации, то работоспособность ус. регистров 10 и 11 подается на блок

14 контроля. В случае, если отказавших разрядов в ячейке нет, то в регистр 4 на вход 6 подается следующий адрес и аналогично производится запись второго числа. Если же в ячейк есть отказавшие разряды, то блок 14 контроля и счетчик 17 разрядов выдают на,коммутатор 15 сигналы, по.кото рым иэ регистра 9 в младшие разряды регистра 12 передаются разряды числа соответствующие отказавшим разрядам ячейки. Эатем в блок 14 контроля, в счетчик разрядов 17 записывается код, соответствующий количеству отказавших разрядов ячейки.Из блока 18 управления в блок 19 местного управления поступает сигнал, по которому в маркерный разряд ячейки накопителя через регистр 10 записывается код 1 . Одновременно из регистра 10 поступает число в формирователь 22 и полученные контрольные разряды корректирующего кода записываются на .место ранее записанных контрольных разрядов. При этом искаженные разряды используются как истинные.

Аналогично производится запись числа во вторую отказавшую ячейку, только соответствующие разряды регистра

9 записываются в.следующие младшие незанятые разряды регистра 12. После того, как все разряды регистра 12 будут заполнены счетчик разрядов выдает сигнал заполнения в блок 18 управления. Адрес резервной ячейки из счетчика 7 поступает на регистр 5 адреса и через элементы ИЛИ 3 на вход, 2 накопления. Содержимое регистра 12 через элемент ИЛИ 13 записывается в первую резервную ячейку массива чи сел.Одновременно в эту же ячейку записываются контрольные разряды корректирующего кода (из формирователя 22). После этого ло сигналу из блока 18 управления в счетчике 7 адреса формируется адрес следующей резервной ячейки.

Чтение информации производится следующим образом.

В регистр 4 адреса через вход 6 подается адрес первой ячейки считываемого массива чисел, а в счетчик 7 адреса записывается адрес первой резервной ячейки чисел. Счетчик 17 разрядов при этом находится в нулевом состоянии. По сигналу из блока 18 управления производится передача содержимого счетчика 7 адреса через регистр 5 адреса и элементы ИЛИ 3 на вход 2 накопителя 1. Производится чтение числа .из первой резервной ячейки на регистр 10. Из регистра. 10 числа поступает в формирователь 22,где проверяется выполнение контрольных соотношений корректирующего кода и при ошибке вырабатывается нулевой синдром. Синдром поступает на дешифратор 23, который управляет работой сумматора 24.Скорректированное число. поступает в регистр 1с. Затем из регистра 4 адреса поступает адрес первой ячейки считываемого массива чисел и производится чтение на регистр

5 10 Если в маркерном разряде код

I I I t

0, то следовательно, до записи числа в .ячейке не было отказавших разрядов. Число из .регистра 10 поступает в формирователь 22 и с помощью дешифратора 23 и сумматора 24 корректируется разряд числа, который мог отказать после записи числа в ячейку. После этого число записывается в регистр 9, а затем поступает на выход 21.

15 Наличие кода 1 в маркерном разряде означает, что до записи числа в ячейке были отказавшие разряды. В случае, если после записи массива чисел не было отказов или пояЩ вился отказ, значение которого не совпадает со значением соответствующего разряда хранимой кодовой комбинации, то производится следующее.

Как и в рассмотренном случае коррек75 тируется разряд, который мог отказать после записи числа в ячейку и число записывается в регистр 9.Затем производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11, а также сигнал с дешифратора 23 о номере разряда, отказавшего после записи числа, подаются на блок 14 контроля.По сигналам из блока 14 контроля и счетчика

17 разрядов через второй коммутатор

16 производится передача необходимого числа младших разрядов регистра 12 в регистр 9. Причем в разряд, который отказал после записи числа и который исправлен корректирующим кодом не

40 передается информация с регистра 12.

Таким образом, разрядами резервной ячейки подменяются только те разряды ячейки, которые отказали до записи числа. Число иэ регистра 9 поступает на выход 21. В счетчик 17 разрядов записывается код, соответствующий количеству использованных разрядов регистра 12. Если все раз. ряды регистра 12 будут использованы, на что указывает соответствующее состояние счетчика разрядов 17, то по сигналу иэ блока управления в счетчике 7 адреса формируется адрес следующей резервной ячейки. Содержимое резервной ячейки считывается на ре55 гистр 10, корректируется и передается на регистр 12. Далее аналогично, продолжается считывание массива чи-

; сел.

911627

Формула изобретения

139/46 исное нч", оектная,4 тройства нарушается. Так как после записи-считывания прямого и обратного кода по заданному адресу не будет установлен факт, что появился новый отказ, т.е. изменилось количество отказов. Следовательно разряды резервной ячейки будут вставлены в места отказавших разрядов неверно.

Предлагаемое устройство, таким образом, в случае, если после записи числа появится отказ, значение которого не совпадает со значением соответствующего разряда хранимой кодовой комбинации, позволяет испольэовать содержимое резервной ячейки для подмены разрядов, которые отказали до записи чисел. При использовании корректирующего кода, исправияаяего одиночные ошибки, и в предложении, что появившийся после записи массива чисел отказ с вероятностью

0,5 совпадает со значением соответствующего разряда хранимой кодовой комбинации, устройство в 50% случаев сохраняет работоспособность при возникновении отказов в ячейках после записи чисел. В то время как известное устройство в этом случае полностью неработоспособно. Следовательно, описанное устройство по сравнению с известным имеет повышенную надежность

Запоминающее устройство с самоконтролем по авт. св. Р 748515, q тл и ч а ю щ е е с я тем, что., с целью повышения надежности устройства, оно содержит последовательно соединенные формирователь контрольных сигналов, дешифратор и сумматор, причем входы формирователя контрольных сигналов подключены соответственно к выходам первого, второго и четвер15 того регистра числа, а выход соединен с одним из входов элементов ИЛИ второй группы, выход дешифратора соединен с одним из входов блока контроля, вход сумматора подключен к

30 выходу второго регистра числа, а выход - ко входам первого и четвертого регистров числа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 748515, кл. G 11 С 29/00, 1978 (прототип!.