Реверсивный счетчик импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик «911737

Щ. (61) Дополнительное к авт. сеид-ву (22) Заявлено 070678 (2() 2624306/18-21 с присоединением заявки ¹вЂ” ($g)+ Кп 3

Н 03 К 23/00

Государственный комитет

СССР по делам изобретений и открытий (23) ПриоритетОпубликовано 070382. Бюллетень ¹ 9

Дата опубликования описания 070382 (И ) УДК 6 21. 374 . . 32 (088. 8) (72) Авторы изобретения

О.Д. Мураховский, В.A Бындыч, И.Н. Евстр и A.Б. Скрипник (7! ) Заявитель (54) PEBEPCHBHbl2 СЧЕТЧИК ИМПУЛЬСОВ

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых приборов, предназначенных для обработки знакопеременных величин.

Известен реверсинный счетчик импульсов, содержащий счетные разряды и блок элементов И (1).

Недостатком известного реверсивного счетчика является его низкое быстродействие.

Наиболее блиэок к предлагаемому реверсинный счетчик импульсов, содержащий счетные разряды, блок элементов И и коммутатор (2) .

Недостаток известного технического решения — низкое быстродействие, обусловленное наличием межразрядных элементов.

Цель изобретения — повышение быстродействия реверсивного счетчика импульсов.

Поставленная цель достигается тем, что в реверсинный счетчик импульсов, содержащий суммкрующий счетчик, поразрядные парафазные выходы которого подключены к первым входам блока элементов И, и коммутатор, входы которого соединены со входными шинами, дополнительно введены нычитающий счетчик и дополнительный блок элементов И, причем поразрядные парафазныв выходы вычитающего счетчика подклю5 чены к первым входам дополнительного блока элементов И, нторые входы которого подключены к первому управляю". щему выходу коммутатора, второйуправляющий выход которого соединен со вторыми входами блока элементов И выходы которого подключены к соответствующим установочным входам вычитающего счетчика, выходы дополнительного блока элементов И подключены к соответствующим устаноночным входам

1 . суммирующего счетчика, а счетные входы суммирующего и нычитающего счетчиков соединены соответственно со вторым и первым импульсными выходами коммутатора.

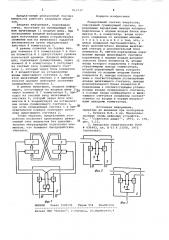

На фиг. 1 представлена функциональная схема реверсинного счетчика импульсов; на фиг. 2 и 3 — примеры выполнения коммутатора.

Реверсивный счетчик импульсов содержит суммирующий счетчик 1, вычитающий счетчик 2, блоки элементов И 3 и 4, коммутатор 5, состоящий, напри" мер, из элементов И 6 и 7, триггера

8 или переключателя 9 и входные шиЗО 10 и

9 117 37

Формула изобретения

Дуг, 1 4Ъг. У

ВНИИПИ Заказ 1149/51 954 Подписное

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,4

Предлагаемый реверсивный счетчик импульсов работает следующим образом. Входная информация, подлежащая счету, поступает на суммирующую 10 или вычитающую 11 входную шину. При поступлении входной информации от двух источников режим устройства(на сложение или на вычитание) задается автоматически путем переключения триггера 8 коммутатора 5. о

В режиме сложения на первых входах элемента И 6 коммутатора 5 и блоха элементов И 3 присутствует уровень логической единицы. Входная информация, подлежащая суммированию, через элемент И 6 коммутатора 5 поступает на счетный вход суммирующего счетчика 1, который через блок элементов

И 3 воздействует на установочные входы вычитающего счетчика 2, при этом вычитающий счетчик 2 в принудительном порядке повторяет состояние суммирующего счетчика 1.

В режиме вычитания, входная информация, поступающая на входную шину 11, через элемент И 7 коммутатора 5, приходи т н а счетный вход вычи т ающе го счетчика 2, который через блок элементов И 4 воздействует на установочные входы суммирующего счетчика 1, при этом суммирующий счетчик 1 в принудительном порядке повторяет состояние вычитающего счетчика 2 °

Таким образом, предлагаемое устройство позволяет производить реверсивный счет импульсов без дополни- З5 тельных межразрядных логических элементов, что повышает быстродействие счетчика.

Реверсивный счетчик импульсов, содержащий суммирующий счетчик, поразрядные парафазные выходы которого подключены к первым входам блока элементов И, и коммутатор, входы которого соединены со входными шинами, отличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены вычитающий счетчик и дополнительный блок элементов И, причем, поразрядные парафазные выходы вычитающего счетчика подключены к первым входам дополнительного блока элементов И, вторые входы которого подключены к первому управляющему выходу коммутатора, второй управляющий выход которого соединен со вторыми входами блока элементов И,.выходы которого подключены к соответствующим установочным входам вычитающего счетчика, выходы дополнительного блока элементов И подключены к соответствующим установочным входам суммирующего счетчика, а с етные входы суммирующего и вычитающего счетчиков соединены соответственно со вторым и первым импульсными выходами коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств.

М., Советское радио, 1975, с. 176, рис, 5. 13.

2. Авторское свидетельство СССР

Р 436443, кл. Н 03 К 23/00, 1972 (прототип).