Преобразователь напряжения в код

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Х, АВТ01е СКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социапнстичесиих

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 16.06.80 (21) 2940995/18-21 с присоединением заявки М (23)ПриоритетОпубликовано 30.03 82 Бюллетень №12

Дата опубликования описания 04.04.82 (51)М. Кл.

Н 03 К 13/17

fbcyaapctweiil квинтет

СССР по лелея нзаеретеннй . н етмрытнй (53) УДК 681. ,32 5(088. 8) (72) Автор изобретения

В. Э, Балтрашевич

Ленинградский ордена Ленина электротех им. В. И. Ульянова (Ле (7i) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

Изобретение относится к аналого-ци-

;фровым преобразователям и может быть использовано в области связи, вычисли- тельной и измерительной техники, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известен преобразователь напряжения . в код, содержащий блок сравнения, преобразователь код-напряжение, источник опорного сигнала, генератор импульсов, бпок, реализующий подразрядный метод, содержащий регистр и группу элементов (1).

Недостатком преобразователя являет1S ся низкая достоверность выдаваемых Кодов и большая погрешность преобразования, так как он может указывать на некоторый квант в то время как сигнала в этом кванте нет, и следовательно, повышается погрешность преобразования

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь напряжения в код, содержащий генератор импульсов, блок импульсов сравнения, первый вход которого соединен с выходом .датчика входного сигнала, а второй вход соединен с выходом преобразователя кода в напряжение, выполненного в виде матрицы R-2Р, аналоговый вход которого соединен с выходом источника опорного напряжения, а цифровые входы соединены с первыми выходами соответствующих разрядов блока реализации поразрядного метода, выход блока сравнения соединен с первым входом блока реализации поразрядного метода, введены бпок проверки достоверности, первый и второй триггеры, аналоговый ключ, элементы И и ИЛИ, причем первый вход бпока проверки достоверности соединен с выходом блока сравнения, второй вход соединен со вторым выходом блока реализации поразрядного метода, а третий вход соединен с выходом элемента И и вторым входом блока реализации пораэв " 1, кроме того, если блок сравнения выдавал-(сигнал U y М, то через четвертый элемент И сигнал появится на первом выходе блока проверки достоверноюти. На следующем такте, если ответ блока сравнения изменится, то через третий элемент И и элемент ИЛИ сигнал появится на втором выходе блока проверки достоверности, в противном случае сигнал появится на третьем выходе.

Сущность предлагаемого решения заключается в том, что для кодов, проверка достоверности которых не производится самим поразрядным методом, проводится дополнительная проверка и если эта проверка показывает, что сигнала в указываемом кванте нет, то начинается новый цикл преобразования того же сигнала.

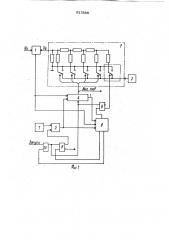

Устройство работает следующим образом.

Одновременно с установкой проверочной единицы.в младшем разряде регистра блока 4 реализации поразрядного метода (фиг. 1) производится запуск блока 8 проверки достоверности. Если на следующем такте ответ блока 1 сравнения меняется на противоположный, то на втором выходе блока проверки достоверности появляется сигнал, устанавливающий в 0" первый трщгер 6 и заканчивается преобразование. Если же ответ блока 1 сравнения не изменился и при этом она выдает сигнал Y > p то на первом выходе блока проверки достоверности 8 появится сигнал устанавливающий второй триггер 9 в "1 ", тем самым в цифроаналоговом преобразователе срабатывает аналоговый ключ и подсоединяет оконеч:ный резистор матрицы Я, -2Q,ê источнику

3 опорного напряжения, в результате чего величины текущего образцового уровня увеличиваются на один квант. На следующем такте, если ответ блока сравнения изменится, то сигнал со второго выхода бпока проверки достоверности заканчивает преобразование, в противном случае сигнал с третьего выхода пройдя через элемент ИЛИ 10 произведет начальную установку блока 4 реализации поразрядного метода, установит в "0 второй триггер 9, после чего начнется новый цикл преобразования.

Таким образом, введение допсюпп тельной проверки кодовых эквивалентов, достоверность которых не проверяется поразрядным методом, позволяет увеличить вдвое достоверность выдаваемых кодов, что в свою очередь устраняет опасность выдачи неверных кодов при наличии раз3 . 917338 4 рядного метода, третий вход которого соединен с единичным входом первого триг гера, выходом элемента ИЛИ и нулевым входом второго триггера, единичный выход первого триггера соединен с первым входом элемента,И, второй вход которого соединен с выходом генератора импульсов, нулевой выход первого триггера соединен с шиной Тотовность", а первый выход бпока проверки достоверности соединен щ с единичным входом второго триггера, второй выход соединен с нулевым входом первого триггера, а третий выход соединен с первым входом элемента ИЛИ, вто- рой вход которого соединен с шиной "3a- пуск, при этом единичный выход второго триггера соединен с входом младшего разряда преобразователя код-напряжение.

На фиг. 1 представлена функциональная схема преобразователя напряжения в код; на фиг. 2- один из возможных вариантов реализации блока проверки достоверности; на фиг, 3 — один из возможных вариантов реализации блока поразрядного метода; на фиг. 4 -пример, поясняю- . щий супоюсть преобразователя напряжения в код(сплошными линиями показана работа известного, а пунктирными — предлагаемого преобразователя напряжения s код), зо

Преобразователь напряжения. s код содержит блок 1 сравнения, преобразователь 2 код-напряжение, источник 3 опорного сигнала, бнок 4 реализации поразрядного метода, элемент И 5, первый триггер 6, генератор 7 импульсов, блок . 35

8 проверки достоверности, второй трщ гер 9, элемент ИЛИ 10.

Первый триггер (фиг. 2) служит для запоминания ответа бпока сравнения на

4О предыдущем такте. Сигналом начальной установки (не показан) второй и третий триггеры устанавливаются в 0". Сигнал установки проверочной единицы в младшем разряде регистра бпока реализации

45 ° поразрядного метода, поступая на второй вход блока проверки достоверности устанавливает в единицу второй триггер. Если на следующем такте ответ блока сраьнения изменится, то на выходе логического элемента неравноэначности появится сигнал неравнозначности, который пройдя через первый элемент И и элемент ИЛИ, выдает сигнал на втором выходе блока проверки достоверности и преобразование заканчивается. Если же ответ бпока срав-55 нения не изменился, то по сигналу равно-значности через второй элемент И второй триггер установится в 0", а третий5 Si 733 . личных аоМех (случайное отклонение измеряемой величины, сбой устройства сравнения, сбой дискретной части преобразователя).

Формула изо бретения

Преобразовагепь напряжения в код, со;держащий генератор импульсов, блок сравнения, первый вход которого соединей с выходом датчика входного сигнала, а второй вход соединен с выходом преобразователя кода в напряжение, выполнен« ного s виде матрицы R-2R, аналоговый вход которого соединен с выходом источника опорного напряжения, а цифровые входы соединены с первыми выходами соответствующих разрядов блока peans- зации поразрядного метода, выход бпо- 20 ка сравнения соединен с первым входом блока реализации поразрядного метода, отличаюшийсятем, что,сцелью повышения точности преобразования, в него введены блок проверки достовер- 25 ности, первый и второй триггеры, аналоговый ключ, элементы И и ИЛИ, причемпервый вход блока проверки aoегоsepmocти соединен с выходом бпока сравнения, !

8 6 второй вход соединен с вторым выходом блока реализации поразрядного метода, а третий вход соединен с выходом эле» мента И и вторым входом блока реа пв запии поразрядного метода, третий вход которого соединен с единичным входом первого триггера, выходом элемента ИЛИ и нулевым входом второго триггера, единичный выход первого триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, нулевой выход первого три гера соединен с шиной «Готовность«, а первый выход блока проверки достоверно- . сти соединен с:единичным входом второго триггера, егоpoN выход соединен с нулевым входом первого триггера, а третий выход соединен с первым входом элемента ИЛИ, второй вход которого соединен с шиной «Запуск", при этом единичный выход второго триггера соединен с входом младшего разряда преобразователя код» . напряжение, Источники информапии, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 451190, ил. Н 03 К 13/17, 2 5.07. 72..917335 йа,д Нобий цикл

g п ев5 аьодани, х... х я о

"Х... ХО/1

-4x" хоро

xg в3ь б цика, рво3уало5иний

Составитель Л. Беляева

Редактор Е. Кинив .Техреду Е.Харигончик Корректор О. Билак

Заказ 1911/76 Тираж 954 Поднисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектяаи, 4