Устройство временной задержки

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социапистичесиик

Респубяии

К АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву

{22) Заявлено 06.0979 {21} 2823039/18-21 (SI)h4. Кл.

Н 03 К 17/28 с присоединением заявки .%

ЭвудорстиыоЫ коиытот

СССР

Ilo долам кзо5уотеннВ

ы открытый (23) Приоритет

Опубликовано 300332, Бюллетень Р612

Дата опубликования описания 300382

{53) УД1(621 ° 374.. 5 (088. 8)

E.Ä.j1îñåâ, Ю.В.Давыдов, Е.И.Хальфи и ЕД,Лукоянова (72) Авторы изобретения (7t ) Заявитель (54) УСТРОЙСТВО ВРЕМЕННОЙ ЗАДЕРЖКИ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автома" тического управления в качестве реле времени.

Известны устройства, содержащие накопительный конденсатор, зарядную цепь, пиковый распределитель, катод" ный повторитель, ключ и дискриминатор. Принцип работы устройства ос16 нован на заряде и разряде накопительного конденсатора через резис" торы с разным значением сопротивлений I

Недостатком данного устройства . 15 является то, что точность его работы в значительной степени определя-. ется линейностью функции преобразования в области малых времен, т.е. на начальном участке- кривой заряда накопительного конденсатора.

Наиболее близким к предлагаемому является устройство, содержащее со-, единенные последовательно времяза. дающую цепь, повторитель, блок сра нения, источник опорного напряжения формирователь (21 °

Недостатком известного устройства является то, что точность его работы зависит от стабильности источника опорного напряжения и, кроме того, диапазон временной задержки ограничен величиной постоянной времени времязадающей цепочки.

Цель изобретения - повышение точности и расширение диапазона временной задержки.

Поставленная цель достигается тем, что в устройстве временной задержки, содержащем интегратор и последовательно соединенные источник опорного .напряжения, блок сравнения и формирователь, причем выход интегратора соединен с другим входом блока сравнения, выход источника опорного напряжения соединен с входом интегратора, выполненного в випе операционного усилителя с вре.

917347

0 „станет равным опорному напряжению о, когда время задержки не

Йувисит от величины опорного напряжения, Преимущество данного устройства по сравнению с известными заключается в повышении точности выдержки времени.

Формула . изобретения

8х.

ВНИИПИ Заказ 1912/77 Тираж 954 Подписное

Филиал ППП "Патент,", г. Ужгород, ул. Проектная, 4 мяэадающим конденсатором в цепи от рицательной обратной связи,. параллельно которому включен ключ, управляющий вход которого соединен с входной клеммой устройства.

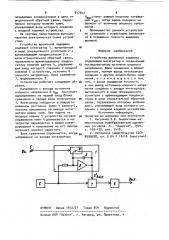

На.чертеже представлена функциональная электрическая схема устрой- ства.

Устройство временной задержки содержит интегратор 1, выполненный l0 в виде операционного усилителя 2 с времязадающим конденсатором 3 в цепи отрицательной обратной связи, параллельно времязадающему конденсатору включен датчик 4, управляю- 15 щий вход которого соединен с входно 1 клеммой 5 устройства, источник 6 опорного напряжения, блок сравнения формирователь 8, Устройство работает следующим об- 20 разом.

Напряжение с выхода источника опорного напряжения 6 U<> поступает одновременно на первый вход блока сравнения и первый вход интегратора 2s

1 ° Интегратор находится в заарретированном состоянии (ключ 4 замкнут), поэтому напряжение на выходе интегратора равно нулю. При подаче на входную клемму 5 устройства сигнала управления ключ 4 размыкается и интегратор переводится в режим интегрирования и напряжение на его выходе начинает линейно нарастать.

Блок сравнения опрокинется, когда напряжение на выходе интегратора

Устройство временной задержки, содержащее интегратор и соединенные последовательно источник опорного напряжения, блок сравнения и форми" рователь, причем выход интегратора соединен с другим входом блока сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в нем выход источника опорного напряжения соединен с входом интегратора, выполненного в виде операционного усилителя с времяэадающим конденсатором в цепи отрицательной обратной связи, параллельно которому включен ключ, управляющий вход которого соединен с входной клеммой устройства.

Источники информации, принятые во внимание при экспертизе

1. Маграчев З.В.. Аналоговые измерительные преобразователи одиночных сигналов, И., "Энергия", 1974, с. 169-172, рис. 7-10.

2. Авторское свидетельство СССР

Ю595698, кл. 6 04 F. lO/10 (прототип).