Устройство для контроля дешифратора

Иллюстрации

Показать всеРеферат

Союз Севетсинх

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и>918948

Ф г (6I ) Дополнительное к авт. свид-ву (22) Заявлено 15.08,80(2l ) 2977003/18-24 (81)М. Кп. с присоединением заявки №(06 F 11/10

3оеударстееииый комитет

СССР (23 ) П р иори тет (З) УДК681.326. .7 (088.8) IIo делам изобретеиий и открытий

Опубликовано 07.04.82. Бюллетень № 13

Дата опубликования описания 07.04.82 (72) Авторы изобретения

С. И. Петренко и А. И. Сахно (71) Заявитель . (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРА

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано для контроля различных дешифраторов.

Известно устройство дпя контроля дешифратора, содержащее дешифратор, мно» говходовую схему ИЛИ, схемы НЕ, И и схему нечетности 1 ).

Недостатком этого устройства является то, что оно не выявляет такие отказы в работе дешифратора, когда возбуждаются требуемая и нетребуемая шины, а также когда возбуждается нетребуемая шина.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля дешифратора, содержащее,блок аналогового суммирования, пороговые элементы, элемент ИЛИ (2).

Известное устройство работает следующим образом. Для выявления отказа шифратора в одном пороговом элементе устанавливается порог срабатывания, равный нулю. С ломошью этого порогового элемента выявляются отказы дешифратора, выражаюшиеся в отсутствии сигналов на его выходах при подаче на входы определенной кодовой комбинации. В другом пороговом элементе устанавливается порог срабатывания, превышающий номинапь ное значение выходного потенциала дешифратора. Таким образом, этот йорого. вый элемент способствует выявлению таких отказов дешйфратора, когда на двух и более выходах дешифратора одновремен» но появляются сигналы.

Однако известное устройство не конт ролирует соответствие выходного сигнала кодовой комбинации. Поэтому указанное устройство не фиксирует отказы дешифратора в случае, когда на pro выхх>де возбуждается нетребуемая шина.

Цель изобретения - повышение разрешающей способности контроля.

Поставленная цель достигается тем, что в устройство для контроля дешифра тора содержащее пороговый элемент и первый элемент ИЛИ, выход которого яв3 91894 пяется первым выходом устройства, выходы контролируемого дешифратора соединены со входами порогового элемента и являются группой входов устройства, выход порогового элемента соединен с первым входом первого элемента ИЛИ, введены второй и третий элементы ИЛИ, группа элементов И, группа элементов задержки, элемент задержки, триггер и элемент И, причем каждый выход контро- 1О пируемого дешифратора соединен с первым. входом соответствующего элемента

И группы, выход каждого элемента И группы соединен с соответствующим входом второго элемента ИЛИ, выход кото- 15 рого соединен с нулевым установочным входом триггера, управляющий вход устройства соединен со входом первого элемента задержки группы, со вторым входом первого элемента И группы, с пер- 20 вым входом третьего элемента ИЛИ, выход которого соединен с единичным установочным входом триггера и со входом элемента задержки, единичный выход триг- гера соединен с первым входом эпемента 25

И, выход элемента задержки соединен со вторым входом элемента И, выход которого „соединен со вторым входом первого элемента ИЛИ, выход каждого элемента задержки группы соедйнен с соответству- щ ющим входом третьего элемента ИЛИ, со вторым входом соответствующего элемента И группы и со входом последую= щего эпемента задержки группы.

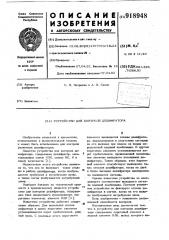

На фиг. 1 приведена функциональная

35 схема устройства для контроля дешифратора; на фиг. 2 и 3 - временные диаграммы работы дешифратора.

Предлагаемое устройство содержит пороговый элемент 1, элемент ИЛИ 2, 4О триггер 3, элемент 4 задержки, элемент

И 5, элементы ИЛИ 6 и 7, группу элементов .И 8, группу элементов 9 задержек, каждый выход которого соединен с первым входом 1+1 элемента

ß5

И 10 (= 1, 2, ..., ) группы элементов И 8, к другим входам которого под:ключены соответствующие выходы контролируемого дешифратора 1 1, объединенные со входами порогового элемента 1. Группа элементов 9 задержки содержит (n -1) элемента 12 задержки.

Выход элемента ИЛИ 2 соединен с нулевым управляющим входом триггера 3, выход которого соединен с первым входом элемента И 5, второй вход которого соединен через элемент 4 задержки с единичным управляющим входом триугера

3 и с выходом эпемента ИЛИ 6, входы которого, кроме первого, соответственно. соединены с выходами группы элементов

9 задержки, а первый вход элемента ИЛИ

6 соединен с управляющим входом устройства и со входом группы элементов

9 задержки и первым входом элемента

И 10 группы элементов И 8, выходы которого соединены со входами элемента

ИЛИ 2.

Выход элемента И 5 соединен с первым входом элемента ИЛИ 7, второй вход которого соединен с выходом порогового элемента 1, причем выход элемента

ИЛИ 7 является выходом устройства.

Устройство работает следующим образом„

В исходном состоянии триггер 3 устанавливается в нулевое состояние (низкий потенциал на прямом выходе). 11ели установки не указаны.

В режиме "Контропь" кодовые комбинации на вход дешифратора 11 подаются с произвольной частотой (период Т). Последоватепьность кодовых комбинаций выбирается так, что на выходах дешифратора 11 появляются сигналы в заранее заданной последоватепьности (например, в порядке возрастания, с 1-го по и- й).

Время задержки сигнала каждым элементом 12 задержки группа элементов

9 задержки равно периоду Т смены кодовых комбинаций на входе дешифратора

11, поэтому появление сигнала на выходе любого элемента 12 задержки группы элементов 9 задержки совпадает с появпением сигнала на соответствующем ему выходе дешифратора 11.

Время задержки 61 эпемента 4 задержки равно

Т

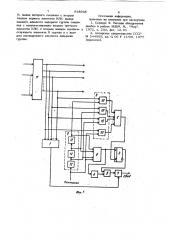

На временных диаграммах (фиг. 2 и

3) указаны сигналы на выходах соответствующих б псков.

Одновременно с подачей на входы дешифратора 1 1 первой кодовой комбинации на вход первого эпемента 12 задержки по управляющему входу устройства подается импульс, который через эпемент

ИЛИ 6 устанавливает триггер 3 в единичное состояние и одновременно задерТ живается на время — элементом 4 задержки. Кроме того, этот же импульс опрашивает первый выход дешифратора

11 на первом элементе И 10 группы эпементов И 8. Если же в этот момент на первом выходе дешифратора 11 присутствует сигнал, то, пройдя через первый элемент И 10, он появится на выходе элемента ИЛИ 2 и задним фронтом

918948

7 .И, выход которого соединен с вторым входом nepsoro элемента ИЛИ, выход каждого элемента задержки группы соединен с соответствующим входом третьего элемента ИЛИ, е вторым входом соответ s ствующего элемента И группы и с Входом последующего элемента задержки группы.

Источники информапии, принятые во внимание при экспертизе

1. Селлерс Ф. Методы обнаружения ошибок в работе ЭБВМ. М., Мир, 1972, с. 232, фиг. 12.10.

2. Авторское свидетельство СССР

Ж 544969, кл. 5 06 Р 11/00, 1977, (прототип ) .

918948

Составитель И. Сигалов

Редактор П. Макаревич Техред М. Надь КорректорО, Билак

Заказ 2143/33 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, уп. Проектная, 4