Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИВ

ИЗОВРЕТИН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i i>918974

Союз Советск их

Социалистических

Респубяик (6l) Дополнительное к авт. свнд-ву (22) Заявлено 21.08. 80 (2! ) 2974751/18-24 с присоединением заявки ЭЙ— (23) П риорнтет (51}M. Кл.

Q 1l С 29/00

Гесу арсташшыа «енктет

СССР ао аеааи изобретений и открытий

Опубликовано 07.04. 82. Бюллетень М 13 (53) УДК 681. 327 . (088. 8) Дата опубликования описания 07.04 ° 82 (72) Авторы изобретения

И.Б.Борисов, Г.П.Воронин, Н.N.Êîðáàøîâ и Я.А.Хетагуров

«Ф": ф Щф Я С ф 11 (71) Заявитель

0 . Я (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к запоминающим устройствам и может быть использовано, в частности, в информационно-управлявщих системах, работающих в режиме реального масшта" ба времени.

Известно устройство для защиты памяти, содержащее граничные регистры и компараторы для сравнения кода исполнительного адреса с кодами адресов, установленными в этих регистрах 111.

Недостатком этого устройства является невысокая надежность.

Наиболее близким техническим ре" шением к предлагаемому является устройство для защиты памяти, содержащее дешифратор адресов зон, блоки сравнения, соответствующие им пары элементов И, регистр и дешифратор признака обращения и два элемента

ИПИ, причем выходы дешифратора адресов зон подключены ко входам блоков сравнения, выходы которых соединены с первыми входами элементов

И, вторые входы элементов И соединены попарно с соответствующими BLI» ходами дешифратора признака обращения, вход которого подключен к выходу регистра признака обращения, выходы всех элементов И соединены с соответствующими входами первого и второго элементов ИЛИ (2).

Недостатком этого устройства яв10 ляется невысокая надежность, так как оно не позволяет. создавать защищаемые поля памяти различной конфигурации, а также требует избыточного объема памяти для размещения

15 программ..

Цель изобретения — повышение надежности устройства.

Укаэанная цель достигается тем, 20 что в устройство для защиты памяти, содержащее дешифратор кодов стра- ниц, регистр кодов-защиты страниц, элемент ИЛИ и первую группу элементов И, причем выходы деши4ратора ко918974

2S

3S

S0

55 дов страниц подключены соответственно к первым входам элементов И первый группы, вторые входы которых сое. динены соответственна с выходами регистра кодов защиты страниц, вход дешифратора кодов страниц и выход элемента ИЛИ являются соответственно первым входо и выходом устройства, введены дешифратор кодов абзацев и дешифратор кодов строк, входы которых являются соответственно вторым и третьим входами устройства, регистры кодов защиты абзацев,регистры кодов защиты строк, вторую и третью группы элементов И и группу элементов ИЛИ, причем выходы дешифратора кодов абзацев соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых подключены к выходам соответствующих элементов И первой группы, а третьи входы — к выходам соответствующих регистров кодов защиты абзацев, выходы дешифратора кодов страниц соединены с первыми входами соответствующих элементов.И третьей группы, вторые входы которых подключены к выходам соответствующих элементов И второй группы, а тре-. .тьи входы — к выходам соответствую-щих регистров кодов защиты строк, входы элементов ИЛИ группы соединены соответственно с выходами элементов

И третьей группы, а выходы элементов ИЛИ группы подключень., соответственно ко вхОдам элемента ИЛИ.

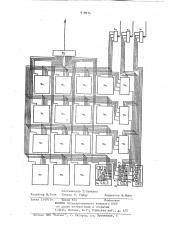

На чертеже изображена структурная схема предлагаемого устройства для защиты памяти объемом, например, в четыре страницы по четыре абзаца в каждой и по четыре строки в каждом абзаце.

Устройство содержит дешифратор

1 кодов страниц, дешифратор 2, кодов абзацев, дешифратор 3 кодов строк, регистр 4 кодов защиты страниц, элементы И 5 первой группы, логические блоки 6, содержащие элементы И 7 второй группы и регистры 8 кодов защиты абзацев, логические блоки, 9, садержащие элементы ИЛИ 10 группь1, регистры 11 кодов защиты строк и элементы И 12 третьей группы, и элемент

ИЛИ 13.

Устройство работает следующим образ ом.

Устройство выполняет аппаратурным путем проверку исполнительных адресов на совпадение их с разрешенными адресами.

Для каждой программы с целью обеспечения доступа только к выделенным ей участкам памяти - страницам, абзацам, строкам — управляющей программой формируются коды защиты этих участков. Перед началом выполнения оче< редной программы сформированные пози" ционные коды защиты заносятся в соответствующие регистры.4, 8 и 11 кодов защиты страниц, абзацев и строк.

За каждым разрядом этих регистров

4, 8 и ll закрепляются соответствующие страницы, абзацы и строки защищаемой памяти.

В соответствии с общепринятым принципом защиты, согласно которому разрешения должны преобладать над запретами, исходным состоянием всех:ре" гистров 4, 8 и 11 является нулевое.

Это значит, что нулевому состоянию разряда регистра 4 соответствует разрешение обращаться к соответствующей странице, единичному — запрещение. Аналогичные рассуждения относятся к регистрам 8 и 11.

Исполнительный адрес поступает на входы дешифраторов 1 2 и 3 причем

30 старшие разряды адреса поступают на .вход дешифратора 1, средние разрядына вход дешифратора 2 и младшие разряды —,на вход дешифратора 3.

Расшифрованный код страницы с выхода дешифратора 1 поступает на первый вход одного из элементов И 5. Ес" ли соответствующий разряд регистра

4, выход которого подключен ко второму входу этого же элемента И 5, находится в нулевом состоянии, то на выходе этого элемента И 5 появится сигнал, который иоступит во вторые входы всех соответствующих элементов И 7. На первый вход одного из этих элементов И 7 поступает расшифрованный код абзаца с выхода дешифратора 2. Если соответствующий разряд регистра 8,который соединен с третьим входом этого элемента И 7, находится в нулевом состоянии, то на выходе этого элемента И 7 появится сигнал, который поступит на вторые входы всех соответствующих элементов И 12. На третий вход одного из этих элементов И 12 поступает расшифрованный код строки с выхода дешифратора 3. Если соответствующий разряд, регистра 11, который соединен с третьим входом этого элемента И 12, 5 91 находится в нулевом состоянии, то на выходе этого элемента И 12 появится сигнал, который поступит на один из входов сответствующего элемента ИЛИ !О, а с его выхода - на вход элемента ИЛИ 13 и затем пройдет на выход устройства как. сигнал разрешения на обращение к памяти по дан" ному исполнительному адресу.

Таким образом, сигнал разрешения сформируется только при совпадении всех трех расшифрованных дешифраторами 1, 2 и 3 кодов страницы, абзаца и строки с нулевыми состояниями соответствующих разрядов регистров

4, 8 и 11. В противном случае сигнал разрешения будет отсутствовать, что и явится признаком несанкционированного обращения в память по данному адресу.

Технико-экономические преимущества предлагаемого устройства по сравнению с известным заключаются в повышении надежности устройства и обеспечении сокращения объема защищаемой памяти, необходимого для размещения программ защиты.

Источники информации, 35 принятые во внимание при экспертизе

1. Патент Великобритании

N- 1282б28, кл. 6 4 А, опублик. 1972 .

2. Авторское свидетельство СССР о 9 552641, кл. G ll С 29 00, 1977 (прототип) .

Формула изобретения

Устройство для защиты памяти, содержащее дешифратор кодов страниц, регистр кодов защиты страниц, элемент ИЛИ и первую группу элементов

И, причем выходы дешифратора кодов страниц подключены соответственно к первым входам элементов И первой .группы, вторые входы которых соединены соответственно. с выходамй регистра кодов защиты страниц, вход:.. де8974 6 шифратора кодов страниц и выход эле» мента ИЗЫ являются соответственно первым входом и выходом устройства, отличающееся тем, что, с целы повышения надежности устройства, оно содержит дешифратор кодов абзацев и дешифратор кодов строк, входы которых являются соответственно вторым и третьим входами устройства, 10 регистры кодов защиты абзацев, регистры кодов защиты строк, вторую и третью группы элементов И и группу элементов ИЛИ, причем выходы дешифратора кодов абзацев соединены с

15 первыми входами соответствующих элементов И второй группы, вторые входы которых подключены к выходам соответствующих элементов И первой группы, а третьи входы — к выходам

2О соответствующих регистров кодов защиты абзацев, выходы дешифратора кодов страниц соединены с первыми входами соответствующих элементов И тре" тьей группы, вторые входы которых подключены к выходам соответствующих элементов И второй группы, а третьи входы — к выходам соответствующих регистров кодов защиты строк, входы элементов ИЛИ группы соединены coyg ответственно с выходами элементов

И третьей группы, а выходы элементов

ИЛИ .группы подключе1ы соответственно к входам элемента ИЛИ.

9!8974

Составитель Т.Зайцева

Редактор М.Ткач Техред И. Гайду Корректор И.Пожо

Заказ 2149i34 Тираж б24 Подиисное

ВНИИПИ Государственного коьмтета СССР по делам изобретений и открытий !!3035, Москва, )!(-35, Раунская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул, Проектная, 4