Формирователь импульсов

Иллюстрации

Показать всеРеферат

Союз Советскими

Социапистииескин

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

N АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

H 03 К 3/ 353

Рщ(дарстаснный кюннтет

СССР ао делан изобретений н открмтнй

О"Убликованз 07.04.82. бюллетень ра 13

Дата опубликования описания 07.04 82 (5З) УЙК 621. 374..5(088,8) (72) Авторы изобретения

П. М. Гафаров, И. П. Лазаренко, А. С. Лушников и Ю. В. Минков (7l) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение оз носится к электратехнике и может быть использовано в импульсных интегральных схемах на МДП-транзисторах, и в особенности, в интегральных схемах íà МДПтранзисторах с обедненными нагрузкамнб

Известен формирователь имупльсов на МДП-транзисторах, содержащий повторитель и инверторы jig. I0

Недостатком этого устройства является низкая помехоустойчивость.

Наиболее близким к предлагаемому является формирователь импульсов, содержащий двухтактный каскад на

13

МДП-транзисторах, первый сложный инвертор с шиной питания и общей шиной, инвертор с нагрузочным МДПтранзистором, первый и второй дополнительные МДП-транзисторы, конденсатор, вход первого сложного инвертора и инвертирующий вход двухтактб кого каскада объединены и подключены к выходной шине, шина питания первогосложного инвертора подключена к истоку п<.рвого дополнительно МПП-транзис1ора, сток которого подключен к шине питания, а затвор — к выходу инвертора, выход первого сложного инвертора подключен к неинвертирующему входу двухтактного каскада и к входу инвертора, исток и затвор второго дополнительного МДП-транзистора подклю чены к выходу пвухтактного каскада, выходной шине и через конденсатор к шине питания первого сложного ин» вертора, а его сток подключен к шине питания (23.

Недостаток известного устройстванизкая помехоустойчивость °

Цель изобретения — повышение помехокоустойчивости.

Поставленная цель достигается тем, что в формирователь импульсов, содержащий дяухтактный каскад на МЦПтранзисторах обогащенного типа, первый сложный инвертор с шиной питания и общей шиной, инвертоп с нагру919062 эочньп1 МЛП-таанзисторам обепненного типа, первый и второй дополнительные

МДЛ-"1ранэисторы обедненного типа, шину питания, входную, выходную и

Общую шины, конденсатор, вход первоГс слажнага инвертора и инвертирующий вход двухтактнаго каскада объединены и подключены к входной шине, шина питания первого сложного инвертара подключена к истоку первого дополни- щ тельного МДП-транзистора обедненного типа, сток .которого подключен к шине питания, а затвор — к выходу инвертара, выход первого сложного инвертора подключен к неинвертируюп1ему входу, двухтакт-roro каскада и к входу ин вер1ара, исток и затвор второго дополнительно-о МДП-транзистора обедненного типа подключен к выходу двух1.актнагo I.ас када, выхад1 оЕ п1ине H че

12еэ ка11двнсатОР к IUHHp питания первого сложного инвертора, а его

c:roK парключен к шине питания, введен второй сложный инвертор, вход каторага подключен к входной шине, д а выход -- к Обп1ей шине первого сложна1 о и:-1верторау

Еажды11 иэ сложных инверторов содержит инвертар с нагруэочным КЦП-транзис IОРОМ ОбедненнОГО.типа и двухтакт ный каскад на МДП-транзисторах обеднегп1ОГО типа и обогащенного типа, причем вход инвертора объединен с инвертирующим входом двухтактного каскада, а выход инвертора подключен

35 к неинвертирующему входу двухтактнаго каскада.

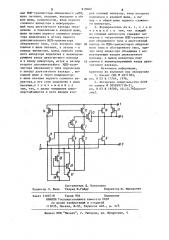

На чертеже изображена схема фор

>IHPOBBÒe22ß ИМПУЛЬСОВ.

ФО" мнраватель импульсов содержит

1IIHIf j 1 пи 1 ання > входную 1пин1 2 общую шину 3, выходную шину 4, первый сложный инвер1ор на МДП-транзисто-рах 5-8 двухтак гный каскад на МДПтранзистОрах 9 и 10, дОполнительные

МДП-транзистарь1 11 и 1.2,,инвертор о нагруэачным ЯП-транзис.1аром 12 на

МДП-транзи "ropax 13 и 14, канденса"ор 15, гторай -:сложный инвертор на

МДП-транзисторах 16 и 19, МДП-транзисторы 5, 6-9 9 I 0- 1 3 ф 1 6

56 обогащенного типа, МДП-транзисторы

7,8,11,12,14,18,19 и МДП-конденсатор 15 — обедненного типа. Устроиство работает следующим об5 разам.

Когда па входной шине формирователя установится уровень логической единиць:, транзисторы 5,6,9,16 и 17 открыты, и на выходной шине, затворах транзисторов 7,8,10-13,18,19 и истоках транзисторов 5 и 6 напряжение ниже поро-а транзистора.обогащенного типа, напряжение на затворе транзистора 9 равно напряжению питания, напряжение на конденсаторе

15 также близко к напряжению питанич. Статический ток, потребляемый схемой в этом состоянии, равен сумме токов насьпцения транзисторов

7,8,11,18 и 19.

Когда напряжение на входе начинает снижаться, гранэисторы 5,9, 12, 6 и 17 начинают закрываться, напряжение на истоках -.ðàíçèñòîðîâ 5 и 6 повьппается и ани быстро переходят в режим глубокой отсечки. Начина ется процесс быстрого заряда затворов транзисторов 10 и 13, и когда они аткрыва1отся, закрывается транзистор 6 предзаряда и изменение напряжения на выходной шине через емкость затвор-канал конденсатора

15 и транзистор 7 передается на затвор транзистора 14, чем обеспечивается условие, что транзистор

10 в течение всего переходного процесса эффективно открыт.

Кроме того, при необходимости исключить задержку начала процесса переключения «ыходнаго сигнала из состояния нуля в состояние единицы транзистор 10 в схеме может быть использован обедненного типа, однако мощность, потребляемая формиро- . вателем, возрастает.

Пречлагаемый формирователь по сравнени1о с изве< тным при равных потребляемой мощности и нагрузке имеет задержку импульса в.два раза меньше.

Использование предлагаемого формирователя импульса в БИС статического ОЗУ емкостью 1024 бит поэволяется получить в изделии статическую мощность 100 мБт при времени выборки 20 нс против 300 мБт и 20 нс соответственна у ОЗУ 2125 Н фирмы

IrI te I (США).

Формула изобретения

1, Формирователь импульсов, содержащий двухтактный каскад на МДНтранзисторах обогащенного типа, первый сложнь1й инвертор с шиной питания н общей шиной, инвертар с нагрузоч1п1м МДП-транзистором обедненного типа, первый и второй дапалнительСоставитель Д. Николаева

Редактор Л. Филь Техред И.Гайду Корректор.KI. Макаренко

Заказ 2160/18 Тираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

5 9 ные МДП-транзисторы обедненного тийа, шину питания, входную, выходную и общую шины, конденсатор, вход первого сложного инвертора и инвертирующий вход двухтактного каскада объединены и подключены к входной шине, шина питания первого сложного инвертора подключена к истоку первого дополнительного ИДП-транзистора обедненного типа, сток которого подключен к шине питания, а затвор — к выходу инвертора, выход первого слож« ного инвертора подключен к неинвертирующему входу двухтактного каскада и к входу инвертора исток и затвор второго дополнительного NQII-транзистора обедненного типа подключены к выходу двухтактного каскада, выходной шине и через конденсаторк шине питания первого сложного инвертора,aего сток подключен к шине питания,отличающийся тем, что, с целью повышения помехоустойчивости в него введен вто»

19062 6 рой сложный инвертор, вход которого подключен к входной шине, а выход — к общей шине первого сложно ". го инвертора, 2. Формирователь по п. 1, о т л ич а ю щ и .й с я тем, что. каждый из сложных инверторов содержит инвертор с нагрузочным МЛП-транзистором обедненного типа и двухтактный

10 каскад на МДП-транзисторах обедненного типа.и обогащенного типа, причем вход инвертора объединен с инвертирующим входом двухтактного каскада, а выход инвертора.под" 5 ключен к неинвертирующему входу двух" тактного каскада.

Источники информации, принятые во внимание при экспертизе

1. Патент США У 4071783, gg кл. Н 03 К 17/04, 1976.

2. Авторское свидетельство СССР по заявке У 2058597/18-21, кл. Н 03 К 19/08, 10.12.79(прото» тип).