Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

ОПИСЛНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()919073 (6l) Дополнительное к авт. свид-ву ¹ 790235 (22) Заявлено 29,09.80(2l ) 2987612/18-21 с присоединением заявки № = (23) Приоритет

Опубликовано 07.04.82. Бюллетень № 13 (5) )Я. )(д.

Н 03 К 5/19

Гооударстеапай комитет оо делам изооретеккй к отхрытнй (53) УДК621.374.,3(088.8) Дата опубликования описания 10.04.82 (72) Автор изобретения

В. А, 1" (огунов (71) Заявитель (54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР

Изобретение относится к технике связи и может использоваться в аппаратуре систем передачи дискретной информации.

По основному авт. св. № 790235, известен цифровой частотный детектор, содержащий цифровой измеритель длитель5 ности импульсов, выполненный в виде соединенных последовательно опорного генератора, ключа и реверсивного счетчика импульсов, выходы которого подключены

10 к входам элемента сравнения чисел, выходы подключенного к входу логического блока, причем установочный вход реверсивного счетчика импульсов подключен к первому выходу логического блока. Де15 модулированный сигнал подается на вход формирователя входного сигнала, выход которого подключен ко входу формирователя импульсов, счетному входу триггера и управляющему входу делителя частоты, прямой выход триггера подключен ко второму йходу логического блока, управляющему входу реверсивного счетчика импульсов и второму управляющему входу делителя частоты, на счетный вход которого подключен выход опорного генератора. Выход делителя частоты подключен ко второму входу формирователя импульсов, выход которого подключен к входу расширителя импульсов, выходом подключенного к управляющему входу ключа и третьему входу логического блс . ка, второй выход которого является выходом цифрового частотного детектоv М.

Цифровой частотный детектор работае1 по способу выделения пары импульсов, в разности длительностей которых сойержится разность между периодом входного частотно-манипулированного сигнала и периодом средней частоты этого сигна ла, Затем длительность пары увеличивается в К раз и определяется знак и величина разности длительности импульсов.

Недостатком цифрового частотного детектора является отсутствие возможности регулировки средней частоты детекти919073 руемого сигнала, что Обуспавливает EIQ»» личие искажений.

Лель изобретения — уменьшение искажений при детектировании.

Указанная цель достигается тем, что в цифровой частотный детектор дополнительно введены два клю I3, генератор тока разряда и блок управления, причем первый выход блока управления подключен к входу генератора тока разряда, !о выход которого подключен к первым входам дополнительных ключей, выходы которых подключены ко второму входу расширителя импульсов, а второй выход блока управления подключен к вторым входам дополнительных ключей, третьи входы которых подключены соответственно к прямому и инверсному выходам тр иггер а.

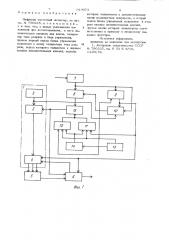

На фиг. 1 приведена блок=схема устройства; на фиг. 2 - диаграммы, поясняющие его работу.

Цифровой McTCTEII.IH детектор содержит цифрОВОЙ Яз!»!ерптель 1 дпи ельпости

ИМПУЛЬСОВ, ВЫПОЛНЕННЫЙ В ВИДЕ СОЕДИпенных последовательно опорного генератора 2, первого ключа 3 и реверсивного счетчика 4 импульсов, выходы которого подключены к входам элемента 5 сравнеНИЯ ЧИСЕЛ, ВЫХО ОМ ПОШСЛЮЧЕННОГО К ВХОду логического олока 6, причем установочный вход реверсивного счетчика 4 импульсов пошаночен к первому выходу логического блока б, второй выход кс

T-I3I3oãî чвчяется выходом детектора» . !e-.

35 модулируемый сигнал подается !Ьа вход формирователя 7 входного сигнала, выход которого подкачан к входу формирователя 8 импульсов, счетному входу р,иггера 9 и управляюи,ему вход" делителя

-.! О

10 частоты,; счетному входу де;!!Г!е.

10 частоты подключен в!яход опорного генератора 2, а выход делителя 10 час= тоты подключен к второму входу формирователя 8 импульсов. Прямой вьо;Од риггера 9 подключен к второму управля- "" ющему входу делителя 10 частоты, третьему входу ключа 11, управпя!о!Лему входу реверсивного счет-вика 4 импульсов и второму входу логического блока 6, 30 а инверсный выход триггера 9 подключен к третьему входу кп,"оча 12, Первый вь:-ход блока 13 подктпочен ко входу I cEIepaтора 14 тока разряда, а второй выход к вторым входам ключей 11 и 12. Вьжод генератора 14 .тока разряда !!Одкл!Очен ! к первым входам ключей 1 и 1, Bbl= ходы которых подкпючень к второму

Входу расширителя ) 5 пмпуль О!3, к пер вому входу которого подключен выход, формирователя 8 импульсов. Выход расширителя 15 импульсов подключен к управляющему входу первого ключа 3 и третьему входу логического блока В.

Устройство работает следующим образом.

На вход детектора приходит периодический часточно-манипулированный сигнал, который формирователем 7 входного с!Ьгнала преобразуется в прямоугольные импульсы, следующие с частотой входного сигнала (фиг. 2a). Е(икп работы детектора, совпадающий с периодом колебания на .выходе триг!ера 9 (фиг.2О), состоит из двух периодов !зходного сигнала, в каждом из которых формируется по одному информационному импульсу (фиг. 2о, "-). Начало цикла совпадает с отрицательньтм фронтом напряжения на выходе формирователя 7 входного сигнала (фиг. 2a), вызывак щим положительный фронт напряжения на прямом выходе триггера 9 (фиг. 2!3), Рассмотрим цикл работы детектора.

В момент прихода первого отрицательного фронта сформированного импульса (фиг. 2а) выход триггера 9 установится в ", " (фиг. 25), выход формирователя 8 импульсов установится в "1" (фиг. 2c), а делитель 10 частоты разблокируется и Ilaчнет деление Опорной частоты (фиг.2Ь)

Одновременно выходной сигнал триггера

9 управляет направг:ением счета реверспвг!Ого с сотника 4 импульсов таким образом, что если выход триггера 9 — в

"единичном" состоянии, то !3еверсивнььй счетчик 4 пмпупьсо..з считает в "положи.!епьном" направлении, а если в "нулевом" состоянии, то с lp.т идет I3 отрицательном" напр !алании. Делитель 10 частоты вырабатывает импульсы отрицатальной попярностп (фпг. 2Ч,), поступающие на второй вход формирователя 8 импульсов и устанавливающие его в "0" (фиг. 2P.), Эти импульсы имеют частоту

: Х с!, (ГДЕ 3 — ЦЕЛОЕ ЧИСЛО, а "..-3 — СРЕДняя .-Гаcтота;астотпо-манипупированного с! IIала) и сл!3(!пучь! Относительно момен

Та запуска делителя 10 (фиг. 2Ь) на время L.. .Величина выбирается из условий . т -!,. (где "„,, — . аксимапьный г,я ы. 1 и !! период входного колебания с учетом !! Оздейств ия пОмех, а Imp — м ин имальный пери!3д входного колебания с учетом возле!!Ствия помех, величина !ч выбирается с таким расчетом, чтобы =- одной стороI!el период делителя 10 частоты попуч! лся минимальным, а с другой стороны, 5 91 чтобы период, получившийся на выходе делителя 10 частоты (фиг. 2ъ), был больше величины (-Т, ц,+Т ) с учетом помех и несинхронности входной частоты и частоты опорного генератора

2. С приходом следующего отрицательного фронта сформированного входного сигнала (фиг. 2cl) формирователь 8 импульсов устанавливается в "1, прямой выход триггера 9 устанавливается в "0" и меняет направление счета реверсивного счетчика 4 импульсов. Следующий . затем импульс с выхода делителя 10 (фиг. 2,) устанавливает формирователь

8 импульсов в "0" (фиг. 2д). При совпадении положительного полупериода сформированного входного сигнала и отрицательного полупериода напряжения на выходе триггера 9 вход делителя 10 частоты блокируется и делитель 10 устанавливается в исходное состояние.

9073 б

СО

С5

В предлагаемом устройстве за счет введения регулировки средней частоты детектора его собственные искажения при расстройке канала Hà величину 2,З

+2,5 Гц уменьшены на 2%, что обеспечивает повышение качества детектирования, 55

Таким образом, за время цикла работы детектора на выходе формирователя

8 импульсов формируется пара импульсов (фиг. 2д), положительные фронты которых следуют с частотой входного сигнала, а отрицательные фронты — со средней частотой этого сигнала. Сформированные таким образом импульсы (фиг.2д) поступают на вход расширителя 15 импульсов, где (за счет разности времени заряда и разряда емкости) их длительность увеличивается в К раз (фиг. 2e).

Импульсы с выхода расширителя 15 подаются на управляющий вход ключа 3 для пропуска на счетный вход реверсив ного счетчика 4 импульсов серии импульсов с выхода опорного генератора 2, частота которого много больше и кратна средней частоте входного сигнала детектора. Во время первой серии импульсов опорной частоты реверсивный счетчик 4 импульсов читает в "положительном" направлении, а во время второй серии в отрицательном". В случае равенства входнойчастоты детектора средней частоте оба импульса íà BbixoABx формирователя 8 импульсов и разрешителя 15 импульсов равны между собой, и по окончании счета в отрицательном" направлении на выходе реверсивного счетчика импульсов 4 устанавливается исходное значение. Если выходная частота равна „, „, то второй импульс пары на выходе расширителя 15 импульсов короче первого на величину К (Т, Т ) и число на выходе реверсивного счетчика 4 импульсов по окончании сче» та больше исходного значения. Если входная частота равна,, то второй им-каv. пульс на выходе расширителя 15 импульсов длиннее первого на величину K-(Тср — Т,„„ ) и число на выходе реверсивного счетчика 4 импульсов по окончании счета меньше исходного значения.

По окончании счета в отрицательном" направлении в блоке 6 происходит формирование импульса записи (фиг. 2 ), который записывает полученную с выхода элемента 5 сравнения чисел информацию и записывает в реверсивный счетчик 4 импульсов исходное значение. Элемент 5 сравнения чисел производит постоянное сравнение числа, записанного в реверсивном счетчике 4 импульсов, с записанным в нем исходным состоянием счетчика 4 и на выходе элемента 5 сравнения чисел появляется "0" либо "1, в зависимости от того, больше записанного числа текущее значение пли меньше. При необходимости подстройки средней частоты изменяется коэффициент расширения K одного из импульсов, для чего блок 13 управления подает на входы ключей 11 или 12 разрешающий сигнал (в зависимости от знака расстройки средней частоты), а на генераторе 14 тока разряда устанавливает значение тока разряда, зависящее от величины расстройки, Прямой и инверсный выходы триггера 9, подключенные на входы 11 и 12 ключей, положительной полуволной разрешают поступление разрядного тока на вход расширителя 15 импульсов. Если блок 13 управления подает разрешающий сигнал на вход ключа 12, то разрядный ток генератора 14- тока разряда поступает на вход расширителя 15 импульсов во время второй половины цикла работы детектора и уменьшает коэффициент расширения второго импульса пары, что приводит к увеличению средней частоты детектора на величину, определяемую током разряда. Если блок 13 управления подает разрешающий сигнал на вход ключа 13, то разрядный ток поступает на вход расширителя 15 импульсов во время первой половины цикла работы детектора, что приводит к уменьшению средней частоты де тектора.

7 9190

Формула изобре тен ия

Цифровой частотный детектор, по авт, св. N. 790235, о т л и ч а ю ш и й— с я тем, что, с целью уменьшения ио- 5 кажений при детектировании„ в него дополнительно введены два ключа, генератор тока разряда и блок управления, причем первый выход блока управления подключен к входу генератора тока разряда„выход которого подключен к первым входам дополнительных ключей, выходы которых подключены к дополнительному входу расширителя импульсов, а второй выход блока управления подключен к вторым входам дополнительных ключей, третьи входы которых подключены соответственно к прямому и инверсному выходам триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 790235, кл. Н 03 К 5/19, 14.09,78.

919073

Составитель В. Потапов

Редактор Е, Кинив Техред М. Надь Корректор Е. Рошко

Заказ 2161/39 Тираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., л. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4