Устройство для определения достоверности контрольной двоичной информации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЯЬС7ВУ н»919118

{61) Дополнительное к авт. свид-ву (22) Заявлено 1О.10.79 (21) 2851600/18-09 с присоединением заявки ¹ (23) Приоритет

H 04 L 1/00

Н 04 L 11/08

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано р 704.82.6 ® eHb № 13 (53) УДК 621. 394. .6 (088.8) Дата опубликования описания 0 704,82 (72) Автор изобретения

В.Г.Каминский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ

КОНТРОЛЬНОЙ ДВОИЧНОЙ ИНФОРМАЦИИ

Изобретение относится к радиотехнике и может использоваться для размеров и контроля параметров дискретного канала связи.

Известно устройство для определения достоверности контрольной двоичной информации, содержащее последовательно соединеные первый сумматор и первый выходной клапан, последовательно соединенные второй сумматор и второй выходной клапан, последовательно соединенные счетчик и входной триггер, выход которого подключен к управляющему входу первого выходного клапана, первый формирователь контрольной последовательности, первый выход которого подключен к одному иэ входов первого сумматора, и второй формирователь контрольной последовательности, первый выход которого подключен к одному из входов второго сумматора, другой вход которого соединен со вторым выходом первого формирователя контрольной последователь- 25 ности (1).

Однако в известном устройстве для определения достоверности контрольной двоичной информации требуется значительное время.

Цель изобретения — сокращение времени определения достоверности.

Поставленная цель достигается тем, что в известное устройство введены третий сумматор, первый элемент ИЛИ и последовательно соединенные анализатор, дополнительный триггер и второй элемент ИЛИ, при этом второй выход второго формирователя контрольной последовательности подключен к второму из входов третьего сумматора, выход которого подключен к входу счетчика, выход которого подключен к другому входу дополнительного триггера, выход которого подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом входного триггера, с первым входом первого формирователя контрольной последовательности и с другим входом второго элемента ИЛИ, выход которого подключен к первому входу второго формирователя контрольной

I. oñëåäoâàòåëьíîcTê, разрядные выходы которого подключены к входам анализатора, а второЙ вход соединен с другими входами первого и третьего сумматоров и со вторым входом первого формирователя контрольной последова919118 тельности, а выход первого элемента

ИЛИ подключен к другому входу второго выходного клапана.

При этом каждый формирователь контрольной последовательности содержит последовательно соединенные входной 5 элемент совпадения, выходной управляемый регистр., выходной сумматор и входной клапан, выход которого подключен к другому входу выходного управляемого регистра, дополнительный 10 выход которого подключен к другому входу выходного сумматора, а другой вход входи -го клапана соединен с соответствующим входом входного элемента совпадения. 15

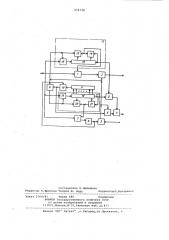

На чертеже представлена структурная электрическая схема предлагаемого устройства.

У тройство для определения достоверности контрольной двоичной информации содержит первый и второй сумматоры 1 и 2, первый и второй выходные клапаны 3 и 4, первый и второй элементы ИЛИ 5 и 6, третий сумматор 7, счетчик 8, входной триггер 9, дополнительный триггер 10, анализатор 11, первый формирователь 12 контрольной последовательности, состояший из входного клапана 13, выходного сумматора 14, входного элемента 15 совпадение и выходного управля- емого регистра 16, второй формирователь 17 контрольной последовательности, состоящий из входного элемента 18 совпадения, выходного управляемого регистра 19, входного кла- 35 пана 20 и выходного сумматора 21.

Устройство работает следующим образом.

Перед сеансом замера параметров 4Q канала связи входной триггер 9 со входа устройства устанавливается в единичное состояние, закрывая первый выходной клапан 3 и через первый элемент ИЛИ 5 второй выходной 45 клапан 4, а также как управляющий сигнал поступает на вход первого формирователя 12 и через второй элемент ИЛИ 6 на вход второго формирователя 17, устанавливая их в режим приема синхросигнала и разрешая режим формирования контрольных йоследовательностей.

Сигналы управления закрывают цепи прохождения сигналов обратной связи выходных управляемых регистров

16 и 19 через выходные сумматоры

14 и 21 на входных клапанах 13 и 20 и открывает через входные элементы

15 и 18 совпадения цепи прохождения сигналов со входа устройства (из

60 канала связи) на заполнение выходных управляемых регистров 16 и 19. На втором формирователе 17 начинается ooUecc проверки последовательности, поступающей из канала связи на ее 65 соответствие выбранному закону формирования комбинаций.

Сигналы с выходного сумматора 21 поступают на вход третьего сумматора 7, на другой вход которого поступают символы из канала связи непосредственно.

При наличии факта передачи комбинаций в канале связи и отсутствии помех в канале связи с выхода третьего сумматора 7 будет поступать нулевая последовательность. При дости>кении определенного порога, который определяется диапазоном просчета подряд принятых нулевых символов счетчиков 8, на era выходе проявляется сигнал, поданный к установочным входам входного и дополнительного . триггеров 9 и 10. В результате этого открываются первый и второй выходные клапаны 3 и 4, а первый и второй формирователи 12 и 17 переключаются из режима синхронизации в режим ге-. нерирования контрольных последовательностей. Первый и второй формирователи 12 и 17 работают синхронно, последовательности сигналов, поступающие на входы второго сумматора 2 полностью совпадают, и через открытый второй выходной клапан 4 на выход устройства поступает нулевая последовательность, характеризующая нор.мальный режим работ. Одновременно с этим через открытый первый выходной клапан 3 с первого сумматора 1 на выход устройства поступает поток ошибок. Он образуется путем позначного сравнения последовательности, формируемой первым формирователем

12 и последовательности, поступающей из канала связи.

Так как после фазирования эти последовательности совпвлвит, то пои отсутствии помех в канале связи с первого сумматора 1 поступают нули.

Наличие искажения приводит к несоответствию последовательностей и приводит к появлению единиц на выходе первого сумматора 1, что и является потоком ошибок.

Через определенное время сработает анализатор 11, настроенный на определенную комбинацию сигналов, формируемых на регистре 19. По этому сигналу дополнительный триггер 10 устанавливается в единичное состояние, закрывает через первый элемент ИЛИ

5 второй выходной клапан 4 и переключает второй формирователь 17 из режима формирования контрольной последовательности в режим синхронизации. После этого второй формирователь 17 работает в, режиме синхронизации, как это было описано при первоначальном включении в связь.

При этом первый формирователь 12 продолжает работать в режиме форми919118 рования контрольной последовательности, продолжая режим замера ошибок.

После выделения порога срабатывания управляющий сигнал со счетчика 8 вновь переключает дополнительный триггер 10 в положение, когда 5 второй формирователь 13 вновь устанавливается в режим генерирования контрольной последовательности, с одновременным открыванием цепи проверки синфазности через второй выходной 10 клапан 4.

После пересинхронизации второго (формирователя 17 его фазовое положение будет синхронным с фазовым положением канальной последоватльности. !5

В случае, если эа эТот цикл замера прибор расфазирован не был,это фазовое положение соответствует фазовому положению первого формирователя 12, что фиксируется нулевой последо- 2О вательностью, выдаваемой со второго сумматора 2 через. второй выходной клапан 4 потребителю.

В случае сбоев прибора в цикле замера эти последовательности не совпадают и на выход устройства поступают единицы, свидетельствующие о необходимости стирания потока ошибок за последний цикл замера.

Поскольку сигналы с анализатора 11ЗО поступают периодически, то с таким же периодом производится переключение второго формирователя 17 из режима генерирования контрольных последовательностей в режим синхронизации.

Таким образом, в режиме синхронизации одновременно ведется замер параметров канала связи независимо от времени синхронизации второго формирователя 17, за счет чего объем 4О набираемых статистических параметров канала связи за один и тот же интервал времени существенно возратает, что и предопределяет в конечном итоге сокращение времени опре- 45 деления достоверности.

Формула изобретения

1. Устройство для определения достоверности контрольной двоичной информации, содержащее последовательно соединенные первый сумматор и первый выходной клапан, последовательно соединенные второй сумматор и второй выходной клапан, последовательно соединенные счетчик и входной триггер, выход которого подключен к управлякщему входу первого выходного клапана, первый формирователь контроль ной последовательности, первый выход которого подключен к одному из входов первого сумматора, и второй формирователь контрольной последовательности, первый выход которого подклю чен к одному из входов второго сумматора, другой вход которого соединен со вторым выходом первого формирователя контрольной последовательности, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени определения достоверности, введены третий сумматор, первый элемент ИЛИ и последовательно соединенные анализатор, дополнительный триггер и второй элемент ИЛИ, при этом второй выход второго формирователя контрольной последовательности подключен к одному из входов третьего сумматора, выход которого подключен к входу счетчика, выход которого подключен к другому входу дополнительного триггера, выход которого подключен к одному из входов первого элемента ИЛИ, другой вход которого соединен с выходом входного триггера, с первым входом первого формирователя контрольной последовательности и с другим входом второго элемента ИЛИ, выход которого подключен к первому входу второго формирователя контрольной последовательности, разрядные выходы которого подключены к входам анализатора, а второй вход соединен с другими входами первого и третьего сумматоров и со вторым входом первого формирователя контрольной последовательности, а выход первого элемента ИЛИ подключен к другому входу второго выходного клапана.

2. Устройство по п.1, о т л и ч а— ю щ е е с я тем, что каждый форми.— рователь контрольной последовательности содержит последовательно соединенные входной элемент совпадения, выходной управляемый регистр, выходной сумматор и входной клапан, выход которого подключен к другому входу выходного управляемого регистра, дополнительный выход которого подклю,чен к другому входу выходного сумматора, а другой вход входного клапана соединен с соответствующим входом входиого элемента совпадения.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 440044, кл. H 04 L 1/00, 1971 (прототип).

9191 I8

Составитель E.Ëþáèìîâà

Редактор А.Фролова Техред М. Надь Корректор@.Макаренко

Заказ 2164/41 Тираж 685 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035,Москва,Ж-35,Раушская наб.,д.4/5

Филиал ППП" Патент",r.Óæãîðîä,óë.Ïðîåêòíàÿ, 4