Демодулятор фазоманипулированного сигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиин

Социалистических

Республни

< 919151 (61) Дополнительное к авт. свил-ву N 758560 (22) Заявлено 27.06.80 (21) 2949663/18-09 с присоединением заявки № (28) Приоритет (51)М. Кл.

Н 04 1 27/22

3Ьеудерстекниый комитет

СССР ао делам изобретений н открытий

Опубликовано 07.04.82 Бюллетень № 13

Дата опубликования описания 07.04.82 (53) УДК 621,394..142 (088,8) (72) Авторы изобретения

В, А. Бархота, В. В. Горшков, С. А. Рубцов и А (71) Заявитель (54) ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННОГО

СИГНАЛА

Изобретение относится к телеграфии.

По основному авт. св. М 758560 известен демодулятор фазоманипулированного сигнала, содержащий генератор импульсов, первый дискретизатор, генератор опорного сигнала и последовательно соединенные сумматор, квантователь, первый перемножитель, ко второму входу которого подключен выход генератора опорного сигнала, накопитель, коммутатор и решающий блок, последовательно соединенные т0, блок выделения сигнала и блок автоматической регулировки усиления, выход которого через генератор импульсов подключен к первому входу второго днскретиэатора, второй вход и выход которого соединены соответственно с выходом первого элемента задержки

1j и первым входом сумматора, ко второму входу которого подключен выход второго элемента задержки, вход которого соединен с выходом первого дискретизатора и первым выходом второго перемножителя, второй вход и выход которого соединены соответственно с первым входом генератора опорного сигнала и первым входом измерителя интенсивности помехи, второй вход которого соединен со вторым входом генератора опорного сигнала, дополнительные выходы которого подключены к соответствующим входам измерителя интенсивности помехи, третий вход и выходы которого соединены соответственно со вторым выходом коммутатора и входами блока выделения сигнала, при этом вход первого элемента задержки соединен со входом первого дискретизатора, а на входы генератора опорного сигнала поданы, соответственно сигналы тактовой и несущей частоты (1), Однако в известном демодуляторе недостаточная помехоустойчивость.

Цель изобретения — повышение помехоустойчивости.

Указанная цель достигается тем, что в известный демодулятор фаэоманипулированного сигнала введены последовательно соединенные делитель напряжения и второй решающий блок, причем один из выходов измерителя интенсивности помехи соединен с одним из входов делителя напряжения, дру3 9 гой вход которого соединен с другим выходом квантователя, другой вход которого соединен d выходом второго, решающего блока.

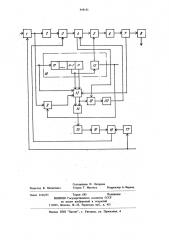

На чертеже изображена структурная электрическая схема предлагаемого демодулятора.

Демодулятор содержит дискретизатор 1, элемент 2 задержки, сумматор 3, квантователь 4, перемножитель 5,накопитель 6, коммутатор 7, решающий блок 8, перемножитель 9, генератор 10 опорного сигнала, содержащий. регистр 11 сдвига с обратной связью и модулятор 12, измеритель 13 интенсивности помехи, блок 14 выделения сигнала, блок

15 автоматнческой регулировки усиления (АРУ), генератор 16 импульсов, элемент 17 задержки, дискретизатор 18, делитель 19 напря>кения и решающий блок 20.

Устройство работает следующим образом.

На вход дискретизатора 1 поступает аддитивная смесь помехи и сигнала, где производится ее квантование по времени. Далее квантованная по времени смесь сигнала и помехи поступает на элемент 2 задержки, где задерживается на время, необходимое для рабаты измерителя 13 и блока 14, и на перемножитель 9, являющийся синхронным детектором по помехе, где умножается на опорный сигнал по несущей частоте.

С выхода перемножигеля 9 снимается сигнал, позволяющий измерителю 13 измерить амплитуду помехи в отсчете смеси сигнала и помехи. C помощью блока 14 и блока 15 этим напряжением управляется амплитуда генератора 16 импульсов. Сигнал с выхода генератора 16 импульсов через дискретизатор 18 попадает на. сумматор 3, где суммируется с квантованной по времени смесью сигнала и помехи.

Чтобы отсчеты сигнала и помехи поступили на сумматор 3 одновременно с отсче19151 4 тами сигнала смещения (сигнала с выхода генератора 16 импульсов), включен элемент

17. Отсчеты смеси сигнала, помехи и сигнала смещения квантуются по уровню в квантователе 4, умножаются в перемножителе 5 на опорный сигнал и поступают в накопитель 6 со сбросом, где происходит их накопление эа период следования бита информации. В конце периода накопления сигнал

1й с помощью коммутатора 7 подается на решающий блок 8, после чего накопитель 6 обнуляется сигналом с коммутатора 7.

Сигнал с измерителя 13 поступает на делитель 19, на который также поступает сиг15 HcLI с квантователя 4. Делитель 19 выполняет операцию деления двух напряжений и на его выходе получается сигнал, пропорциональный отношению этих напряжений, который через решающий блок 20 поступает аа квантователь 4, Таким образом, в предлагаемом демодуляторе повышается помехоустойчивость.

Формула изобретения

Демодулятор фазоманииулированного сигнала по авт. св, N 758560, о т л и ч а юшийся тем, что, с целью повышения

30 помехоустойчивости, введены последовательно соединенные целитель напряжения и второй решающий блок, причем один из выходов измерителя интенсивности помехи соединен с одним из входов делителя напряжения, другой вход которого соединен с другим выхо33 дом квантователя, другой вход которого соединен с выходом второго решающего блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР М 758560, кл. Н 04 1 27/22, 17.08.78 (прототип).

919151

Составитель Н. Лаэарева

Техред Т, Маточка Корректор А. Ференц

Редактор В. Пилипенко

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 2166/43 Тираж 685 Подписное

ВНИИПИ Государственного комитета СССР по делам нэобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5