Цифровой измеритель средней частоты

Иллюстрации

Показать всеРеферат

O Il И С А Н И Е ()920555

ИЗОВЕИтИНИЯ

С ото э Советски к

Социапнстичесиии республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву и 705360 (22)»" » о 140 780 (21) 2958829/1 8-21 с присоединением заявки УтЪ (23) Приоритет

Опубликовано 150482, Бюллетень М 14

Дата опубликования описания 1у482 (53)М. Кл.

G 01 R 23/00

Гооударотееииый комитет

СССР иа делам изобретений и открытий (53) УДК 621 ° 317 . 76 (088.8) (72) Авторы б (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СРЕДНЕЙ ЧАСТОТЫ

Изобретение относится к электроиз,, мерениям.

По основному авт. св. и 705360 известен цифровой измеритель средней частоты, содержащий дешифратор, соединенный через последовательно соединенные декадный умножитель и делитель частоты с одной из групп входов блока вентилей делителя частоты, другая группа входов которого

to соединена с первыми выходами е младших разрядов реверсивного счетчика, элемент совпадений, один из входов которого соединен со входом делителя частоты, другой с выходом блока

15 вентилей делителя частоты, а выход со входом реверсивного счетчика, второй выход реверсивного счетчика присоединен ко входу дешифратора, первый, второй и третий дополнительные элементы совпадений, у которых входы первого и второго элементов соединены соответственно с выходами (m-1) -го и m-го разрядов реверсивного счетчика выходы первого и второго дополнительных элементов совпадений и один из входов (m-1) "го разряда реверсивного счетчика соединены соответственно со входами третьего добавочного элемента совпадения, выход которого соединен со входом элемента 9 (m-1)-го разряда и и одним из входов старших и разрядов реверсивного счетчика, второй вход которого соединен со входом дешифратора 1 m-го разряда реверсивного счетчика (1).

Недостатком известного измерителя является отсутствие необходимого масштабирования измерителя в реальном диапазоне измеряемых величин ионизирующих излучений, что снижает оперативность измерения.

Цель изобретения - повышение быстродействия измерений.

Поставленная цель достигается тем, что в цифровой измеритель сред ней частоты, содержащий дешифратор, 3 9205 соединенный через последовательно присоединенные декадный умножитель и делитель частоты с одной из групп входов блока вентилей делителя частоты, другая группа входов которого соединена с первыми выходами m младших разрядов реверсивного счетчика, элемент совпадений, один из входов которого соединен со входом делителя частоты, другой с выходом блока 1О вентилей делителя частоты, а выход ,со входом реверсивного счетчика, второй выход реверсивного счетчика присоединен ко входу дешифратора, первый, второй и третий дополнитель 15 ные элементы совпадений, у которых входы первого и второго элементов соединены соответственно с выходами (m-l) - го и m-ro разрядов реверсивного счетчика, выходы первого u zp второго дополнительных элементов совпадений и один из входов (m-l)го разряда реверсивного счетчика соединены соответственно со входами третьего добавочного элемента совпа- z5 дений, выход которого соединен со входом элемента 9 (m-l).-го разряда и одним из входов старших и разрядов реверсивного счетчика, второй вход которого соединен со входом дешиф- 5О ратора m-ro разряда реверсивного счетчика, введены блок памяти, сум" матор и блок управления, один выход которого соединен с управляющим входом группы старших разрядов реверсивного счетчика, а второй выход блока управления соединен через . элемент памяти с.первым входом сумма тора, второй вход которого подключен к одному из выходов группы старших разрядов реверсивного счетчика, и кроме того, декадный умножитель состоит из К ключей, входы управления которых соединены с выходами дешифратора, информационные входы подклю" чены к .ши ам сигналов опорных частот, а выходы соединены между собой.

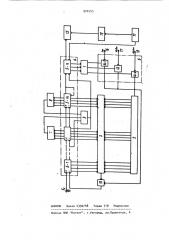

На чертеже показана структурная электрическая схема предлагаемого измерителя.

Измеритель содержит дешифратор 1, делитель 2 частоты, блок 3 вентилей, реверсивный счетчик 4, состоящий из m rpynn 5-1-5-m младших разрядов и группу 5-п старших разрядов, де- 55 кадный умножитель 6, элемент И 7-10, блок 11 управления, элемент 12 памя" .ти, сумматор 13. Декадный умножи55 4 тель 6 содержит ключи 14-1-14-К, где

К - число разрядов дешифратора.Входной сигнал подан на входную шину

15. На шины 16-18 поданы сигналы опорной частоты fon 10 fon, Устройство работает следующим образом.

На вход "Сложение" реверсивного счетчика 4 поступают входные импульсы. Последние пересчитываются в группах m младших разрядов реверсивного счетчика 4. При переполнении

m младших разрядов появляется сигнал

"Переполнение", который поступает на группы и старших разрядов реверсивного счетчика 4, предназначенную для измерения диапазона входной частоты. Коды обоих частей е и .п реверсивного счетчика поступают на входы блока 3 вентилей и на дешифратор 1, Дешифратор 1 управляет ключа. ми умножителя 6, которые в зависимости от диапазона измеряемой частоты пропускают на входы элемента

И 10 и делителя 2 определенное значение опорной частоты (fon, 10fon и т.д.), Код с делителя 2 поступает на другие входы блока 3, где он сравнивается с кодом ре.версивного счетчика 4, а выходной сигнал с блока 3 управляет элементом И 10 таким образом, что в установившемся режиме на входе "Вычитание" реверсивного счетчика 4 поступают сигналы с частотой, равной коду реверсивного счетчика 4. При этом входная частота равна частоте обратной связи (на входе элемента И 10), а код реверсивного счетчика 4 пропорционален измеряемой частоте.

Таким образЬм, при переполнении

m разрядов реверсивного счетчика и при дальнейшем увеличении входной частоты и переходе ее в более старший диапазон, в m-ом разряде счетчика 4 устанавливается число, соот- . ветствующее измеряемой величине, а в группе и старших разрядов -,код диапазона измерения, !

При уменьшении входной частоты заем импульса осуществляется со входа (m-1) -го разряда. При этом элементы И 7-9 вырабатывают сигналы при кодах в-го и (m-1) -ro разрядов соответственно 1000 и 0000. Таким образом, при уменьшении входной частоты . переход ее в более низкий диапазон

6 формула, изобретения

920555 производится со сдвигом на. один десятичный порядок.

По сигналу из блока 11 коды диапазона входных частот и коды показателя степени измеряемой физической величины .соответственно из и старших разрядов реверсивного счетчика из элемента 12 поступают на . сумматор Т3, в котором эти два кода,складываются, s результате чего на его выходе появляется код, автоматически и однозначно указывающий диапазон измеряемых частот, унитывающий динамику изменения диапазонов входных импульсов. 15

Код элемента 12 памяти устанавливается вручную для каждого конкретного случая.

Таким образом, предлагаемое устройство,позвоЛяет динамически сме- 2О щать шкалу диапазона измерения на, необходимое число десятичных разрядов, обеспечив масштабирование измерителя в реальный диапазон из.меряемых величин ионизирующих излу чений. Это повышает оперативность измерений различными типами блоков детектирования.

1 ° Цифровой измеритель средней частоты по авт.св. 1705360, о т л и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены блок памяти, сумматор и блок управления, один выход которого соединен с управляющим входом группы старших разрядов реверсивного счетчика, а второй выход блока управле" ния соединен через элемент памяти с первым входом сумматора, второй вход которого подключен к одному из выходов группы старших разрядов реверсивного счетчика.

2. Измеритель по п.1., о т л ич а ю шийся тем, что декадный умножитель состоит из К ключей, входы управления которых соединены с выходами дешифратора, информационные входы подключены к шинам сигналов опорных частот, а выходы соеди" нены между собой.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

1705360, кл. G 0 1 R 23/OQ, 03,01.77.