Генератор псевдослучайных кодов

Иллюстрации

Показать всеРеферат

CoIo3 Советсккк

Социалистические

Республик

<и>92О718 (6l ) Дополнительное к авт. саид-ву (22) Заявлено 090780 (21) 2953927/18-24

Г с присоединением заявки РЙ (23) Приоритет (5! )М. Кл.

G 06 F 7158

Гееудеретеениый комитет

СССР (53) УДК 681.325 (088,8y па делам изобретений и открытий

Опубликовано 15,04. 82. Бюллетень И 14

Дата опубликования описания 15,04.82

P. E. Богуславский, В.А. Бродко, Л.ф. Карачу

А . И. Романкевич, N.X. Ñëop÷íñêèé и И. T.×åð (72) Авторы изобретения,Jg p р

1 )

Специальное проектно- конструкторское и тфхнологиыеское бюро реле и автоматики (7t) Заявитель (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ КОДОВ

Изобретение относится к вычислй тельной технике и может быть исполь. зовано в аппаратуре контроля и диагностики цифровых блоков для выработки псевдослучайных испытательных сигналов с заданными свойствами, а также для формирования псевдослучайных последовательностей, необходимых для различных стохастических вычислительных устройств.

Известен генератор равномерно распределенных псевдослучайных кодов, содержащий регистр сдвига с сумматорами по модулю два в цепи обратной связи 11.

Однако использование известного генератора в качестве источника испытательных сигналов, которые подаются на входы цифровых схем для проверки правильности их функционирования, ограничивается, так как порядок следования кодов в последовательности кодов, формируемых такими генераторами, носит случайный характер.

Иогут возни кнут ь ситуации, когда входные си гналы не определяют одно з на чно, к а к должн а сработать испытуемая схема, т.е. возникает так называемая "гонка фронтов". Неопделенное поведение схемы затрудня" ет достоверную оценку правильности ее функционирования.

Источник псевдослучайных кодов должна вырабатывать только такие последовательности, соседние коды в которых отличаются только в одном разряде. В литературе такие коды получили название псевдоцикли- ческих кодов, так как они имеют одно общее свойство с циклическим кадом: з данный момент времени только один двоичный разряд меняет свое значение - переключается.

Применение псевдоциклических кодов не ограничивает времени проверки цифровых комбинационных схем, поскольку вероятность появления определенной двоичной комбинации на

3 92071 выходах генератора псевдоциклического кода равна вероятности появления этой комбинации на выходах генератора равномерно распределенного псевдослучайного кода. Однако

1 при проверке цифровых схем, содержащих сдвиговые регистры или счетчики, применение псевдоциклического кода может существенно увеличить время проверки, поскольку средняя 16 частота переключения для каждого входа проверяемой схемы при псевдоциклическом коде в rl/2 раз ниже, чем при равномерно распределенном псевдослучайном коде (где и - число входов) . Для сокращения времени проверки в генераторе псевдоциклического кода должна быть предусмотрена возможность задания вероятности изменения состояния каждого из разрядов генерируемого псевдоциклического кода. Тогда при низкой средней частоте переключения может быть достигнута относительно высокая частота переключения на отдельных входах проверяемой схемы (например на сдвигающих входах регистров и счетных входах счетчиков).

Наиболее близким к предлагаемому является генератор псевдослучайных кодов, содержащий блок формирования равномерно распределенных псевдослучайных чисел, регистр выходного кода, входы которого связаны с выходами блока формирования равномерно

35 распределенных псевдослучайных чисел, и блок задания веса кодов, включенный в цепь обратной связи регистра кода (2).

Однако оно не позволяет получать последовательность пневдоциклических кодов. Кроме того, не предусмотрена возможность изменения вероятности переключения (изменения сос; тояния) каждого из разрядов гене45 рируемых кодов.

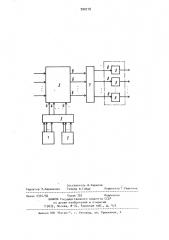

Цель изобретения - расширение функциональных возможностей генератора за счет получения последовательности псевдослучайнь|х циклических кодов с заданными вероятностями переключения каждого из разрядов кода, Укаэанная цель достигается тем, что в известный генератор псевдослучайных кодов, содержащий блок формирования равномерно распределенных псевдослучайных чисел, группу т ри ггеров, выходы которых являются выходами генератора, введены коммута тор, счетчик, блок памяти и дешифра (ор, выходы которого соединены со счетными входами соответствующих триггеров группы, а входы дешифратора подключены к соответствующим выходам блока памяти, адресные входы которого соединены с выходами коммутатора соответственно, входы которого соединены с выходами счетчика и блока формирования равномерно распределенных псевдослучайных чисел соответственно, информационные входы блока памяти являются вхо. дами генератора, На чертеже изображена структурная схема генератора.

Генератор содержит блок 1 формирования равномерно распределенных псевдослучайных кодов и счетчик 2, выходы которых соединены с входами коммутатора 3, выходы коммутатора 3 подключены к адресным входам 4 блока памяти 5. Выходы 6 блока памяти 5 подключены к входам дешифратора 7, выходы которого соединены со счетными входами 8 три ггеров 9. Выходы триггеров 9 подключены к выходным каналам генератора. Информационные входы блока памяти являются входами генератора.

Генератор функционирует следующим образом.

На информационных входах блока памяти 9 выставляются коды номеров выходных каналов генератора, Каждый из кодов номеров выходных каналов записывается в ячейки блока памяти 9, причем для каждого из кодов выбрано определенное число ячеек блока памяти 5, в которые записывается код одного и того же номера выходного канала, Это позволяет при условии равновероятного перебора адресов блока памяти 5 считывать из него коды номеров выходных каналов с заданной для каждого канала частотой.

В процессе заполнения блока памяти 5 коммутатор 3 подключает выходы счетчика 2 к адресным шинам 4.

Счетчик 2 обеспечивает последовательное заполнение всех ячеек блока памяти 5 кодами номеров выходных каналов.

После того, как заполняется блок памяти 5, коммутатор 3 отключает адресные входы 4 от счет чика 2 и подключает их к блоку формирования

9207! 8 б выходных каналов в процессе генерации циклических кодов позволяет е значительной степени оптимизировать процесс контроля. При контроле схем, состоящих иэ различных участков, интенсивное функционирование (переходы в различные состояния) которых возможно только при вполне определенном различном темпе поступлеIo ния переключающих входных сигналов, последнее свойство предлагаемого генератора позволяет сократить время контроля и повысить его полноту, формула изобретения равномерно распределенных псевдослучайных кодов. Блок 1 формирует на адресных входах 4 с одинаковой вероятностью все возможные адреса ячеек блока памяти 5. Считываемые из ячеек коды номеров каналов поступают по шинам 6 на входы дешифратора 7. В результате в каждом такте возбуждается один из выходов дешифратора 7 и на счетный вход 8 одного из триггеров 9 поступает счет" ный импульс. Именно этот триггер из всех триггеров 9 изменяет свое состояние на противоположное. 1аким образом новый код отличается от пре- iS дыдущего кода только в одном разряде. Так как частота появления кодов йомеров выходных каналов на шинах 6 соответствует заданному распределению этих кодов в ячейках блока па- 2О мяти 5, то частота изменения состояний соответствующих триггеров 9, а следовательно и выходных канапов мо" жет изменяться в необходимых пределах. При получении на выходах гене- 25 ратора достаточно длинной последовательности псевдослучайных цикличес" ких кодов, за счет соотВетствующего заполнения .ячеек блоков памяти можно осуществлять управление задани- ЗО ем вероятности изменения каждого из разрядов циклических кодов на выходах генератора.

По сравнению с известным данный генератор обладает дополнительными возможностями, позволяющими улучшить

его свойства как источника вероятностных испытательных сигналов для контроля цифровых блоков. Сама по себе воэможность генерации псевдо- 4в случайных циклических кодов обеспе" чивает надежную гарантию того, что на входы испытуемой схемы не поступают запрещенные для данной схемы последовательности наборов вход-, 4> ных сигналов. В результате этого упрощается проведение анализа состояний схемы в процессе контроля, .повышается полнота и достоверность контроля. Кроме того, возможность широкого изменения вероятности переключения состояния каждого иэ

Генератор псевдослучайных кодов,, содержащий блок формирования равномерно распределенных псевдослучайных чисел, группу триггеров, выходы которых являются выходами генерато" ра,отли чающийся тем, что, с целью расширения функциональных возможностей генератора за счет формирования последовательности псевдослучайных циклических кодов с заданными вероятностями переключения каждого из разрядов кода, он содержит коммутатор, счетчик, блок памяти и дешифратор, выходы которо" го соединены со счетными входами со. ответствующих триггеров группы, в входы дешифратора подключены к со" ответствующим выходам блока памяти, адресные входы которого соединены с выходами коммутатора соответственно, входы которого соединены с выходами счетчика с блока формирова" ния равномерно распределенных псевдослучайнфх чисел соответственно, информационные входы блока памяти являются входами генератора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство CCCP

М 468231, кл. G 06 F 1/02, 1976, 2. Авторское свидетельство СССР

И 696510, кл. G 06 F 1/02,1977 (про" тотип), Составитель A.Êàðàñîâ

Техред И,Гайду Корректор Г, Решетник

Редактор Л.Авраменко

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4

Заказ 2344/56 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква„ Ж-35, Раушская наб., д.. 4/g