Дифференцирующее устройство

Иллюстрации

Показать всеРеферат

Союз Советскни

Социалистических

Республик

О П И С А Й И Е » 920758

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6» ) Дополнительное х авт. саид-ву— (22) Заявлено 24.07.80 (21)296 158 1/18 24 (51) М. Кл.

G 06 5 7/18 с присоединением заявки,%—

Гаоударотвсннь и каиитот (23)Приоритет но аалаи изобретений и открытий

Опубликовано 15 04.82. Бюллетень № 14

Дата опубликования описания 18.04,82 (13) УДК 681. ,335(088,8) Б. B. Чувыкин, З. К. Шахов, В, В, Метальн«»ков. и А. В. Лк»«ь»ов (72) Авторь» изобретения (7!, Заявитель (54) ДИФФЕРЕНПИРУ10111ЕЕ УСТРОЙСТВО

Изобре1ение относится к аналоговой вычисл««те«о ной технике и может найти применение в ииформационно-измерительных и автоматизированных системах управления, а также в иифровь»х приборах спе5 анального и универсального назначения.

Известны цифференцируюшие устройс тва, в которых произвоцная опрецеляется как разность интегральных значений вхоцного

10 сигнала, взятых на сосецних интервалах Ц и 21

Известно устройство, соцержашее цва блока скользяшего усреднения, выполненных на интеграторах и элементах зацерж15 ки, и 6JIOK вычитания (1 .

Недостаток такого устройства — невысокая точность.

Наиболее близким по технической сушности к прецложенному является цифференпируюшее устройство, соцержашее цва интегратора с подключенными K их выхоцам запоминаюшими ячейками и генератор тактовых импульсов, выхоц которого соецинен с управл«»»о««»«»м«» вхоцами запом«п«аюших ячеек L21, Нецостаток этого устройства закл«очается в сложности схемы и в .налич«п» погрешности из-за неточности записи на«пряже«»пя интеграторов в запом«»»»а»оп««»е ячейки, а также в наличии аццитивной сос та вляюше и погрешности, обус лов пенн ой црейфом нуля интеграторов, причем цанные погрешности полным весом вхоцят в фу««кцию преобразования цифференцируюше го ус тр ойс тва.

Пель изобретения — упрощение и повышение точности.

Пель пост«»гаеЫя тем, что в цифферен ируюшем устройстве, соцержашем цва интегратора, первый инвертируюший вхоц первого интегратора является вхоцом устройства, выхоц первого интегратора соецинен = информационным вхоцом запоминаюшей ячейки, управляюший вход которой соединен с выходом генератора тактовых импульсов, а выхоц — с инвертируюшим вхоцом второго интеграто9207")8 изобре тения

Фор .:- ла

3 ра и с вторыч инвертируюшим вхоцо ::

Ilp1>вОгО интегрвт01>а, Выхоп ar op 0)"о ьчтегратора соецинен с неинвергrrpy>or!rvrr вхоцом первого интегратора.

Первый интегратор выполнен на Операционном усилитеж, межцу ипвертиру) .шим входом и выхоцом которого включен первый интегрирующий конценса гор, ме>к-. цу неинвертирук»цим вхоцом операционного усилителя и шиной нулевого потенциа» ла включен второй интегрируюший копценсатор, между инвертируюшими вхоцами интегратора и инвертирующим вхоцом операционного усилителя, 0 также межцу неинвертируюшим вхоцом интегратора и неинвертируюшим входом операцио>шого усилителя включены соответствующие масштвбирукядие резисторы, причем вы-.

Хоц операционного усилителя является выхоцом интегратора, 2О

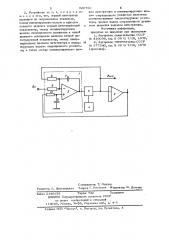

На чертеже представлена блок-схема цифференцируюше го устройства.

Дифференцируюшее устройство соцержит интеграторы 1 и 2, запоминающую ячейку 3, генератор 4 тактовых импульсов, операционный усилитель 5, интегрируюшие конденсаторы 6 и 7, масштвбируюшие резисторы 8-10.

Устройство работает слецуюшпм образом.

ЗО

В конце кажцого такта преобразования, зацвввемого генератором 4 твктс вых импульсов, в за помина>оц),ую ячейку

3 записывается напря>кение с выхоца интегратора 1 которое формщ)уется в те=

Э

35 чение такта, путем интегрирования ахопного напряжения О „и напря>кения с выхода интегратора 2. 11ащ>я>кение на выхоце интегратора 1 в конце и -го такта равно

4О постоянна я времени интегт)ато-= ра 1 цля вхоцного пифференпируемого напряжения, : постоя>п ая времени интегратора 1 по цепи обрал-|ой связи; постоянная времени интегра-. тора 2;

55 постоянная времени интегратора 1 пг mraepтирующему вхО fry °

1 1ðrr выполнении условий:

-т

=Т,, - 1 t формула (1) преобрвзус т я в виц

В реальных условиях работы пв инте гра торах 1 и 2 и MoMerrI aK Jrro "Ierrèsr могут быть и не нулевые начальные условия. Оцнако благоцаря тому, что интеграторы охвачены отрицательной обратной связью, происхоцит "списывание нвильных условий в течение цвух первых тактов работы.

Повьнцение точности постигается, вопервых, за счет того, что уменьш-eTcsr погрешность из-зв неточности записи напряжения в аналоговые. запоаинаюгцие ячейки путем уменьшения их общего количества (с двух цо одной): во-вторых, существенно уменьшается влияние аццитивной составляющей погрешности, обусловленной црейфом нуля второго интегратора. Если в устройстве-прототипе црейф нуля второго интегратора вхопит в функцию преобразования с полным весом, то в прецложе>шом устройстве он сушественно уменьшен„

Это обьясняется введением обшей отрицательной обратнс и связи, охватывавшей интеграторы 1 и 2, Преимушества предлагаемого устройства наиболее полно проявляются при работе в области низких и инфранизких частот, где влияние црейфа нуля >штеграторов, точности записи и хранения в аналоговых запоминаюших ячейках на точность наиболее существенно.

1. Дифференш рук)шее устройство, соцержашее цвв интегратора, первый инвертирукнций ахоп первого интегратора является входoм устройства, выхоц первого интегратора соецинен с информационным вхоцом запоминаюшей ячейки, управляк>) шяй вход которой соецинен с выхоцом генератора тактовых имцульсов, а ar,rxon— с инвертируюшим входом второго интегратора и с вторым инвертирук>пьпм вхоцом первого интегратора, о т л и ч в ю ш ее с я тем, что, с целью упрощения и повышения точности, выхоц второго интег» ратора соецинен с неинвертируюцщм вхопом первого интегратора.

5 920758 б

2. Устройство по п. 1, о т л и ч а ю- дом интегратора и неинвертирую дим Вхо» ш е е с я тем, что, первый интегратор дом операционного усилителя включены выполнен на операционном усилителе, соответствующие масштабируквпие резисмежду инвертируюшим входом и выходом торы, причем выход операционного усипикоторого включен первый интегрируюший g теля является выходом интегратора. конденсатор, между неинвертируюшим Источники информации, входом операционного усилителя и шиной принятые во внимание при зкспертиэе нулевого потенциала включен второй ин- 1. Авторское свидетельство СССР тегрируюший конденсатор, между инвер- . N 316098, кn." G 06 5 7/18, 1970. тируюшими входами интегратора и инвер о 2, Авторское,свидетел ьство СССР тируюшим входом операционного усилите- М 577540, кл. G 06.С 7/18, 1976 ля, а также между неинвертируюшим вхо- (прототип), Составитель Г. Осипов

Редактор Л. Веселовская Техред С.Мигунова Корректор М. Демчик

Заказ 2346/58 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент > г, Ужгород, ул. Проектная, 4