Устройство для контроля системы передачи дискретных сигналов

Иллюстрации

Показать всеРеферат

ЬП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

Союз Советсиик

Социалистичесиии

Реслублии («>920813

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. саид-ву 1т" 830490 (22) Заявлено 050580 (21) 2920464/18-24 (51)М. Кл. с присоединение1и заявки ¹

G 08 С 25/ОО

3Ъаударотееакый комитет

СССР пю делам изобретений и открытий (23 )11риоритет. Опубликовано 1504.82. Бюллетени №14

Дата опубликования описания 1504р2 (53) У%К 621.398 (088. 8) (72j Авторы изобретения

А.С. Горбенко и В.И. Николаев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СИСТЕМЫ

ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ

Изобречение относится к вычислич ельной ч ехнике и передаче информации и может бьчь использовано для отыскания места отказов в линиях связи между цифровыми вычислительны-.

5 ми устройствами.

Ilo основному авч .св. У 830490 извесчно устройсч во для контроля сис" чемы передачи дискречных сигналов, кочорое содержич передающий цифровой

l0 вычисличельный блок, первые выходы

Kol oporto соединены со входами первых усилич елей и -канальной линии свя.зи, выходы последних усиличелей которой соединены с первыми входами приемного цифрового вычислительного блока, регисчр сдвига, первые входы ячеек кочорого объединены и соединены со вчорым входом приемного цифрово-. го вычисличельного блока, выход каждой предыдущей ячейки регистра сдвига соединен со входом последующей ячейки, выход последней ячейки регистраа сдвига соединен с третьим Вхо дом приемного цифрового вычислительного блока, выход приемного цифрового вычислительного блока соединен со входом передающего цифрового вычис" личельного блока, элеменчы неравнозначносчи и элеменчы ИЛИ, первый и второй входы каждого элеменча неравнозначносчи соединены сооч ветсчвенно со входом и выходом соответствующего усилителя, выход - с тречьим входом соответствующей ячейки регистра сдвига и с первым входом соотвечствующего элемента ИЛИ, вчорой вход кочорого соединен с выходом предыдущего усилителя, а выходсо входом последующего усилителя (I).

Недостач ком эчого устройства являечся чо, ччо оно не позволяет определичь момент появления отказа, а лишь фиксирует факч нарушения рабоч о способно ст и сист емы через некото. рое время. Кроме того, для выявления,неисправных элементов необходимо обязачельно переходичь к режиму

920813

3 конч роля независимо от количества отказов.

Цель изобретения - повышение точности и оперативности кончроля за счет возможности определения момента возникновения отказа и места: однократного отказа без перехода в режим контроля.

Посчавленная цель достигается чем, что в усТройство для контроля системы передачи дискретных сигналов введен многовходовый элемент

ИЛИ, выход которого соединен с четвертым входом приемного цифрового вычислительного блока, выходы всех, кроме последней, ячеек регистра сдвига соединены с соответствующими входами многовходового элемента ИЛИ.

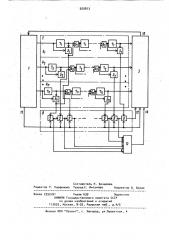

На чертеже предсчавлена структурная схема предлагаемого устройства.

Устройство содержит передающий ,цифровой вычислительный блок 1, иканальную линию 2 связи, приемный цифровой вычислительный блок 3. Каждый канал 4„-4„ содержит элементы неравнозначносчи (сумматоры по модулю 2} 5„ -5„, элементы ИЛИ бч-6 и усилители 7„- 7„.

Устройство также содержит регистр

8 сдвига с ячейками 9, управляющую шину 10, шины -11 и 12 импульсов сдвига, многовходовый элемент ИЛИ 13 и шину 14 контроля.

Устройство работает следующим обра зом.

Данные от передающего цифрового вычислительного блока 1 по многока" нальной линии 2 связи поступают в приемный цифровой вычислительный блок 3. При этом постоянно контроли" руется работоспособность усилителей

7 путем сравнения значений сигналов на входе и на выходе с помощью weментов неравнозначности 5. При от" сутсч вии нарушений в работе линий 2 связи на выходе элементов 5 - -низкий уровень. В случае нарушения работоспособности усилителя 7 на выходе элемента неравнозначности 5 появля" ечся сигнал высокого уровня, который обеспечит запись "1" в соответствую"i щую ячейку 9 регистра 8 сдвига. Импульсы сдвига на регистр 8 по шине

11 поступаюч с частотой выдачи дан" ных постоянно, поэтому !" при подаче первого же импульса сдвига поступает на вход элемента ИЛИ 13 и переписываечся в соседнюю ячейку 9 региS

1е

2S

ЭЗ

4е фф

4 стра сдвига 8. С выхода элемента

ИЛИ 13 единичный сигнал поступает по шине 14 на вход приемного цифрового вычислительного блока 3 и обеспечивавает фиксацию момента появления очказа в ликии 2. Единица, записанная в соседнюю ячейку регистра 8 сдвига, под воздействием импульсов сдвига продвигается по регистру 8 и зачем по шине 12 поступаеч в приемный вычислительный блок 3 через время, определяемое количеством импульсов сдвига, необходимым для выдачи "!" на выход регистра 8. Таким образом, фиксируя момент возникновения очказа по сигналу, поступившему с элеменч а

ИЛИ 13 по шине 14, и определив количество тактов, необходимое дпя сдвига "1" не выход регистра 8, можно однозначно установить номер ячейки 9 регистра 8 сдвига, определить очказавший усилитель 7, не переводя устройство в режим контроля.

Например, если в канале 4„ отказал последний усилитель 7, то с выхода соответствующего ему элемента неравнозмечности 5 единичный сигнал поступает на n -o справа ячейку 9 регистра сдвига 8. При поступлении импульса сдвига по шине 11 "1" поступаеч через элемент ИЛИ 13 по шине !4 на вход блока 3 и, кроме того, сдвигается в соседнюю ячейку регистра 8. Начиная с с этого момента в блоке 3 производится подсчет импульсов сдвига до момента появления. !" на шине 12. В данном случае она появляется на входе блока 3 после подачи еще (n -1) импульса сдвига. Следовательно, первоначально единица была записана в чу ячейку 9 регистра сдвига 8, для сдвига "1" из которой на выход регистра потребовалось (и -1) импульсов сдвига, т.е. в и -ю справа ячейку. А этой ячейке однозначно соответствует последний усиличель 7 4„ канала.

Для обнаружения нескольких, одновременно возникших, отказов следует перейти к режиму контроля, поскольку в худшем случае от элемента неравнозначности 5, подключенного к неисправному усилителю 7 (в примере эчо последней усилитель 4„ канала), в каждом такте передачи данных поступает высокий уровень в соответствующую ячейку 9 регистра 8 сдвига, ччо делает возможным выявление других, одновременно отказавших, усилите 01-1 — 10-0 10-1

-м — г

П 2

Скобками выделены разряды комби" нации, указывающие на состояние

5 9208

В режим контроля, если это. необходимо, т.е. велика вероятность нескольких одновременных отказов, устрой" ство переходит по управляющему сигналу, подаваемому в блок 1 по шине 10, после прихода в блок 3 первой же еди" ницы по шине 12.

В режиме контроля определяются места отказов. В исходном состоянии все ячейки 9 регистра 8 сдвига об" 10 нулены. Для отыскания отказов, нап.ример, наиболее часто встречающихся типа "Устойчивый 0", блок 1 посылает в линию 2 связи комбинацию 11-11.

Элементы 5, подключенные к отказав- 15 шим усилителям 7, формируют единичные сигналы, которые заносят и1" в соответствующиее ячейки 9 регистра 8 : сдвига.

I затем блок 1 выдает серию импуль- 20 сов сдвига по шине 11, обеспечивающих последовательную передачу содер" . жимого всех ячеек 9 регистра S сдвига по шине 12 в блок 3 для ана- лиза. 25

Предположим, что в первом канале

41 отказали первые два усилителя 7, во втором — последний усилитель, а в последнем канале 4 - первый и последний усилители. Тогда в блок 3 50 за период контроля последовательно поступит по шине 12 следующая комбинация сигналов:

13 6 одноименных усилителей 7 всех и каналов. В записи опущены разряды, значения которых равны "0".

Такий образом, предлагаемое устройство по сравнению с известным позволяет не только обнаружить фактнарушения работоспособности, но и зафиксировать момент нарушения, т.е. момент начала приема искаженной информации, что повышает точность, контроля. Кроме того, предлагаемое устройство позволяет определить неисправностный элемент при однократном-. отказе без прохода в режим контроля,. что повышает оперативность контроля.

Формула изобретения

Устройство для контроля системы передачи дискретных сигналов по ввт.св. h" 830490, о т л и ч а ющ.е е с я тем, что, с целью повышения точности и оперативности контроля, в устройство введен многовходовый элемент ИЛИ, выход которого соединен с четвертым входом приемного цифрового вычислительного блока, выходы всех, кроме последней, ячеек регистра сдвига соединены с соот ветствующими входами многовходового элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

tt 830490, кл. G 08 С 25/00, 1979 (прототип).

92Q813

Составитель Н. Бочарова

Редактор Т. Парфенова Техред С. Мигунова Корректор О. Билак

Заказ 2352/61 Тираж 639 Подписное

ЗНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r. Ужгород, ул.Проектная,