Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И306РЕТЕH ÈЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1920843

Союз Советских

Социалистических

Республик (61) Дополнительное к авт.. свид-ву .— (22) Заявлено 04.07.80 (21) 2950667/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

G 11 С 27/00

Гееудеретеелнмл кемлтет

СССР

Опубликовано 15.04.82. Бюллетень № 14

Дата опубликования описания 25.04.82 (53) УДК 681.327.. 66 (088.8) ло аелам нзебретеннй н аткрмтий (72) Авторы изобретения

В. М. Гавриков и В. М. Телеш v с" Ф1 (71) Заявитель

Ф (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобретение относится и автоматике и вычислительной технике, в частности к аналоговым запоминающим устройствам, и может быть использовано в вычислителях с . временным разделением обработки информации. 5

Известно аналоговое запоминающее устройство, содержащее входной операционный усилитель, накопительный элемент, например конденсатор, делитель напряжения, выходной операционный усилитель, выход которого через элемент обратной связи соединен с инвертирующим входом входного операционного усилителя, буферный каскад, вход которого соединен с одной из обкладок конденсатора и через ключ с делителем на. пряжения (1). 15

Недостатком данного устройства является наличие динамической ошибки при переходе из режима выборки в режим хранения, а также сложность схемного выполнения, .

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, которое содержит входной и выходной операционные усилители, охваченные через первый пассивный элемент, например резистор, отрицательной

2 обратной связью, накопительный элемент, например конденсатор, обкладки которого соединены с шиной нулевого потенциала с неинвертирующим входом выходного усилителя, шунтирующий выход входного усилителя, первый ключ, второй ключ, соединенный с выходом входного усилителя и шину управления (2).

Однако это запоминающее устройство имеет две существенные динамические ошибки, появляющиеся в устройстве при переходе его с этапа выборки на этап хранения.

Первая из них обусловлена наличием разрядного тока конденсатора через паразитные емкость затвор-исток второго ключа от перепада управляющего напряжения U упр, и емкость сток-исток этого же ключа от перепада напряжения на выходе входного усилителя при работе его от аналогового коммутатора. Вторая ошибка обусловлена наличием высокочастотной генерации контура в режиме выборки, Цель изобретения — повышение точности аналогового запоминающего устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый накопительный элемент, 920843

Формула изобретения

3 например первый конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, входной операционный усилитель, инвертирующий вход которого соединен с выходом первого ключа, выходной операционный усилитель, охваченный по инвертирующему входу отрицательной обратной связью, другая обкладка первого конденсатора соединена с неинвертирующим входом выходного операционного усилителя, выход которого подключен к выходу устройства и через первый пассивный элемент, например первый резистор, к инвертирующему входу входного операционного усилителя, выход которого соединен с информационными входами первого и второго ключей, шину управления, соединенную с управляющим входом второго ключа, введены второй накопительный элемент, например второй конденсатор, инвертор, второй и третий пассивные элементы, например резисторы, и третий ключ, информационный вход которого соединен с входом устройства, управляющий вход третьего ключа соединен с шиной управления и входом инвертора, выход которого соединен с управляющим входом первого ключа, выход третьего ключа соединен с неинвентирующим входом входного операционного усилителя и через второй резистор с выходом выходного операционного усилителя, выход второго ключа соединен через третий резистор с другой обкладкой первого конденсатора, выход входного операционного усилителя подключен к одной из об- З0 кладок второго конденсатора, другая обкладка которого соединена с инвертирующим входом входного операционного усилителя.

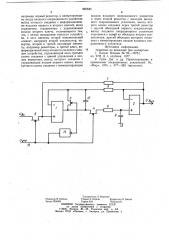

На чертеже изображена функциональная схема предложенного устройства.

Оно содержит входной и выходной операционные усилители 1 и 2, ключи 3 — 5, пассивные элементы, например резисторы 6 — 8, накопительные элементы, например конденсаторы 9 и 10, инвертор 11, шину 12 управления и шину 13 нулевого потенциала. 40

Предлагаемое устройство функционирует сле;,ующим образом.

При наличии управляющего импульса на мряжения Uypp на шине 12 управления (этап выборки) ключи 5 и 4 замкнуты, а ключ 3 разомкнут. Конденсатор 9 через сопротив45 ление ключа 4 и резистора 8 заряжается до величины напряжения, равной величине входного напряжения Uz, так как усилители 1 и

2 включены по схеме общего повторителя, и имеет собственный коэффициент усиления, 50 т.е. в установившемся режиме напряжения на неинвертирующем входе усилителя 1 и выходе усилителя 2, а также на инвертирующем входе усилителя 1 практически равны входному напряжению 11вх . Падение напряжения на ключе 5 мало, так как его сопротивление в замкнутом состоянии составляет сотни Ом, а входное сопротивление усилителя 1 составляет не менее тысячи МОм.

При переходе аналогового запоминающего устройства в режим хранения ключи 5 и 4 размыкаются, а ключ 3 замыкается. Задний фронт управляющего импульса дифференцируется паразитной .емкостью затвористок и в виде узкого импульса поступает на вход фильтра образованного резистором

8 и конденсатором 9, которым он подавляется практически до нуля. При отсутствии резистора 8 продифференцированный перепад заднего фронта управляющего импульса вносит приращение напряжения к величине напряжения, имевшейся до момента перехода устройства в режим хранения. Это приращение является одной из двух составляющих первой динамической ошибки, проявляющейся в известном устройстве. Постоянная времени (= R С, (где Кв — сопротивление резистора 6, а С, — емкость конденсатора 10) фильтра выбирается из условия обеспечения максимального быстродействия запоминающего устройства и допустимой величины динамической погрешности, обусловленной действием цепи управления ключа 3. После размыкания ключа 3 обеспечивается эквипотенциальность входов и выхода усилителя 1, причем уровень напряжений на его входах и выходе равны выходному напряжению устройства U»i>, которое практически в режйме хранения остается постоянным, так как разряд конденсатора обуславливается малыми токами утечки цепей затвор-исток ключа

4 и входного сопротивления усилителя 2.

Введение ключа 5 и резистора 7 обеспечивает значительное снижение уровня напряжения перепада на выходе входного усилителя 1 (практически до нуля) при переходе устройства в режим хранения, а резистор 8 с конденсатором 9 образуют фильтр, подавляющий узкие выбросы (пики) напряжения от действия заднего фронта управляющего напряжения при переходе устройства так же в режим хранения. Конденсатор

I0 срывает высокочастотную генерацию контура в режиме выборки, а введение логичес кого инвертора 11 упрощает входную цепь управления запоминающим устройствам.

Аналоговое запоминающее устройство, содержащее первый накопительный элеМент, например первый конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, входной операционный усилитель, инвертирующий вход которого соединен с выходом первого ключа, выходной операционный усилитель, охваченный по инвертируюшему входу отрицательной обратной связью, другая обкладка первого конденсатора соединена с неинвертирующим входом выходного операционного усилителя, выход которого подключен к выходу устройства и через первый пассивный элемент, 920843 Составитель А. Воронин

Редактор В. Бобков Tex ред А. Бо и к а с Корректор О. Билак

Заказ 2356 62 Тираж 524 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

5 например первый резистор, к инвертирующему входу входного операционного усилителя, выход которого соединен с информационными входами первого и второго ключей, шину управления, соединенную с управляющим входом второго ключа, отличающееся тем, что, с целью повышения точности устройст-. ва, в него введены второй накопительный элемент, например второй конденсатор, инвертор, второй и третий пассивные элементы, например резисторы, и третий ключ, информационный вход которого соединен с вхо- 10 дом устройства,- управляющий вход третьего ключа соединен с шиной управления и входом инвертора,,выход которого соединен с управляющим входом первого ключа, выход третьего ключа соединен с неинвертирующим входом входного операционного усилителя и через второй резистор с выходом выходного операционного усилителя, выход второго ключа соединен через третий резистор с другой обкладкой первого конденсатора, выход входного операционного усилителя подключен к одной из обкладок второго конденсатора, другая обкладка которого соединена с инвертирующим входом входного операционного усилителя.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 52 — 19751, кл. 97/8 Д 1, опублик. 1977.

2. Грэм Дж. и др. Проектирование и применение операционных усилителей. М., «Мир», 1974, с. 377 — 382 (прототип).