Устройство для контроля блоков долговременной памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >920846

Союз Советских

Социалистических

Республик. (61) Дополнительное к авт.,свид-ву— (22) Заявлено 02.07.80 (21) 2949886/18-24 с присоединением заявки №вЂ” (51) М.К .

G 11 С 29/00

Гвеударствеллнй квнлтет (23) Приоритет—

Опубликовано 15.04.82. Бюллетень № 14

Дата опубликования описания 25.04.82 (53) УДК 681.327..6 (088.8 ) ио делан лэвбретений и вткрнтий

Г. А. Бородин, Н. И. Егорова и А. К. (толяросв1 р е ре

1 " ! е -:, Московскнй ордена Ленина н ордена Окйнб ьс коей.:,о„: „ г

Революции . энергетический институт (72) Авторы . изобретения (71) Заявитель (54) УСТРОИСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ДОЛГОВРЕМЕННОЛ ПАМЯТИ

Изобретение относится к вычислительной технике, а именно к контролю долговременных запоминающих устройств.

Известно устройство для контроля, содержащее сумматор, блок задания циклов суммирования, блок установки контрольных чисел и блок управления. Проверяемый блок постоянной памяти кроме контролируемых чисел дополнительно хранит контрольные константы, с помощью которых осуществляется контроль (1).

)о

Недостатком известного устройства является необходимость хранения большого количества контрольных чисел, что уменьшает полезный объем памяти.

Наиболее близким к предлагаемому по 1s технической сущности является устройство для контроля блоков постоянной памяти, содержащее сумматор, формирователь контрольных разрядов по модулю, коммутатор, регистр сравнения, узел установки контрольных чисел, блок управления и блок за- дания циклов суммирования. Устройство осуществляет контроль блока долговременной памяти по методу контрольного суммирования (2).

Недостатком известного устройства является излишняя сложность устройства, в част ности сумматора.

Цель изобретения — упрощение устройства контроля.

Поставленная цель достигается тем, что в устройстве для контроля блоков долговременной памяти, содержащем блок задания циклов суммирования, выход которого подключен к одному управляющему входу коммутатора, а вход — к первому выходу бло-. ка управления, выходы коммутатора подключены к одним входам блока сравнения, другие входы которого подключены к выходам блока установки контрольных чисел, управляющий вход блока установки контрольных чисел подключен к второму выходу блока управления, управляющие вход и выход блока сравнения подключены соответственно к третьему выходу и к входу блока управления, второй управляющий вход коммутатора подключен к четвертому выходу блока управления, сумматор и формирователь сигналов контрольных разрядов, выходы сумматора подключены к входам коммутатора, управляющий вход сумматора подключен к пятому выходу блока управления, t

920846 а входы сумматора подключены к выходам формирователя сигналов контрольных разрядов, входы которого являются входами устройства, управляющий вход формирователя сигналов контрольных разрядов подключен к шестому выходу блока управления.

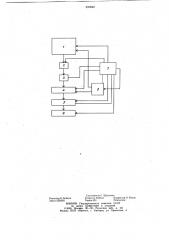

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит подключенный к вы ходам блока 1 долговременной памяти формирователь сигналов контрольных разрядов

2, сумматор 3, коммутатор 4, блок 5 сравнения, блок 6 установки контрольных чисел, блок 7 управления и блок 8 задания циклов суммирования.

Устройство работает следующим образом. 15

При подаче на вход блока 1 долговременной памяти кода адреса импульса запроса из блока 7 управления и сигнала из блока

8 задания циклов суммирования из блока 1 долговременной памяти считываются числа . и посылаются в формирователь сигналов контрольных разрядов 2, в котором производится определение вычета каждого считанного числа, далее производится сложение вычетов в сумматоре 3. После того, как все числа, подлежащие суммированию в очередном цикле, отработаны, в сумматоре 3 хранится сумма вычетов всех считанных в этом цикле чисел. По сигналам управления, поступающим из блока 7 управления и блока

8 задания циклов суммирования, через коммутатор 4 производится запись контрольных разрядов вычета в соответствующие разряды блока 5 сравнения. Сумматор 3 после этого обнуляется. Начинается следующий цикл суммирования. После заполнения всех разрядов блока 5 сравнения в нем производится сравнение полученного кода с контрольным числом, поступающим из блока 6 установки контрольных чисел по команде из

1 блока 7 управления.

Результат операции сравнения направляется в блок 7 управления. 4О

Применение предлагаемого устройства позволяет реализовать поставленную задачу контроля, используя сумматор значительно меньшей разрядности, чем в известном. А именно, если используется формирование

4 контрольных разрядов по модулю.А, то количество контрольных разрядов К будет равно К= log (A+1), при А =7, К =3. В известном устройстве К = M, где М вЂ” разрядность слов в блоке памяти. Обычно М= 16, 32 и т.д. При этом известно, что поскольку контроль по вычетам используется для контроля арифметических операций, то возникающие ошибки обнаруживают вычетом и точность контроля не ухудшается.

Формула изобретения

Устройство для контроля блоков долговременной памяти, содержащее блок задания циклов суммирования, выход которого подключен к одному управляющему входу коммутатора, а вход — к первому выходу блока управления, выходы коммутатора подключены к одним входам блока сравнения, другие входы которого подключены к выходам блока установки контрольных чисел, управляющий вход блока установки контрольных чисел подключен к второму выходу блока управления, управляющие входы и выход блока сравнения подключены соответственно к третьеМу выходу и к входу блока управления, второй управляющий вход коммутатора подключен к четвертому выходу блока управления, сумматор и формирователь сигналов контрольных разрядов, отличаюи!ееся тем, что, с целью упрощения устройства, выходы сумматора подключены к входам коммутатора, управляющий вход сумматора подключен к пятому выходу блока управления, а входы сумматора подключены к выходам формирователя сигналов контрольных разрядов, входы которого являются входами устройства, управляющий вход формирователя сигналов контрольных разрядов подключен к шестому выходу блока управления.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР

Мо 135105, кл. G 11 С 29/00, !975.

2. Авторское свидетельство СССР по заявке № 2794982/18 — 24, кл. G 11 С 29/00, 1979 (прототип).

920846

Составитель С. Шустенко

Редактор В. Бобков Техред А. Бойкас Корректор О. Билак

Заказ 2356 62 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, ж — 35, Раушская наб., д. 4/5 филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4