Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (920848

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дойолнительное к авт., свид-ву,— (22) Заявлено 16.07.80 (21) 2961639/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

G 11 С 29/00

Государственный комитет .

СССР

Опубликовано 15.04.82. Бюллетень №14

Дата опубликования описания 25.04.82 (53) УДК 681,327 (088.8 ) по делам изобретений. и еткрмтий

)

В. П. Андреев, А. И. Беляков, A. Н. Пресняков

1 (72),Авторы изобретения и.А. Н. Иванов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминаюшим устройствам.

Известно запоминающее устройство с са-, моконтролем в котором используется временная избыточность для исправления обнаруженных ошибок (1). 5

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому техническим решением является запоминающее устройство с самоконтролем, содержащее регистр адреса, накопитель, регистр числа, блок обнаружения и коррекции ошибок и блок управления 12).

Недостатком этого устройства является низкая надежность вследствие отсутствия автоматической регулировки длительности цикла обращения к устройству .в зависимости от частоты возникающих ошибок. ю

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается,тем, что в запоминающее устройство с самоконтролем, содержашее накопитель, регистр числа, регистр адреса, блок коррекции и блок управления, причем выходы регистра адреса подключены к адресным входам накопителя, информационные входы и выходы которого соединены с одними из выходов и входов блока коррекции, другие выходы и входы которого подключены к одним из входов. и выходов регистра числа, управляющие входы накопителя, регистра числа, блока коррекции и регистра адреса соединены соответственно с выходами блока управления, первый и второй входы которого являются соответственно входом разрешения записи и входом режима записи устройства, входы регистра адреса и другие входы и выходы регистра числа являются ссютветственно адресными и информационными входами и выходами устройства, введены блок анализа частоты ошибок, вход которого подключен к управляюшему выходу блока коррекции, а выходы — к третьему входу блока управления.

При этом блок анализа частоты ошибок целесообразно выполнить содержащим счетчик, формирователь сигналов временной диаграммы, элементы ИЛИ, элемент И вЂ” НЕ и элементы И, причем установочный вход формирователя сигналов временной диаграммы подключен к выходу первого элемента ИЛИ, 920848

3 первый вход которого соединен с первым входом первого элемента И, второй вход которого подключен к выходу элемента И вЂ” НЕ, выход формирователя сигналов временной диаграммы соединен со вторым входом первого элемента ИЛИ и первым входом второго элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, выходы элементов И соединены соответственно со .т входами «Сложение» и «Вычитание» счетчика, выходы которого подключены ко входам второго элемента ИЛИ и элемента И—

НЕ и являются выходами блока, а первый вход первого элемента ИЛИ является входом блока.

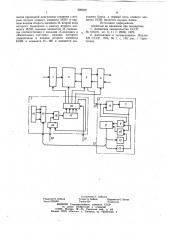

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит регистр Т адреса, накопитель 2, блок 3 коррекции, регистр 4 числа, блок 5 управления и блок 6 анализа частоты ошибок. Блок 6 анализа частоты ошибок выполнен содержащим формирователь сигналов временной диаграммы 7, счетчик 8 реверсивного типа, первый 9 и второй

10 элементы И, первый 11 и второй 12 элементы ИЛИ и элемент И вЂ” НЕ 13. Блок 5 управления содержит формирователь 14 синхросигналов, коммутатор 15, триггер 16, счетчик 17, элемент И 18 и формирователь 19 управляющих сигналов. Кроме того, устройство содержит вход 20 разрешения записи и вход 21 режима записи устройства, а также выходы 22 и вход 23 блока анализа частоты ошибок и формирования управляющих сигналов.

Устройство работает следующим образом.

В режиме записи на адресные входы устройсгва поступает код адреса ячейки памяти накопителя 2, на информационные входы устройства = код записываемого числа, а на вход 21 — сигнал, соответствующий режиму записи. По сигналу «Пуск», поступающему на вход 20 устройства, блок 5 формирует последовательность управляющих сигналов в соответствии с временной диаграммой записи. При этом происходит запись кода адреса в регистр 1 адреса, с выхода которого код адреса поступает на адресные входы накопителя 2. Код числа записывается в регистр 4 и с его выхода поступает на вход блока 3 коррекции, который осуществляет кодирование информации в соответствии с выбранным избыточным кодом. Избыточный код числа с выхода блка 3 поступает на информационные входы накопителя 2, в выбранную ячейку памяти которого производится запись.

Формирование управляющих сигналов блоком 5 в соответствии с временной диаграммой режима работы устройства производится следующим образом.

С выходов формирователя 14 синхросигналов, сигналы различной частоты поступают на информационные входы коммутато4 ра 15, на управляющий вход которого подается код управления с выходов 22 блока 6.

В начальном состоянии на вход управления коммутатора 15 подается нулевой код управления. При этом на выход коммутатора

5 15 поступают синхросигналы максимальной частоты с первого выхода формирователя 14.

Сигналом «Пуск», поступающим со входа

20 устройства на вход установки «1 » триггера 16, производится запись в него единичной информации, Разрешающий потенциал с единичного выхода триггера 16 подается на второй вход элемента И 18, разрешая прохождение синхросигналов с выхода коммутатора 15 на вход счетчика 17. Счетчик 17 производит деление частоты F поступающих на его вход синхросигналов. Сигналы частоты —ä,,--,Г- и т.д. подаются с выходов счетг чика 17 на первые входы формирователя 19, на второй вход которого поступает сигнал со входа 21 устройства. На выходах формирователя 19 формируются управляющие сигналы в соответствии с временной диаграммой цикла работы. По окончании цикла работы со второго выхода формирователя 19 на вход установки «О» триггера 16 поступает сигнал

«Конец цикла» и устанавливает его в начальное состояние. При этом на второй вход элемента И 18 подается потенциал с единичного выхода триггера 16, запрещающий прохождение синхросигналов на вход счетчика

17. На этом цикл работы устройства заканчивается. зо Блок 5 управления позволяет изменять временную диаграмму цикла работы устройства, поскольку при изменении управляющего кода, поступающего с выходов 22 блока

6 на управляющий вход иоммутатора 15, например, на единицу, на вход счетчика 17 поступают синхросигналы более низкой частоты со второго выхода формирователя 14,.что приводит к увеличению времени цикла работы устройства и т.д.

В режиме считывания код адреса записы40 вается в регистр 1 адреса и с его выходов поступает на адресные входы накопителя 2, из выбранной ячейки памяти которого производится считывание информации. Считанный избыточный код числа поступает на

4 вход блока 3, где производится его декодирование и исправление обнаруженных ошибок. Далее с выхода блока 3 код числа поступает на вход регистра 4, записывается в него и выдается на информационные выходы устройства.

so Факт обнаружения ошибки в считанной информации фиксируется в блоке 6, на вход 23 которого в этом случае поступает сигнал с соответствующего выхода блока 3.

Блок 6 в зависимости от частоты возникаю55 щих ошибок, т.е. в зависимости от уменьшения времени наработки на ошибку по сравнению с допустимым, формирует код управления, который с выходов 22 блока 6 поступает на вход блока 5 и задает временную диа920848

1о

IS го

Формула изобретения г5 зо

55 грамму цикла работы устройства. Причем при повышении частоты ошибок происходит автоматическое .увеличейие времени цикла работы устройства, а при снижении частоты ошибок (т.е. при увеличении времени наработки на ошибку по сравнению с допустимым) — уменьшение.

Рассмотрим более подробно работу блока

6 анализа частоты ошибок.

В исходном состоянии нулевой,код управления с выхода счетчика 8 поступает на вход элемента И вЂ” НЕ 13, разрешающий потенциал с выхода которого поступает на второй вход первого элемента И 9. При обнаружении ошибки сигнал со входа 23 блока 6 через элемент И 9 поступает на вход «Сложение» счетчика 8 и увеличивает его содержимое на единицу, что приводит к увеличению времени цикла работы устройства. Сигнал со входа 23 блока 6 через элемент ИЛИ

11 поступает также на установочный вход формирователя 7, который предназначен для задания допустимого времени наработки на ошибку. С момента поступления этого сигнала через заданное допустимое время с выхода формирователя 7 на вход «Вычитание» счетчика 8 поступает сигнал, который на единицу уменьшает его содержимое, что приводит к уменьшению времени цикла работы устройства.. Сигнал с выхода формирователя 7 через элемент ИЛИ 11 поступает также на его установочный вход, задавая новый цикл отсчета времени.

В случае отсутствия ошибок в каждом цикле отсчета времени происходит уменьшение на единицу содержимого счетчика 8, что приводит к последовательному уменьшению цикла работы устройства.

В случае обнаружения ошибки в каждом цикле отсчета времени формирователем 7 происходит увеличение содержимого счетчика 8. Это приводит к последовательному увеличению времени цикла работы устройства.

В случае последовательного поступления сигналов на вход «Сложение» и на вход «Вычитание» счетчик 8 находится в динамичес.ком равновесии. При этом код управления, а следовательно, и задаваемый им цикл работы устройства колеблется около своего oIIтимального значения.

В случае отсутствия ошибок на выходе счетчика 8 через некоторое время устанавливается нулевое значение кода управления.

При поступлении на его вход «Вычитание» еще одного сигнала с выхода формирователя 7 значение кода управления изменяется на единичное, что приводит к максимальному увеличению времени цикла работы устройства. Во избежание этого при нулевом коде управления потенциал с выхода элемента

ИЛИ 12 поступает на второй вход второго элемента И 10 и запрещает прохождение сигнала с выхода формирователя 7 на вход счетчика 8.

6 !

В случае обнаружения в каждом цикле отсчета времени более одной ошибки на выходе счетчика 8 через некоторое время устанавливается единичное значение кода управления. При поступлении еще одного сигнала обнаружения ошибки на выходе счетчика 8 устанавливается нулевое значение кода управления, что приводит к максимальном уменьшению цикла работы устройства, а следовательно, и к появлению новых ошибок.

Во избежание этого при единичном коде управления потенциал с выхода элемента И—

НЕ 13 поступает на второй вход элемента И

9 и запрещает прохождение сигнала обнаружения ошибки со входа 23 блока 6 на вход «Сложение» счетчика 8.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает автоматическую регулировку длительности циклов работы устройства в различных режимах в зависимости от частоты возникновения ошибок, за счет чего повышается его надежность по сравнению с известным.

1. Запоминающее устройство с самоконтролем, содержащее накопитель, регистр числа, регистр адреса, блок коррекции и блок управления, причем выходы регистра адреса подключены к адресным входам накопителя, информационные входы и выходы которого соединены с одними из выходов и входов блока коррекции, другие выходы и входы которого. подключены к одним из входов и выходов регистра числа, управляющие входы накопителя, регистра числа, блока коррекции и регистра адреса соединены соответственно с выходами блока управления, первый и второй входы которого являются соответственно входом разрешения записи и входом режима записи устройства, входы регистра адреса и другие входы и выходы регистра числа являются соответственно адресными и информационными входами и вы-. ходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок анализа частоты ошибок, вход которого подключен к управляющему выходу блока коррекции, а выходы — к третьему входу блока управления.

2. Устройство по п. 1, отличающееся тем, что блок анализа частоты ошибок содержит счетчик, формирователь сигналов временной диаграммы, элементы ИЛИ, элемент И вЂ” НЕ и элементы И, причем установочный вход формирователя сигналов временной диаграммы подключен к выходу первого элемента ИЛИ, первый вход которого соединен с первым входом первого элемента И, и второй вход которого подключен к выходу элемента И вЂ” НЕ, выход формирователя сиг920848

Составитель Т. Зайцева

Редактор В. Бобков Техред А. Бойкас Корректор О. Билак

Заказ 2356 62 Тираж 524 Подписное

ВНИИПИ Гоеударственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, . Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4 налов временной диаграммы соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, выходы элементов И соединены соответственно с входами «Сложение» и

«Вычитание» счетчика, выходы которого подключены к входам второго элемента

ИЛИ и элемента И вЂ” НЕ и являются вы8 ходами блока, а первый вход первого элемента ИЛИ является входом блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 516101, кЛ. G 11 С 29/00,,1976.

2. Автоматика и телемеханика». Изд-во

АН СССР, 1974, № ., с, 155. рис. 1 (прототип).