Триггер на кмоп транзисторах

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик

921052 (61) Дополнительное к авт. свид-ву (22) Заявлено 110780 (21) 2958446/18-21 (И)М Кл з с присоединением заявки ¹â€”

Н 03 К 3/286 (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 150482. Бюллетень №14

Дата опубликования описания 150482 ($3)УДК 621.374 (088. 8) Г.Д. Беляев, Б.А. Баградов, Ю.Н. Смирнов и И.Г. Фильцер (72) Авторы изобретения (71) Заявитель (54) ТРИГГЕР НА КМОП ТРАНЗИСТОРАХ

Изобретение относится к импульсной технике и может быть использовано в цифровой аппаратуре, в частности в цифровых интегральных Схемах,к которым предъявляются требования установки триггеров и триггерных устройств в определенное исходное со-стояние в процессе нарастания напряжения питания.

Известны триггерные устройства, состоящие иэ двух интервалов с перекрестными связями, каждый из кото- рых содержит два последовательно вклю. ченных комплементарных МОП транзистора, затворы которых образуют вход 15 инвертора, а стоки — выход (1).

Недостаток известных устройств заключается в отсутствии начальной установки в определенное состояние.

Известен триггер на КМОП транзисторах, состоящий иэ двух инверторов с перекрестными связями, для установки которого в определенное исходное состояние на его вход начальной установки поступает импульс сброса, Формируемый устройством начальной установки после установления напряжения питания (2).

Недостатком известного устройства является то, что требуется время на - 30 установку триггера.в определенное исходное состояние после установления напряжения питания.

Цель изобретения — установка триггера в определенное исходное состояние в процессе нарастания напряжения питания °

Для достижения поставленной цели в триггер на KNOII транзисторах, состоящих из двух инверторов с перекрестными связями, введены пять дополнительных МОП транзисторов и дополнительный триггер, состоящий из двух инверторов с перекрестными свя-. зями, каждый из которых содержит. нагрузочный и ключевой МОП транзисторы одного типа проводимости, при этом нагрузочные транзисторы подключены к шине питания через первый дополнительный МОП транзистор того же типа проводимости в диодном включении, а выходы дополнительного триггера подключены, соответственно, к затвору второго и третьего дополнительных

МОП транзисторов того же типа проводимости, истоки которых подключены к общей шине, а стоки — к затвору четвертого дополнительного МОП транзистора того же типа проводимости и через пятый дополнительный МОП

921052 транзистор дополняющего типа проводимости:- к шине питания, исток четвертогo и затвор пятого дополнительных МОП транзисторов подключены к общей шине, а сток четвертого дополнительного МОП транзистора подключен к одному из выходов триггера.

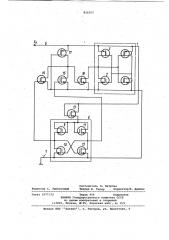

На чертеже представлена электрическая принципиальная схема устройства.

Триггер 1 состоит из двух инвер- 30 торов с перекрестными связями, каждый из которых содержит два комплементарных транзистора 2,3 и 4,5 соответственно, последовательно включенных между шиной питания 6 и общей шиной 7. Дополнительный триггер

8 состоит из двух инверторов с перекрестными связями, каждый иэ которых содержит нагрузочный и ключевой

МОП транзисторы одного типа провоци-мости, 9,10 и соответственно, 11 и

12. При этом затворы и стоки транзисторов 9 и 11 через первый дополнительный МОП транзистор 13 того же типа проводимости в диодном включении подключены к шине 6, а выходы триггера 8 подключены соответственно, к затвору второго и третьего дополнительных МОП транзисторов 14 и 15, того же типа проводимости, истоки которых подключены к шине 7, а стоки к затвору четвертого дополнительного МОП транзистора 16 того же типа проводимости и через пятый дополнительный МОП транзистор 17 дополняющего типа проводимости — к шине 6, 35 исток транзистора 16 и затвор транзистора 17 подключен к шине 7, а сток транзистора 16 — к одному из выходов триггера 1.

Устройство работает следующим об- 40 разом.

В процессе нарастания. напряжения питания вначале открывается транзистор 17 и вследствие этого транзистор

16, при этом низкий потенциал посту- 45 пает на один из выходов триггера 1.

По мере нарастания напряжения нитания триггер 1 обретает свойство иметь два устойчивых состояния и поскольку на один из его выходов поступает низкий потенциал, триггер 1 устанавливается в определенное начальное состояние. При дальнейшем нарастании напряжения питания открывается транзистор 13 и ключевой и нагрузочный транзисторы одного из инверторов триггера 8. При этом потенциал на выходе другого инвертора триггера 8 возрастает вслед эа дальнейшим ростом напряжения питания, что приводит к открыванию того из транзисторов 14 60 или 15, затвор которого подключен к выходу закрытого инвертора триггера 8. Транзисторы 14 и 15 выбираются более мощными, чем транзистор 17, поэтому потенциал в общей точке стоков транзисторов 17,14,15 падает, что приводит к запиранию транзистора 16, это позволяет в дальнейшем триггеру

1 управляться внешними логическими. сигналами.

Изобретение обеспечивает установку в определенное исходное состояние в процессе нарастания напряжения питания как одиночного триггера, 3 так и ряда триггеров. Для этого к каждому. из триггеров должен быть подключен транзистор, аналогично подключению транзистора 16 к триггеру 1,. затвор которого следует подключать к общей точке стоков транзисторов

17,14,15.

Использование триггера на KMOII транзисторах позволяет строить цифровые устройства в интегральном исполнении, способные выполнять свои функции сразу после установления напряжения питания.

Формула изобретения

Триггер на KMOII транзисторах, состоящий из двух инверторов с перекрестными связями, о т л и ч а юшийся тем, что, с целью установки триггера в определенное исходное состояние в процессе нарастания напряжения питания, в него введены пять дополнительных МОП транзисторов и дополнительный триггер, состоящий из двух инверторов с перекрестными связями, каждый из. которых содержит нагрузочный и ключевой NOII транзисторы одного типа проводимости, при этом нагрузочные транзисторы подключены к шине питания через первый дополнительный NOII транзистор того же типа проводимости в диодном включении, а выходы дополнительного триггера подключены, соответственно, к затвору второго и третьего дополнительных МОП транзисторов того же типа проводимости, истоки которых подключены к общей шине, а стокик затвору четвертого дополнительного

ИОП транзистора того же типа проводимости и через пятый дополнительный

МОП транзистор дополняющего типа проводимости — к шине питания, исток четвертого и затвор пятого дополнительных NGO транзисторов подключены к общей шине, а сток четвертого дополнительного ИОП транзистора подключен к одному из выходов триггера. Источники информации, принятые во внимание при,экспертизе

1. Букреев И.Н . и др. Микроэлектронные схемы цифровых устройств N., Советское радио, 1975.

2. Ильин В.Н., Фролкин В.Т. Цифровые схемы и устройства на ИДП транзисторах. M., Энергия, 1975, с. 37.

921052

Составитель Л. Петрова

Техреду М. Тепер Корректор М. Демчик

Редактор С. Запесочный Хираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Заказ 2377/72

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4